Logic BIST is crucial for many applications, in particular for life-critical and mission-critical applications.

Logic BIST不需要在ATE上进行测试,减小了成本,但是电路本身是可能存在问题的,导致测试逻辑有问题而且增加了逻辑。

Basic concepts and design rules of logic BIST

Test pattern generation(exhaustive testing/pseudo-random testing/pseudo-exhaustive testing),

output response analysis(ones count testing/transition count testing/signature analysis)

logic bist architecture STUMPS

For stuck-at faults and bridging faults,how to test faults in a scan-based design containing multiple clock domain

For path-delay and transition delay, how to test

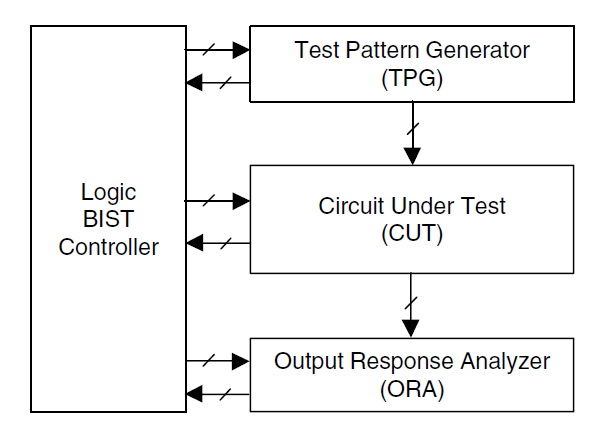

Design a logic bist system:test pattern generator, output response analyzer, logic BIST controller

Traditional test techniques that use ATPG software to target single faults for digital circuit testing have become quite expensive

And can no longer provide sufficiently high fault coverage.

Two general categories of bist techniques:

1) online BIST, is performed when functional circuitry is in normal operational mode

concurrently:test is conducted during normal functional operation, generate interrupt for failures.

nonconcurrently:test is performed during idle mode, test process can be interrupt at any time

2) offline BIST, does not detect any real-time error, but widely used in the industry.

Functional offline BIST:perform a test based on the functional specification, employ a functional or high-level fault model.

Implemented as diagnostic software or firmware.

Structural offline BIST:

external BIST:test pattern generation and output response analysis is separate from the functional circuitry being test

Internal BIST:functional storage elements are converted into test pattern generators and output response analyzers.

ger provide sufficiently high fault coverage.

做BIST设计时,需要BIST-specific design rule,并且BIST fault coverage也不一定比scan design来的高,但是BIST不需要进行test pattern的generation,也不需要huge data volume来存储output response.

BIST DESIGN RULES

While many scan design rules are optional for scan designs, they are mandatory for BIST deisgn.

The major logic BIST design restriction relates to the propagation of unknown X values. No unknown values can be tolerated.

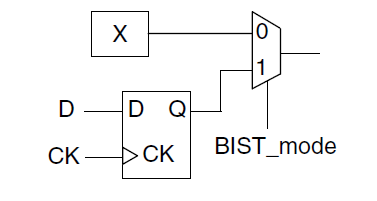

1) Unknown source blocking

Blocked and fixed using a DFT repair approach called X-bounding/X-blocking,0-control point/1-control point/bypass logic/control-only scan point.

2) Memories and Non-Scan Storage Element

通过bypass来block 来自memory和non_scan storage出来的unknown X或者通过initialization sequence初始化storage element。

3) Combinational Feedback Loops

所有的combinational feedback都必须是避免的,通过0-control/1-control/scan point cell.

4) Async set/reset signal

在data shift过程中,可能会使得set/reset signals变得active,所以set/reset在shift operate中必须保证set to 1,推荐使用SE做mux。

5) Tristate Buses

由于pseudo-random pattern在BIST中应用较多,所以为了避免bus conflict,最好每条bus都resynthesize with multiplexers或者通过one-hot decoder来进行编码。

6) False paths

由于false path在normal circuit operation中并不会被exercised,这些path一般也不会符合timing specifications,BIST中可能会有delay fault test,这样就需要加入0-control/1-control point来切断这样的OCC Test.

7) Multiple-Cycle path

类似于false path,需要加入0-control/1-control point来切断这样的OCC Test.

8) Floating Ports

Neither PI nor PO can be floating.

9) Bidirectional I/O ports

BIST operation时,必须fix the direction of each bidirectional I/O port.

10) Re-Timing

由于TPG和ORA距离CUT可能比较远,所以推荐加入FF,来保证timing.

Test pattern generation

在TPG中,LFSR(Linear feedback shift registers)通常被用来产生test pattern,来做exhaustive testing,pseudo-random testing,pseudo-exhaustive testing

1) Exhaustive testing可以保证100%的single-stuck和multiple-stuck fault coverage,但是要求所有可能的2的N次的test pattern.

2) Pseudo-random testing用subset的test pattern来计算fault coverage,不保证100% single-stuck。

3) Pseudo-exhaustive testing,保证100% single stuck-at fault coverage

Standard LFSR

Consists of n D FF and a selected XOR gates.

Modular LFSR

相应的XOR放在两个D FF之间,运行速度比standard更加快一点。

LFSR可以用特征多项式(characteristic polynomial)来进行表示,

Exhaustive Testing

使用2的N次方的exhaustive pattern到一个n-input的CUT中,进行test。包括binary counter为generator计数,maximum-length LFSR进行generator.

Pseudo-Random Testing

Reduce test length but sacrifices the circuit fault coverage.

Pseudo-Exhaustive Testing

Reduce the test time while retaining many of the advantages of exhaustive testing.

Delay Fault Testing

structural faults,像stuck-at faults和bridging faults,可以通过one-pattern vectors来进行detect.

但是对于delay fault,要求two-pattern vectors.目前有技术可以是实现特殊one-transition pattern来实现。

进行at-speed的BIST测试时,power consumption也会有问题,可能会超过chip或者package的承载范围。

Output Response Analysis

对于scan design来说,output reponses compared是在tester上来做的,但是BIST中不会这么处理,

BIST不会将所有的output response都放在on/off chip的memory中。

在BIST中,output reponses会被压缩到一个signature中,并且同golden signature来进行比较。

(名词比较,compaction有损压缩,compression无损压缩)

三种output responses compaction techniques:

1)ones count testing

2)transition count testing

3)signature analysis

对于某些test length比较长的电路,可以通过segment test来进行设计:

1)Hardware partitioning,通过插入multiplexers.

2)Sensitized partitioning,通过appropriate inputpattern到一些input lines来实现circuit partitioning或subcircuit isolation.