Logic BIST通过将很多的tester functionality放在CUT中,减少了test costs,但是更重要的一方面是at-speed testing.

At-speed test包括两部分:

1) intra-clock-domain fault:originates at one clock domain, terminate at the same clock domain

2) inter-clock-domain fault:originates at one clock domain, terminate at another clock domain

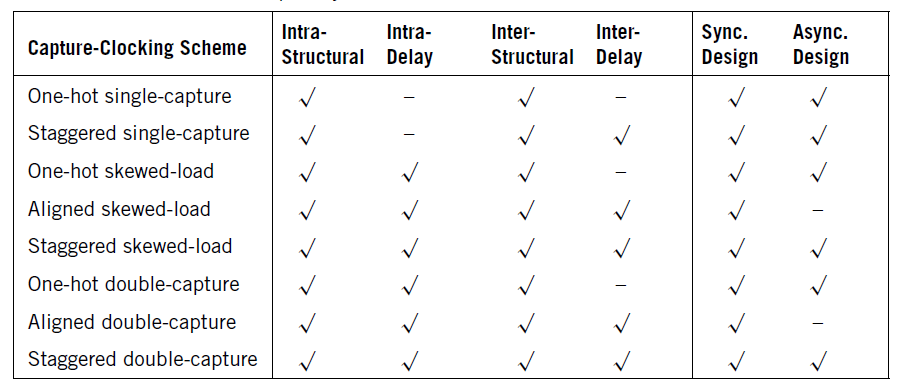

三种基本的capture-clocking scheme来做multiple clock domain test:

1) single-capture;

2) skewed-load;

3) double-capture;

两种fault model:

1) structural faults, such as stuck-at faults and bridging faults;

2) delay faults, path-delay faults and transition faults;

以STUMPS-based architecture

Single-capture是一种slow-speed test的技术,只需要一个capture pulse.测试intra-clock-domain和inter-clock-domain的structural faults.

两种approaches来进行test.

1) One-Hot Single-Capture

在一个capture window下只需要一个capture pulse,所以不用担心不同clock domain之间的clock skew,但是这种方式只能test intra-clock-domain和inter-clock-domain的structure faults, synchronous和asynchronous clock domain都可以.

synchronous clock在此处指edge完全相同的clock,asynchronous指edge不是完成相同的clock。

这样做的优势:

可以使用一个single,slow-speed global scan enable(GSE)来drive both clock domain,所以方便physical implement.

这样做的缺点是:

Test time会拉的比较长.

Staggered Single-Capture

Capture pulses C1 C2可以在capture window通过sequential和staggered order来test intra-clock-domain和inter-clock-domain structural faults.

在synchronous clock中,调整d2可以测试inter-clock-domain delay.

优点:a single slow-speed GSE signal方便physical implementation.

缺点:一些capture clock的order sequence可能导致一些structural faults的coverage loss.

Skewed-Load

Skewed-Load是一种at-speed delay test,a last shift pulse followed by a capture pulse.

在last shift pulse和next-to-last-shift pulse的值是不一样的,来保证transition的产生,并用这个capture pulse来capture output response

Scan enable信号必须在一个clock cycle中从shift mode转变为capture mode.

这种方法主要来解决intra-clock-domain delay fault detection

也主要分为三种approaches来实现:

1) one-hot skewed-load

2) aligned skewed-load

3) staggered skewed-load

One-hot Skewed-load

与single-capture的主要不同点:

1)apply shift-followed-by-capture pulses来detect intra-clock-domain delay faults,

2)每个scan enable signal switch operations from shift to capture within one clock cycle.

缺点:不能用来detect inter-clock-domain delay faults;很长的test time;与single, slow-speed GSE signal不能兼容(incompatible)

Aligned skewed-load

主要分为capture aligned skewed-load和launch aligned skewed-load,

可以测试所有的intra-clock-domain和inter-clock-domain faults,但是必须要求所有的clock都有一个reference clock, 这个clock的频率很高,

而且设计中不会存在这么一个refer clock

Staggered skewed-load

与single-capture的类似,一个delay d3会插在两个capture cycle之间,来消除两个clock domain之间的clock skew。

这样的设计同样可以测试所有的intra-clock-domain和inter-clock-domain的structural faults

缺点同样是scan enable信号的物理实现太困难。

Double-capture技术是另一种at-speed test的技术,是一种true at-speed test,可以测试所有的intra-clock-domain和inter-clock-domain的structural faults和delay faults,无论是在synchronous 或asynchronous design。并且scan enable比较容易physical implementation,scan/ATPG也容易实现。

同样分为三种实现

1) one-hot double-capture

一次只test一个clock,可以实现synchronous/asynchronous clock domain的intra-clock-domain的delay fault.

主要的区别:

1)两个capture clock来test intra-clock-domain的delay faults;

2)一个single,slow-speed的GSE信号方便物理实现;

缺点:

不能测试inter-clock-domain的delay faults,并且也是要有一个很长的test time。

2) Aligned Double-Capture

可以测试所有的intra-clock-domain和inter-clock-domain faults,

主要的区别是:

1) 两个capture clock cycle,而不是一个shift-followed-by-capture pulse

2) 需要一个single,slow-speed GSE,方便物理实现

缺点:

还是需要capture pulse的精确控制。

3) Staggered Double-Capture

可以测试所有的intra-clock-domain和inter-clock-domain faults,并且方便SCAN_ENABLE的物理实现。

Scan design和logic bist是两种提高production quality的最重要的structure offline test techniques.

但是,随着工艺的复杂,100%的single-stuck fault coverage也能以保证perfect production quality。

The remaining faults包括:timing-independent(由于connection上的resistance越来越大)和non-single-stuck-at faults,non-feedback bridging faults.

相对来说,intra-clock-domain的fault容易检测,inter-clock-domain的delay fault testing比较复杂。

D必须设置的比较准确来detect inter-clock-domain faults

几种测试方法的比较: