1. 下去下个原理图。今天准备研究下DDR的控制,看介绍新一代的Nexys 4 DDR最值得被关注的改良是将原先的16 MiBCellularRAM升级为128 MiB的DDR2 SDRAM内存。Digilent将提供一个硬件描述语言(VHDL)参考模块,以封装DDR2控制器的复杂性

2. 这个网址有很多资料 https://reference.digilentinc.com/reference/programmable-logic/nexys-4-ddr/start?redirect=1

3. 看下板子的资源,下一篇可以用下XADC的模块,快速随机存储器不知道怎么用,估计是vicado自动分配

1 Xilinx Artix-7 FPGA XC7A100T-1CSG324C 2 15,850个逻辑片,每片有4个6-input LUTs和8个触发器 3 4,860Kbits的快速随机存储器 4 6个时钟管理模块,每个有锁相回路(PLL) 5 240个DSP片 6 内部时钟速度超过450MHz 7 片上模数转换器(XADC) 8 128 MiB DDR2

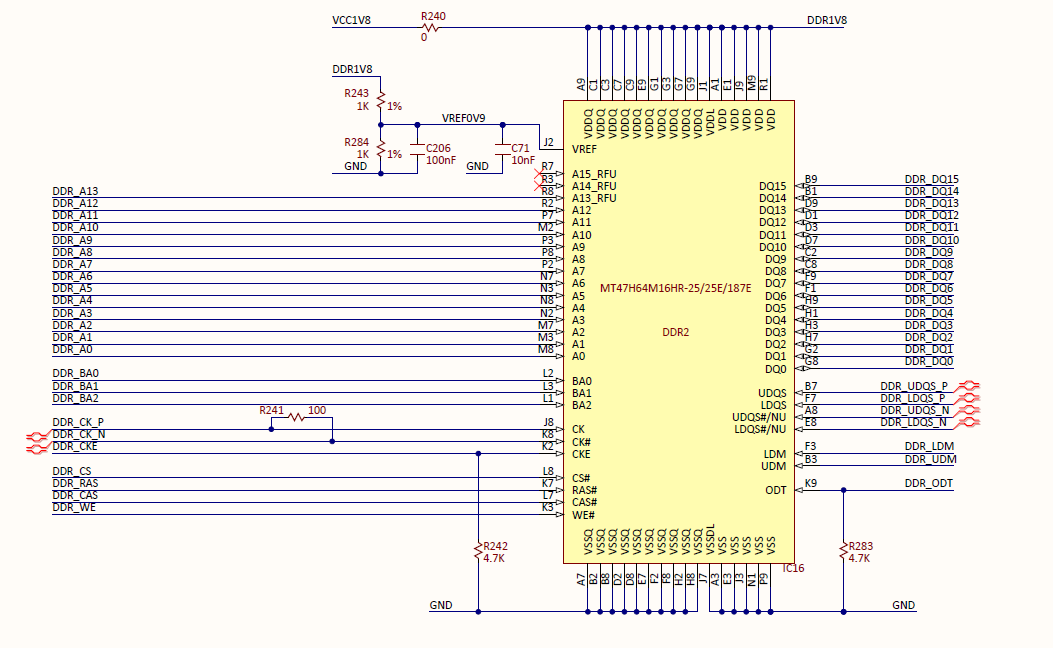

4. DDR的型号是MT47H64M16,3条BANK线,14位地址线,16位数据线。It is routed to a 1.8V-powered HR (High Range) FPGA bank with 50 ohm controlled single-ended

trace impedance.这个50欧姆的阻抗是什么意思?要求PCB Layout是50欧姆阻抗匹配么?

A[0-13]地址线,BA0-BA3是BANK选择,CK和CK#是时钟差分线,图上错误把CKE-CK#标记的查分,CKE是时钟使能线,CS#片选信号,LDM-UDM是输入数据掩码(作用不清楚),ODT终端电阻(作用不清楚看不明白),RAS#,CAS#,WE#好像是行列地址,以及写使能,DQ[0-15]数据线,DQS由DQ信号发出端发出DQS,信号接收端根据DQS的上、下沿来触发数据的接收。

5. 文档上说More advanced users or those who wish to learn more about DDR SDRAM technology may want to use the Xilinx 7-series memory interface solutions core generated by the MIG (Memory Interface Generator) Wizard.可以使用MIG向导产生IP控制核。

6. 看下DDR的时序图,暂时先不管时序,有点麻烦

7. 打开vivado,找到MIG,实例化一下

估计我的vivado版本太老,MIG不能适配芯片,去下载个新的先