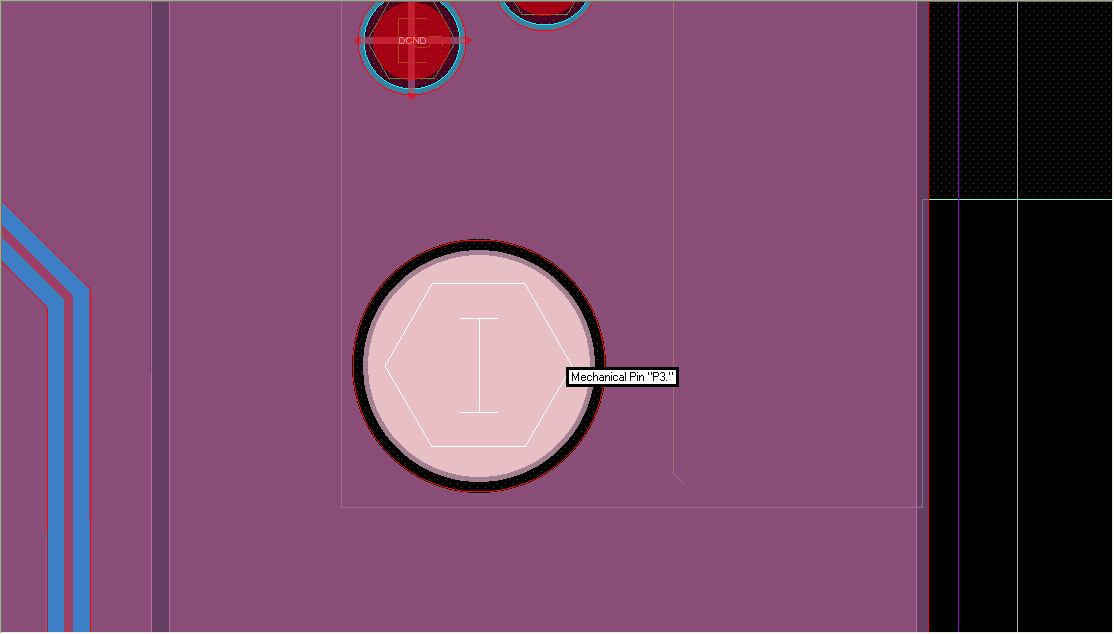

1、画了DB9的封装,共十一个焊盘,其中两个是机械焊盘,在绘制PCB板时,想要将其接地,但无法连接,如图所示

因为是机械焊盘,所以无法用更改logic的方法进行网络更改,现在只发现一个办法,就是更改封装,然后更新到PCB板中。

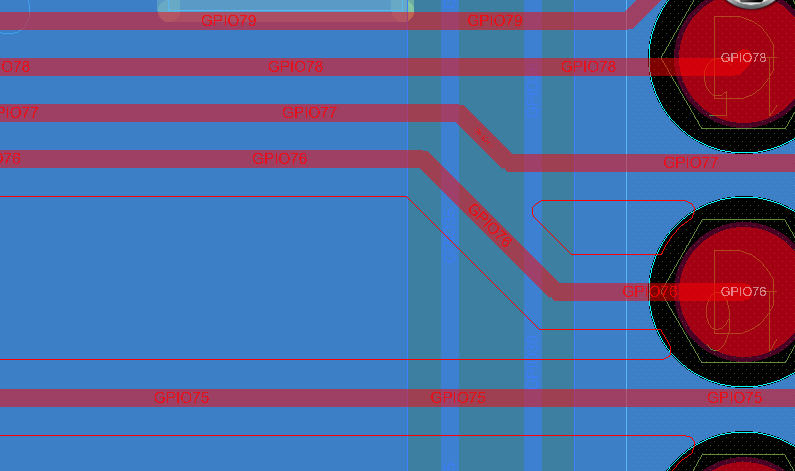

2、PCB覆铜后有边界线

display->Color/Visibility,在打开的对话框里找到stack-up->Conductor->Boundray和stack-up->Non-Conductor->Boundray,将其中的选项取消,就可以隐藏了。

3、在allegro中删除元件,提示“Selected item not valid for current operation, ignored: Pin "U*.161"”

解决方法:按control+D进入删除模式,再点击想要删除的元件即可。

4、利用向导画封装,提示

Performing DRC...

No DRC errors detected.

E- (SPMHA1-70): Pin is outside of the extents.

E- *Error* axlDBGetPad: argument #1 should be any user-defined (other) type (type template = "ogg") - nil

这是由于参数设置错误,比如SOIC封装的芯片,左右两排的引脚间距大于芯片的宽度,总结起来就是一句话,重新检查芯片的各项参数。

5、如何分割覆铜?

选择LINE,在options中选择Anti Etch,选择对应的板层,设置对应的选项,主要是设置线宽Line width,这个值决定了两个覆铜之间的间距,电压差不大时可以设置为15~20mil即可,之后按照自己所需划出区域。然后在Edit->Split Plane->Parameters中设置需要的参数,在同选项卡中选择creat,分割之后选择对应的网络即可。

6、如何改变铺铜的透明度,让走线更加清晰?

在allegro的菜单栏,显示选项卡”display->color/visibility“,在弹出的”color dialog“窗口中选择”display“,在"openGL"中选择”shapes transparecy“,左右调节,找到最适合的透明度,选择OK即可。