本文转自:自己的微信公众号《集成电路设计及EDA教程》

里面主要讲解数字IC前端、后端、DFT、低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程。

考虑到微信公众平台上面发布的很多推文百度搜索不到,所以以后的推文也会在这里进行转载。

《数字IC后端布局阶段对Tie-high和Tie-low Net的处理》

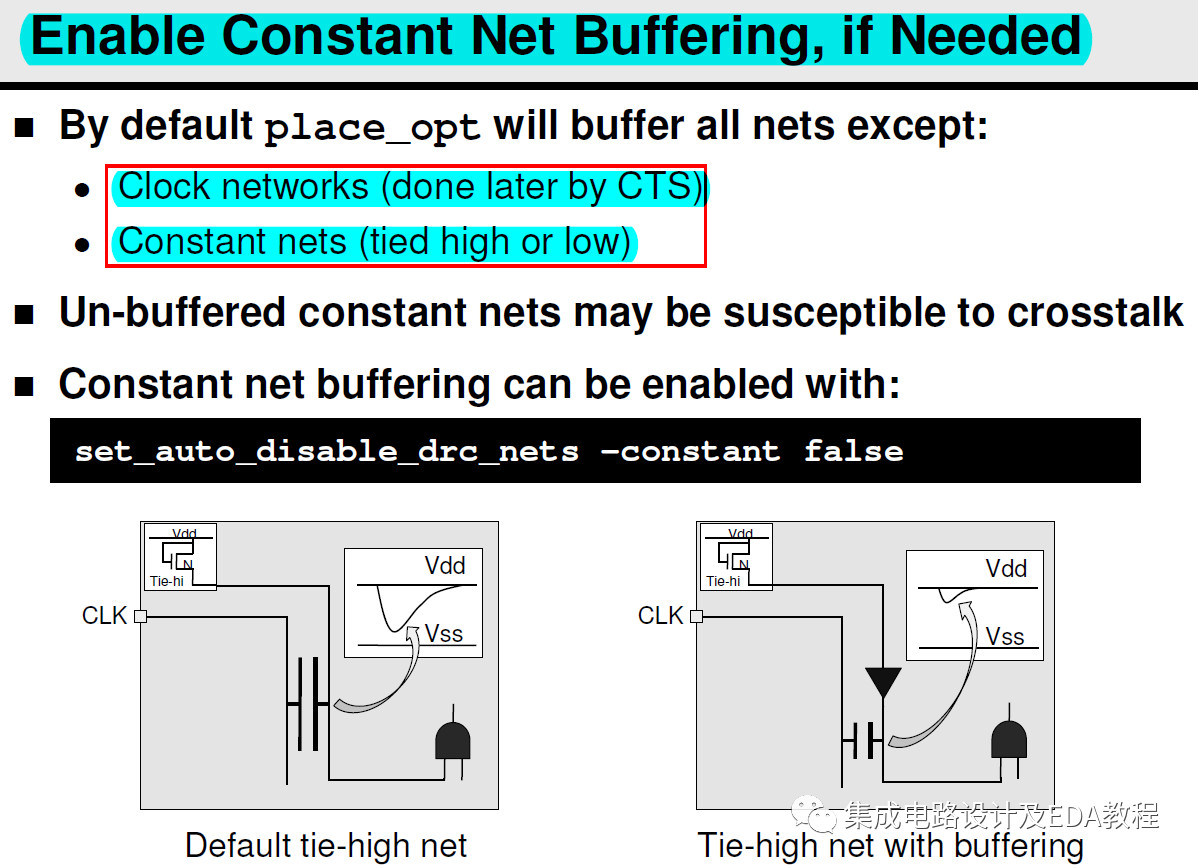

布局阶段ICC对于时钟网络和恒0/1网络(Constant Net)的行为:

在布局阶段,在默认情况下,对于时钟网络和恒0/1网络(也就是Tie-high和Tie-low的net),ICC是不会做逻辑DRC(Design RuleConstraint)的检查与修复的。这也意味着在执行place_opt时,ICC不会在这些net上插入Buffer。在布局阶段我们也不想在时钟网络上插入Buffer,但是对于Tie-high和Tie-low的Net,如果软件不在上面插入Buffer,可能会产生一些问题。在默认设置下工具在place_opt时对tie-high和tie-low的net的行为:会用tie-high和tie-low的Cell去驱动尽量多的Cell。

逻辑DRC(Design Rule Constraint):

即max_transition, max_capacitance, max_fanout。这些规则决定布局布线引擎是否需要在这些Net上插入Buffer。

Constant Net上面不插入Buffer的缺点:

其信号容易受到串扰的影响,如下图所示:

在离Tie-high的Net比较近的地方,如果有个高速时钟信号(两条线并行走了很长的距离),那么它的恒定电平会受到串扰的影响而产生毛刺。

而对于加了Buffer的Tie-high网络,它不容易受到串扰的影响,原因如下:

1、由于互连线长度缩短了,因此耦合电容大幅降低,串扰会大大降低;

2、由于Buffer有非常好的电平保持和恢复能力,与Tie-high Cell相比,抗串扰能力更好。

Constant Net上面插入Buffer的缺点:

以面积为代价,Tie-high/low的net扇出越大(也就是说设计中固定0/1输入比较多),加的Buffer越多。

如何使能Constant Net Buffering呢?

ICC命令:set_auto_disable_drc_nets -constant false

set_app_varphysopt_new_fix_constants true

set_attribute[...] max_fanout 12

set_attribute[...] max_capacitance 0.2 -type float

设置完成后工具的行为:

用tie-high和tie-low尽量驱动更多的单元,同时满足指定的最大扇出和最大电容约束。

set_auto_disable_drc_nets命令可以在常量网络上启用DRC修复。

physopt_new_fix_constants变量设置为true会使得工具在优化期间注意最大电容约束。最大电容约束由max_capacitance属性确定,该属性使用set_max_capacitance或set_attribute命令设置。 set_attribute命令用于明确指定设计中对象的最大扇出和最大电容约束。

## 为了方便大家交流讨论 ##

## 建了一个QQ群 ##

## 集成电路设计及EDA教程 ##

## 加群请备注:EDA ##

## 群二维码如下 ##