- 533SPI的特性

- 最高速度可达SCLK/4;

- 支持主模式和从模式;

- 可使用8个GPIO口作为从选择线:

- 1 slave select input pins

- 7 slave select output pins

- DMA支持

- 可编程的时钟极性和相位;

- 可编程的波特率;

- 可编程的字长度:8或16bits

- 接口信号说明

- 时钟信号SCK

由主设备产生,是门控的,即只在传输期间有效,在没有数据操作时,是无脉冲波形的。在一个边沿输出数据、另一个边缘采样数据。

- Master Out Slave In(MOSI)/Master In Slave Out(MISO)

双向数据引脚,方向取决于设备是主设备还是从设备。

- SPISS,PF0

作为从机时的片选信号;

PFx:作为主机时的设备选择信号。

- 电路连接方法如下:

4. 时钟的极性与相位问题:

这里的设置要取决于我们所采用的设备的SPI接口模式,假如设备是上升沿采样,下降沿输出,空闲时间为高电平,则对应的DSP设置为:CPOL = 1, CPHA = 1,即模式4.

5. 时钟频率问题:

时钟频率是由SPI_BAUD register决定的,计算方法为:

SCK = SCLK/(2*SPI_BAUD);

假设我们SCLK = 120MH,SPI_BAUD = 4,则SCK = 15M,即SPI的波特率为15MHz。

6.其它寄存器的设置

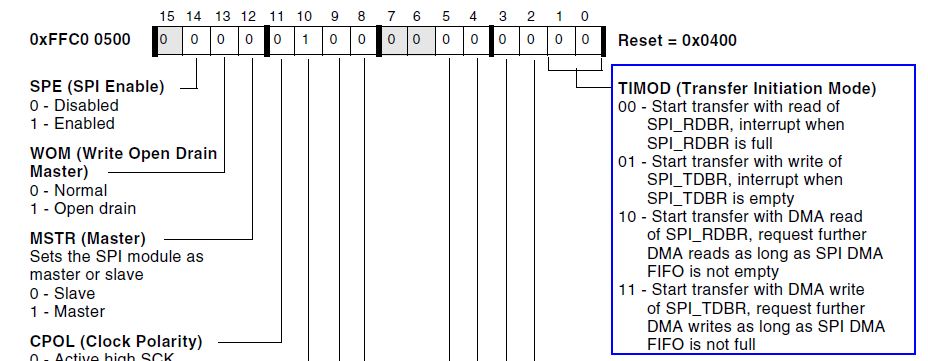

其它寄存器的设置按照寄存器的手册相关位的说明即可,需要解释的是SPI_CTL中TIMOD位的设置。

从时钟SCK与数据的关系波形中注意到,在8个时钟周期中,可以同时发送一个字节的数据,同时采样一个字节的数据。本例程中设置为01,也就是发起传输是由向SPI_TDBR寄存器中写数据导致的。那接受数据时如何发起SCLK呢?答案是要在读SPI_RDBR之前,发送一个字节的数,这个数发送完成的同时,采样也结束了。因此:

因此(这里为16位操作):

- 写操作:spi_send_read_data(0xaabb); //发送数据0xaabb

- 读操作:var = spi_send_read_data(0xffff); //0xffff为发送无效数据

7.具体的代码:

void init_spi(void) { *pSPI_BAUD=4; //配置速率为1/4系统时钟 SPI速率 = SCLK/2*SPI_BAUD *pSPI_FLG |=FLS2; //选择SPISEL2接口作为slave选择引脚 //enable spi,master mode,MSB first,16 bit transfer //CPOL,CPHA(slave select pin controlled by software) //start transfer with write of SPI_TDBR *pSPI_CTL = SPE|MSTR|CPHA|CPOL|SIZE|0x0001; } uint16_t spi_send_read_data(uint16_t data) { uint16_t i; *pSPI_FLG &= ~FLG2; //将SPISEL2拉到0 *pSPI_TDBR = data; //将数据送入SPI传输数据寄存器 while(*pSPI_STAT & TXS); //查看SPI传输状态是否完成,用示波器测试要花费一个CLK周期; //读过程 while(!(*pSPI_STAT & RXS));//查看SPI传输状态是否有数据需要接收 i = *pSPI_RDBR; //读取数据 *pSPI_FLG |= FLG2; //将SPISEL2拉到1,完成数据传输 return i; }