对于消抖,有很多种写法。今天分享一下我的写法。

基本思路:

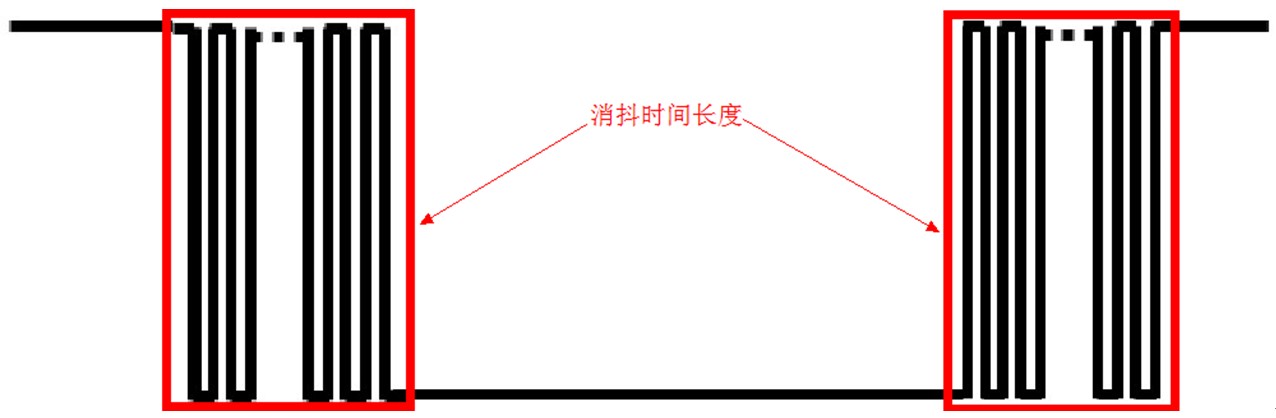

1. 看图

图1 图2 图3

图1 是理想的按键按下信号变化,图2是FPGA采集到的按键按下的信号变化。图3是一个外部干扰导致的一个错误。

用什么办法能把图2中延续到我们图1中一样的信号呢,又怎样滤除图3中的干扰呢?

在各位前辈的苦思下,总结出一个最好的解决办法,就是延迟消抖:如果抖动在一定范围内,系统不认为是一个正确的按键。

正好今天我也是以延迟消抖的办法来设计。 如图3

依照前辈们的经验,抖动时间一般会少于20ms. 也就是说,如果数据稳定20ms,认为可以采集该数据。

设计基本思想,如果计数计数到20'HF_FFFF,则认为此时状态是稳定的状态。若计数计数到中间某值,输入有变化,则计数器会清零,重新计数。则等按键稳定20‘hf_ffff个时钟为止。下面给出按键的程序

1 `define UD #1 2 module key_jitter( 3 input clkin, 4 5 input key_in, 6 output key_value, 7 output [15:0] tout 8 ); 9 10 // inner signal 11 reg [1:0] key_in_r; 12 wire pp; 13 reg [19:0] cnt_base; 14 reg key_value_r; 15 16 //内部信号 17 always @(posedge clkin) 18 key_in_r<= `UD {key_in_r[0],key_in}; 19 20 // 检测有输入有没有变化 21 assign pp = key_in_r[0]^key_in_r[1]; 22 23 //延迟计数器 24 always @(posedge clkin) 25 if(pp==1'b1) 26 cnt_base <= `UD 20'd0; 27 else 28 cnt_base <= `UD cnt_base + 1; 29 30 //输出 31 always @(posedge clkin) 32 if(cnt_base==20'hf_ffff) 33 key_value_r <= `UD key_in_r[0]; 34 35 assign key_value = key_value_r; 36 endmodule