1、前言

NXP官方对I.MX6U系列的嵌入式SoC编写了相关的SDK包,类似于STM32开发使用的STD库或者HAL库,里面包含了I.MX6U评估板的许多测试例程,以及芯片外设的寄存器定义,对于这些相关的外设寄存器定义文件,在对I.MX6UL进行ARM裸机开发时,可以直接移植过来使用。

2、移植SDK包

先到NXP官网上下载并安装I.MX6UL嵌入式SoC的SDK包,链接如下:

下载Windows版本的SDK包,如下:

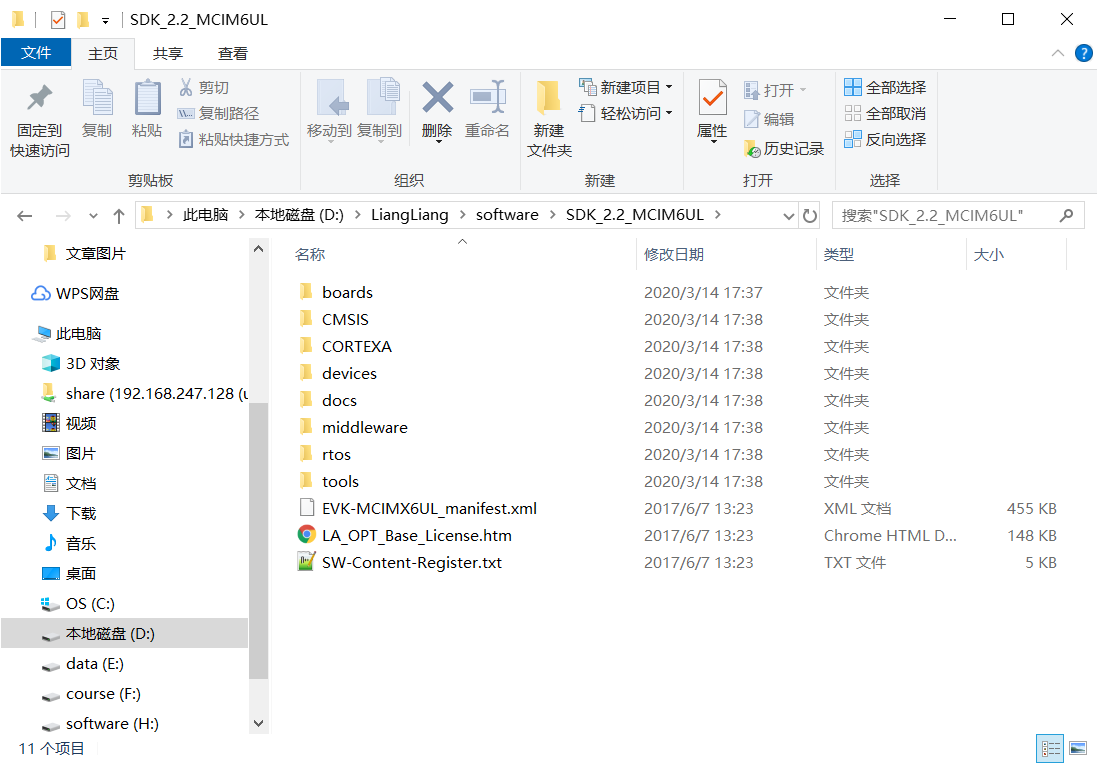

SDK包下载安装后,如下所示:

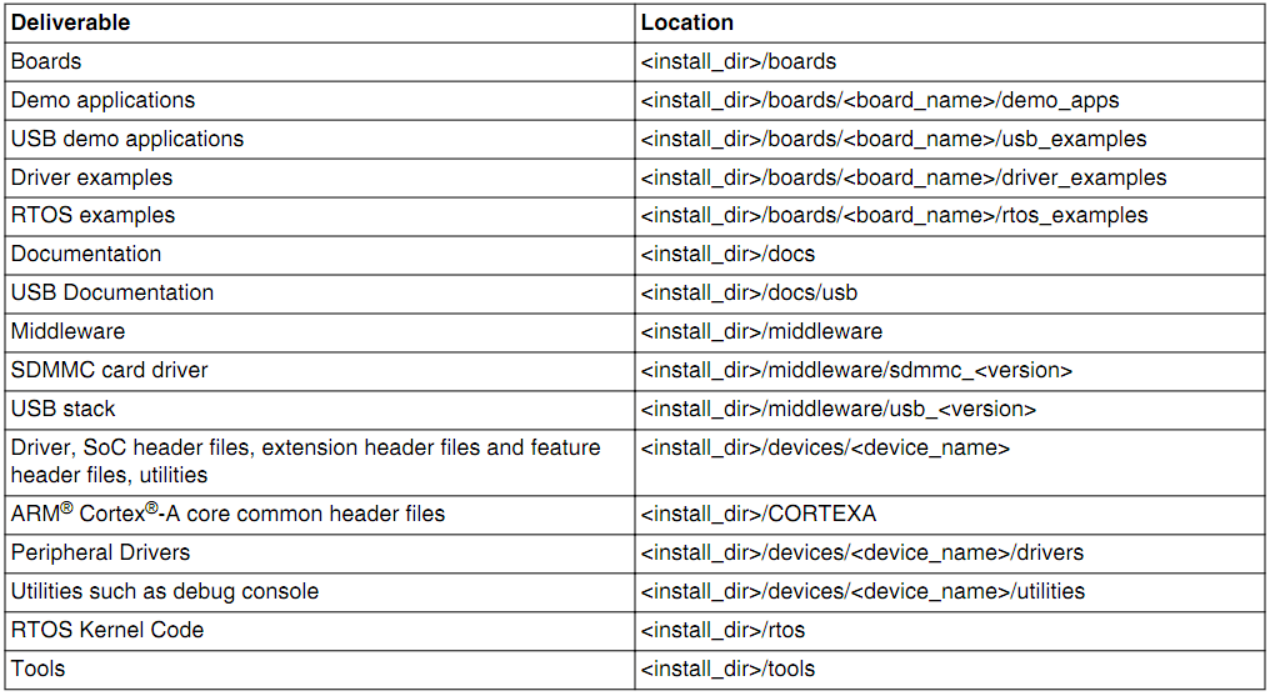

对于上图目录下的相关文件夹说明如下:

在上面已经提及过了,该SDK包是NXP官方为I.MX6UL嵌入式SoC的测试评估板所提供的,所以该SDK包里面提供了大量的测试例程,包括芯片上的外设驱动、USB开发以及RTOS等相关实例,当然我们并不需要所有的SDK包里面的文件,也并不是使用该SDK包进行开发,我们需要移植一些重要的芯片外设寄存器定义的文件,以便于后续ARM裸机的开发,关于SDK包里面的更详细内容,可以直接参考SDK包里面的文档。

首先需要移植的文件为fsl_common.h,该文件定义了一些公共的宏,文件路径如下:

<install-dir>SDK_2.2_MCIM6ULdevicesMCIMX6G2driversfsl_common.h

修改后的文件内容如下:

/* * Copyright (c) 2015-2016, Freescale Semiconductor, Inc. * Copyright 2016-2017 NXP * * Redistribution and use in source and binary forms, with or without modification, * are permitted provided that the following conditions are met: * * o Redistributions of source code must retain the above copyright notice, this list * of conditions and the following disclaimer. * * o Redistributions in binary form must reproduce the above copyright notice, this * list of conditions and the following disclaimer in the documentation and/or * other materials provided with the distribution. * * o Neither the name of the copyright holder nor the names of its * contributors may be used to endorse or promote products derived from this * software without specific prior written permission. * * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND * ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED * WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR * ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES * (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; * LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON * ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT * (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS * SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. */ #ifndef _FSL_COMMON_H_ #define _FSL_COMMON_H_ #include "types.h" /*! * @addtogroup ksdk_common * @{ */ /******************************************************************************* * Definitions ******************************************************************************/ /*! @brief Construct a status code value from a group and code number. */ #define MAKE_STATUS(group, code) ((((group)*100) + (code))) /*! @brief Construct the version number for drivers. */ #define MAKE_VERSION(major, minor, bugfix) (((major) << 16) | ((minor) << 8) | (bugfix)) /* Debug console type definition. */ #define DEBUG_CONSOLE_DEVICE_TYPE_NONE 0U /*!< No debug console. */ #define DEBUG_CONSOLE_DEVICE_TYPE_UART 1U /*!< Debug console base on UART. */ #define DEBUG_CONSOLE_DEVICE_TYPE_LPUART 2U /*!< Debug console base on LPUART. */ #define DEBUG_CONSOLE_DEVICE_TYPE_LPSCI 3U /*!< Debug console base on LPSCI. */ #define DEBUG_CONSOLE_DEVICE_TYPE_USBCDC 4U /*!< Debug console base on USBCDC. */ #define DEBUG_CONSOLE_DEVICE_TYPE_FLEXCOMM 5U /*!< Debug console base on USBCDC. */ #define DEBUG_CONSOLE_DEVICE_TYPE_IUART 6U /*!< Debug console base on i.MX UART. */ #define DEBUG_CONSOLE_DEVICE_TYPE_VUSART 7U /*!< Debug console base on LPC_USART. */ /*! @brief Status group numbers. */ enum _status_groups { kStatusGroup_Generic = 0, /*!< Group number for generic status codes. */ kStatusGroup_FLASH = 1, /*!< Group number for FLASH status codes. */ kStatusGroup_LPSPI = 4, /*!< Group number for LPSPI status codes. */ kStatusGroup_FLEXIO_SPI = 5, /*!< Group number for FLEXIO SPI status codes. */ kStatusGroup_DSPI = 6, /*!< Group number for DSPI status codes. */ kStatusGroup_FLEXIO_UART = 7, /*!< Group number for FLEXIO UART status codes. */ kStatusGroup_FLEXIO_I2C = 8, /*!< Group number for FLEXIO I2C status codes. */ kStatusGroup_LPI2C = 9, /*!< Group number for LPI2C status codes. */ kStatusGroup_UART = 10, /*!< Group number for UART status codes. */ kStatusGroup_I2C = 11, /*!< Group number for UART status codes. */ kStatusGroup_LPSCI = 12, /*!< Group number for LPSCI status codes. */ kStatusGroup_LPUART = 13, /*!< Group number for LPUART status codes. */ kStatusGroup_SPI = 14, /*!< Group number for SPI status code.*/ kStatusGroup_XRDC = 15, /*!< Group number for XRDC status code.*/ kStatusGroup_SEMA42 = 16, /*!< Group number for SEMA42 status code.*/ kStatusGroup_SDHC = 17, /*!< Group number for SDHC status code */ kStatusGroup_SDMMC = 18, /*!< Group number for SDMMC status code */ kStatusGroup_SAI = 19, /*!< Group number for SAI status code */ kStatusGroup_MCG = 20, /*!< Group number for MCG status codes. */ kStatusGroup_SCG = 21, /*!< Group number for SCG status codes. */ kStatusGroup_SDSPI = 22, /*!< Group number for SDSPI status codes. */ kStatusGroup_FLEXIO_I2S = 23, /*!< Group number for FLEXIO I2S status codes */ kStatusGroup_FLEXIO_MCULCD = 24, /*!< Group number for FLEXIO LCD status codes */ kStatusGroup_FLASHIAP = 25, /*!< Group number for FLASHIAP status codes */ kStatusGroup_FLEXCOMM_I2C = 26, /*!< Group number for FLEXCOMM I2C status codes */ kStatusGroup_I2S = 27, /*!< Group number for I2S status codes */ kStatusGroup_IUART = 28, /*!< Group number for IUART status codes */ kStatusGroup_CSI = 29, /*!< Group number for CSI status codes */ kStatusGroup_SDRAMC = 35, /*!< Group number for SDRAMC status codes. */ kStatusGroup_POWER = 39, /*!< Group number for POWER status codes. */ kStatusGroup_ENET = 40, /*!< Group number for ENET status codes. */ kStatusGroup_PHY = 41, /*!< Group number for PHY status codes. */ kStatusGroup_TRGMUX = 42, /*!< Group number for TRGMUX status codes. */ kStatusGroup_SMARTCARD = 43, /*!< Group number for SMARTCARD status codes. */ kStatusGroup_LMEM = 44, /*!< Group number for LMEM status codes. */ kStatusGroup_QSPI = 45, /*!< Group number for QSPI status codes. */ kStatusGroup_DMA = 50, /*!< Group number for DMA status codes. */ kStatusGroup_EDMA = 51, /*!< Group number for EDMA status codes. */ kStatusGroup_DMAMGR = 52, /*!< Group number for DMAMGR status codes. */ kStatusGroup_FLEXCAN = 53, /*!< Group number for FlexCAN status codes. */ kStatusGroup_LTC = 54, /*!< Group number for LTC status codes. */ kStatusGroup_FLEXIO_CAMERA = 55, /*!< Group number for FLEXIO CAMERA status codes. */ kStatusGroup_LPC_SPI = 56, /*!< Group number for LPC_SPI status codes. */ kStatusGroup_LPC_USART = 57, /*!< Group number for LPC_USART status codes. */ kStatusGroup_DMIC = 58, /*!< Group number for DMIC status codes. */ kStatusGroup_SDIF = 59, /*!< Group number for SDIF status codes.*/ kStatusGroup_SPIFI = 60, /*!< Group number for SPIFI status codes. */ kStatusGroup_OTP = 61, /*!< Group number for OTP status codes. */ kStatusGroup_MCAN = 62, /*!< Group number for MCAN status codes. */ kStatusGroup_CAAM = 63, /*!< Group number for CAAM status codes. */ kStatusGroup_ECSPI = 64, /*!< Group number for ECSPI status codes. */ kStatusGroup_USDHC = 65, /*!< Group number for USDHC status codes.*/ kStatusGroup_LPC_I2C = 66, /*!< Group number for LPC_I2C status codes.*/ kStatusGroup_ESAI = 69, /*!< Group number for ESAI status codes. */ kStatusGroup_FLEXSPI = 70, /*!< Group number for FLEXSPI status codes. */ kStatusGroup_MMDC = 71, /*!< Group number for MMDC status codes. */ kStatusGroup_MICFIL = 72, /*!< Group number for MIC status codes. */ kStatusGroup_SDMA = 73, /*!< Group number for SDMA status codes. */ kStatusGroup_NOTIFIER = 98, /*!< Group number for NOTIFIER status codes. */ kStatusGroup_DebugConsole = 99, /*!< Group number for debug console status codes. */ kStatusGroup_ApplicationRangeStart = 100, /*!< Starting number for application groups. */ }; /*! @brief Generic status return codes. */ enum _generic_status { kStatus_Success = MAKE_STATUS(kStatusGroup_Generic, 0), kStatus_Fail = MAKE_STATUS(kStatusGroup_Generic, 1), kStatus_ReadOnly = MAKE_STATUS(kStatusGroup_Generic, 2), kStatus_OutOfRange = MAKE_STATUS(kStatusGroup_Generic, 3), kStatus_InvalidArgument = MAKE_STATUS(kStatusGroup_Generic, 4), kStatus_Timeout = MAKE_STATUS(kStatusGroup_Generic, 5), kStatus_NoTransferInProgress = MAKE_STATUS(kStatusGroup_Generic, 6), }; /*! @brief Type used for all status and error return values. */ typedef int32_t status_t; #endif /* _FSL_COMMON_H_ */

接下来,需要移植的文件为fsl_iomuxc.h,该文件是与芯片上的IOMUX复用控制器相关的内容,里面定义了一些IOMUX控制器的驱动函数以及宏,能方便我们在开发时,能方便设置IO口引脚的复用模式以及IO引脚的电气属性配置,文件路径如下:

<install-dir>SDK_2.2_MCIM6ULdevicesMCIMX6G2driversfsl_iomuxc.h

修改后的文件内容如下: