好的时序是通过该严密的逻辑来实现的。http://blog.csdn.net/i13919135998/article/details/52117053介绍的非常好

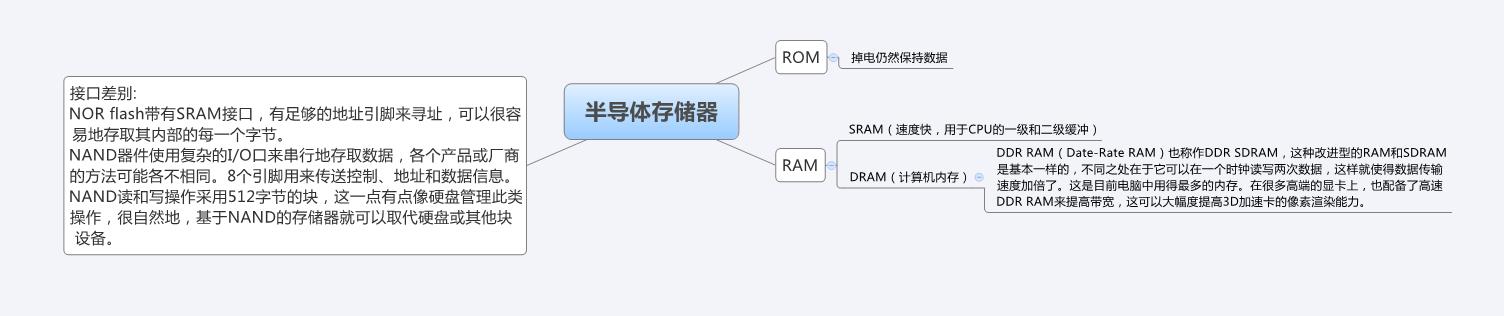

有RAM(随机存储器可读可写)ROM(只读存储器:存储内容是固定不变的,只能读出不能写入的半导体存储器。)CAM(内容可寻址存储器)、DRAM(动态随机存储器)、SRAM(静态随机存储器)、FLASH(闪存)、FIFO(先入先出缓存器)

表格总结

| 存储器 | 功能 | 寻址方式 | 掉电后 | 说明 |

| 随机存取存储器(RAM) | 读、写 | 随机寻址 | 数据丢失 | |

| 只读存储器(ROM) | 读 | 随机寻址 | 数据不丢失 | 工作前写入数据 |

| 闪存(Flash Memory) | 读、写 | 随机寻址 | 数据不丢失 | |

| 先进先出存储器(FIFO) | 读、写 | 顺序寻址 | 数据丢失 | |

| 先进后出存储器(FILO) | 读、写 | 顺序寻址 | 数据丢失 |

选择存储器需要考虑的设计参数有:包括微控制器的选择、电压范围、电池寿命、读写速度、存储器尺寸、存储器的特性、擦除/写入的耐久性以及系统总成本。

我所使用的C5G开发板有存储器SRAM和LPDDR,先看实例,然后将其加入到我的系统设计里边去,加油~

关于LPDDR有:DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,这种改进型的RAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。这是目前电脑中用得最多的内存,而且它有着成本优势,事实上击败了Intel的另外一种内存标准-Rambus DRAM。在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。

关于SRAM有:

话说SRAM(静态),DRAM(动态),SDRAM(同步(Synchronous)DRAM)

SRAM是Static Random Access Memory的缩写,中文含义为静态随机访问存储器,它是一种类型的半导体存储器。“静态”是指只要不掉电,存储在SRAM中的数据就不会丢失。这一点与动态RAM(DRAM)不同,DRAM需要进行周期性的刷新操作。 然后,我们不应将SRAM与只读存储器(ROM)和Flash Memory相混淆,因为SRAM是一种易失性存储器,它只有在电源保持连续供应的情况下才能够保持数据。“随机访问”是指存储器的内容可以以任何顺序访问,而不管前一次访问的是哪一个位置。

SRAM中的每一位均存储在四个晶体管当中,这四个晶体管组成了两个交叉耦合反向器。这个存储单元具有两个稳定状态,通常表示为0和1。另外还需要两个访问晶体管用于控制读或写操作过程中存储单元的访问。因此,一个存储位通常需要六个MOSFET。对称的电路结构使得SRAM的访问速度要快于DRAM。SRAM比DRAM访问速度快的另外一个原因是SRAM可以一次接收所有的地址位,而DRAM则使用行地址和列地址复用的结构。

SRAM不应该与SDRAM相混淆,SDRAM代表的是同步DRAM(Synchronous DRAM),这与SRAM是完全不同的。SRAM也不应该与PSRAM相混淆,PSRAM是一种伪装成SRAM的DRAM。

从晶体管的类型分,SRAM可以分为双极性与CMOS两种。从功能上分,SRAM可以分为异步SRAM和同步SRAM(SSRAM)。异步SRAM的访问独立于时钟,数据输入和输出都由地址的变化控制。同步SRAM的所有访问都在时钟的上升/下降沿启动。地址、数据输入和其它控制信号均于时钟信号相关

关于两者的应用方面:

Static RAM(SRAM),指的是一种具有静止时存取功能,在不需要刷新电路的情况下依然可以保持内部存储数据的存储芯片。

一般来说有两个主要的规格:

1. 一种是放置于单片机CPU与主存储之间的高速缓存,有两种规格,一种是会固定在电路主板上的高速缓存,另一种是插入电路卡槽的COAST扩充用的高速缓存。

2. 第二种是内置于CMOS芯片146818的电路中,内部有128字节小容量的SRAM存储芯片,用于存储我们设置的配置数据,也有用于加速单片机CPU内部数据的传递,从80486CPU开始,基本上CPU内部会将SRAM设计进去作为高速缓存,SRAM存储芯片在读取数据上速度比较快,不需要刷新电路,目前在市场上,价格相对其他的DRAM还是高了点,主要用于高要求的行业中的应用,

基本特点

1.速度相对快,不需要刷新电路,可以提高整体工作效率。

2.SRAM集成度低,功耗高,相同的容量的情况下比DRAM等存储芯片体积大,

SRAM存储的应用

1.CPU与主存之间的高速缓存。

2.CPU内部的L1/L2或外部的L2高速缓存。

3.CPU外部扩充用的COAST高速缓存。

4.CMOS 146818芯片。

同步SRAM存储芯片在传统上的应用是搜索引擎,用于对算法的实现,长时间来这也是SRAM存储芯片在网络的主要作用。跟随着新的存储技术的出现,设计者为SRAM存储芯片找到新的应用领域。

现在对路由器跟交换机的要求已经不仅仅限制于FIB搜索,计数器需要对接收服务包的信息包数量进行跟踪,并从中获取统计数据从而解决账单编制问题,并通过统计来不间断监视网络,并完成对问题的检测及判定,并随着每个信息包处理量的递增,就必然采取包缓冲器来提高处理能力,除了上面提及到的以外,随着系统中存储器资源的增加,动态存储分配也是必需的,路由器或者交换机的这些附加功能正在重新定义这网络系统的设计。

具有更多新功能的网络系统

并随着IPv6和VRF的快速普及,对更宽、更深、更快和更高效系统的需求变得更为迫切。系统设计者必须能以最低的成本来满足网络系统的所有度量标准。这时,之前的同步SRAM已经难以满足需求了。所以这些功能需要借助DDR或QDR SRAM等速度更快、带宽更高的SRAM存储芯片来实现。

QDR 与 DDR SRAM

在由瑞萨、、赛普拉斯IDT、NEC和三星公司组成的QDR协会的合作下开发出了QDR SRAM存储芯片,目的通过把SRAM存储芯片性能提升为原先的4倍用于满足那些不仅需要标准ZBT或NoBL SRAM的低延迟和满周期利用率,并还需要极大幅度提高工作频率的系统对带宽的要求。QDR SRAM存储芯片具有单独的读和写端口,设计里在每个数据引脚上以双倍数据速率各自独立地工作,因此能在一个时钟周期中传输4个数据字,因此4倍数据速率而得名。设计上采用分离的读/写端口从根本尚消除了SRAM与存储控制器之间对总线争用的冲突,这就是传统的公用I/O器件的问题所在。因此QDRII SRAM被称呼为回波时钟的源同步时钟,它们与数据输出由同一道生成。QDR SRAM采用了HSTL I/O标准,从而实现高速缓存操作。

QDR SRAM主要的应用在于面向那些需要在读和写操作之间进行转换,而DDR SRAM主主要的应用在于面向需要进行数据流式处理,此时,读和写操作之间的近期平衡为百分百的读操作或百分百的写操作。但在这种情况下,有一根QDR SRAM总线在百分之五十的时间里没被使用过。同时其它总线也是可能具有不平衡的近期读/写比例。这是督促人们对DDR公用I/O SRAM存储芯片开发的主要因素,在这种器件中,输入和输出数据端共同使用同一根总线。在从读操作向写操作转换的过程中,需要总线转向周期,并使得可用带宽减少。因此,对于某些系统来说,这必然产生了比QDR架构的平均总线利用率更优,控制信号几乎极少,而且又与QDR器件控制信号有些不同的地方。

SRAM、MRAM、pSRAM、 FLASH芯片、SDRAM(DDR1/DDR2/DDR3)

各类存储器之间的区别和联系: