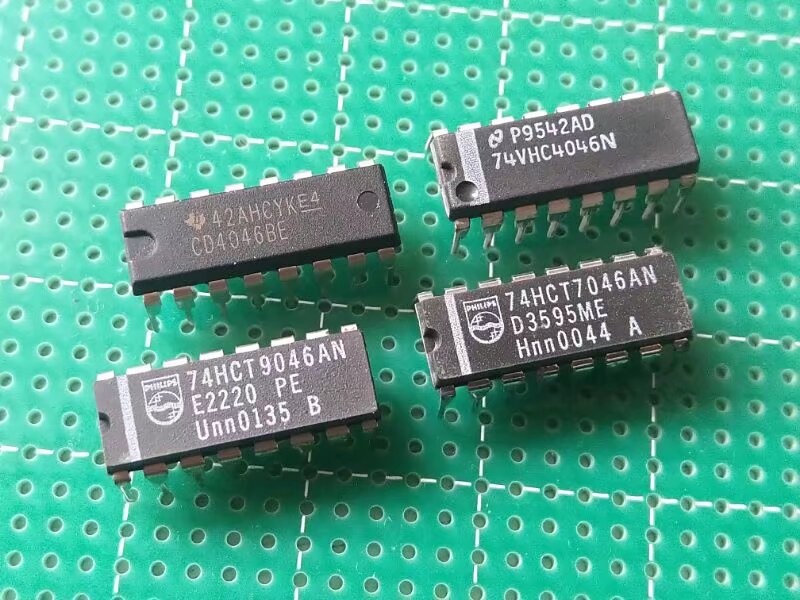

4046系IC(下简称4046),包括最常见的CD4046(HEF4046),可以工作在更高频的74(V)HC4046,以及冷门而且巨难买到的74HC(T)7046和74HCT9046(下文简单介绍),是工作在较低频率的模拟CMOS锁相环IC,被广泛应用在谐振功率变换器控制,FM解调以及频率合成等场合,也经常被单纯地当成VCO来使用,虽然我也不是很懂为什么要放着性能更好的专用VCO IC不用而非要把一个PLL的鉴相器浪费掉然后抽出VCO来用。然而我在应用这样一款常用的IC进行设计的时候却发现它的英文资料大多又臭又长,中文资料又语焉不详(而且之间的相似度较高连不详的方面都差不多),所以写这样一篇笔记来整理我查阅到的一些文献,大致地从VCO、鉴相器、环路滤波器、相位补偿几方面扯一扯怎么用4046设计一个pll电路。

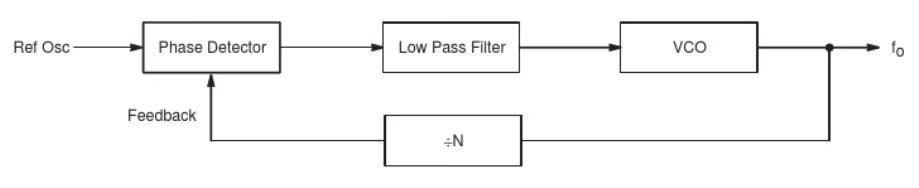

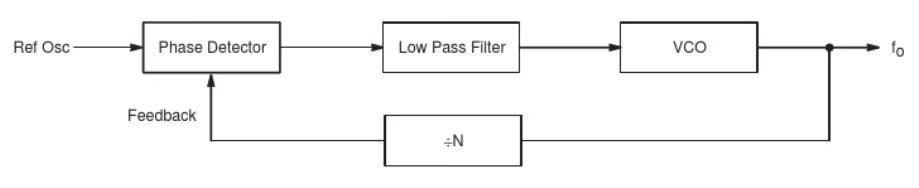

嗯,不多提了,要是有不懂锁相环是啥的还想看下去的话就给张图你们意会一下吧(

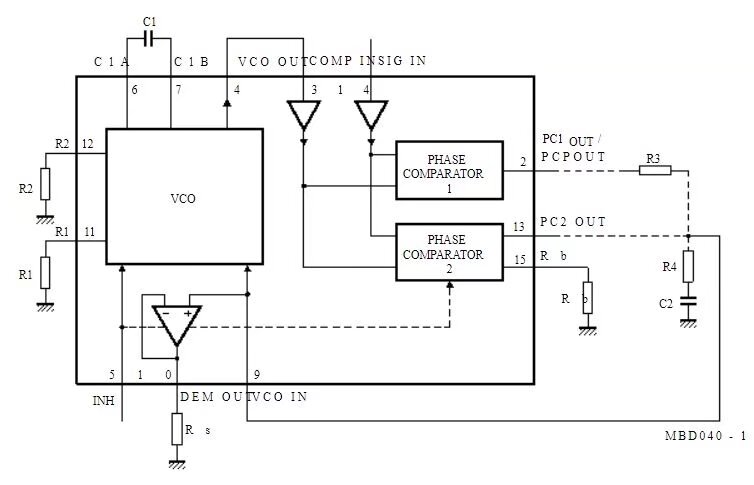

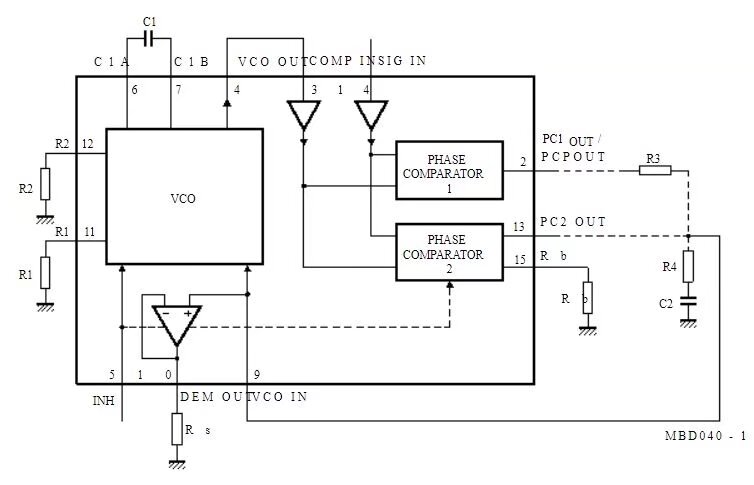

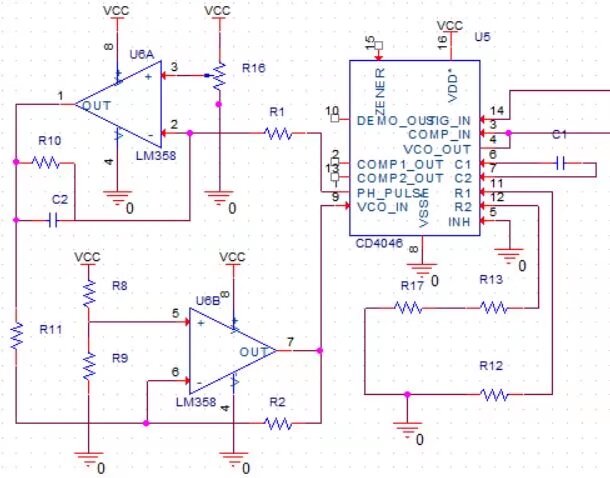

具体到4046上,信号相位差可由内部的两种(在74HC4046/7046里是三种,多了一种RS触发器实现的)鉴相器度量;内部振荡器是一个压控振荡器(VCO),其输出频率可由外部电压控制。由于鉴相器的输出是离散的三态电平脉冲,而VCO是由连续电压线性控制的,所以环路上需要一个低通滤波器(LPF)来完成这个离散电平到连续电压信号的变换。

4046系IC示意图。仅给出各型号共有的部分

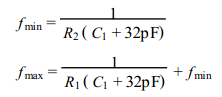

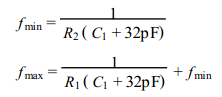

4046的VCO的静态工作状态由三个元件设定:震荡电容C1、频偏设置电阻R1、上限设置电阻R2。其中R1设置了VCO的频率下限,同时也使得异或门鉴相器的扫频范围从该下限开始。该电阻是非必须的,当11脚悬空(R1无穷大)时,VCO频率从0Hz开始递增。关于这三个元件和VCO频率的关系真可谓是众说纷纭,连不同厂家给的公式都不一样。实际上,由于元件的非线性、不同批次参数的离散性和不同厂商在design和fab上的差异,并没有一个精确的公式来表示VCO参数的设定。因为4046的频率跟踪特性,这样精确的公式也是不必要的。这里给出一组有较为普遍认同的公式,仅作为进行估算时的参考:

4046全家福,图上昔日的三个半导体巨头如今只剩一家(TI)未被并购或改组,令人唏嘘

锁相环的原理这里就不多提了,简而言之就是一个环路,通过负反馈把内置振荡器输出的相位和输入波形的相位之差不断缩小,最后达到一致。当然通过干涉反馈环路,也可以使输出与输入呈的特定倍频或者相差关系。

嗯,不多提了,要是有不懂锁相环是啥的还想看下去的话就给张图你们意会一下吧(

具体到4046上,信号相位差可由内部的两种(在74HC4046/7046里是三种,多了一种RS触发器实现的)鉴相器度量;内部振荡器是一个压控振荡器(VCO),其输出频率可由外部电压控制。由于鉴相器的输出是离散的三态电平脉冲,而VCO是由连续电压线性控制的,所以环路上需要一个低通滤波器(LPF)来完成这个离散电平到连续电压信号的变换。

4046系IC示意图。仅给出各型号共有的部分

4046的VCO的静态工作状态由三个元件设定:震荡电容C1、频偏设置电阻R1、上限设置电阻R2。其中R1设置了VCO的频率下限,同时也使得异或门鉴相器的扫频范围从该下限开始。该电阻是非必须的,当11脚悬空(R1无穷大)时,VCO频率从0Hz开始递增。关于这三个元件和VCO频率的关系真可谓是众说纷纭,连不同厂家给的公式都不一样。实际上,由于元件的非线性、不同批次参数的离散性和不同厂商在design和fab上的差异,并没有一个精确的公式来表示VCO参数的设定。因为4046的频率跟踪特性,这样精确的公式也是不必要的。这里给出一组有较为普遍认同的公式,仅作为进行估算时的参考:

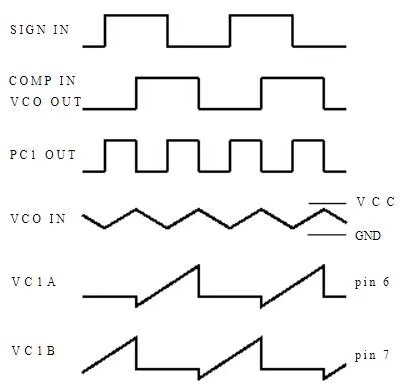

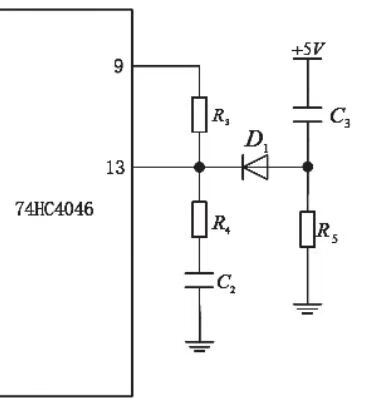

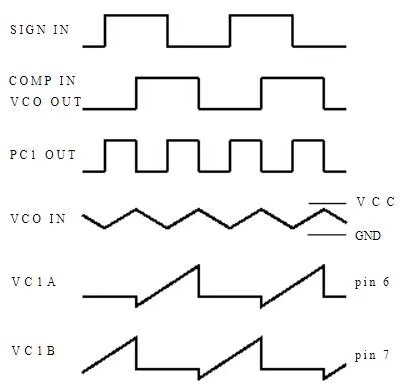

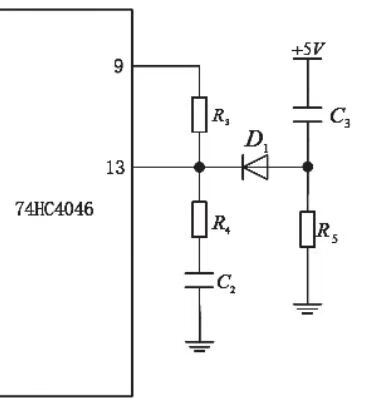

4046的1号鉴相器(PDI)由异或门实现,逻辑很简单:两输入电平相同时输出低电平,相异时输出高电平。这个简单的逻辑在输入信号和反馈信号相位差在0-180度内时工作得很好,然而超出这个范围环路就会往相反的方向调节VCO。[1]不少关于鉴相器1锁相范围窄或易失锁定状况的反映就是这个原因。另外,为达到最大的锁相范围,1号鉴相器需要输入信号有50%的占空比,且1号鉴相器比2号鉴相器对谐波更敏感。[2]1号鉴相器控制的VCO的初始频率是VCO的下限频率。若该下限频率被设置得过低,使得与输入频率之差超出了鉴相器锁定范围,会导致PLL一直无法入锁。这时需要在13脚引入一个扫频电路,使得VCO从上限频率开始扫频。

PD1原理图(左)工作波形(中)及扫频电路 (右)

PD1原理图(左)工作波形(中)及扫频电路 (右)

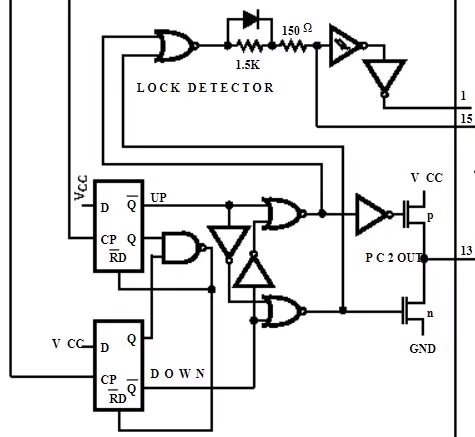

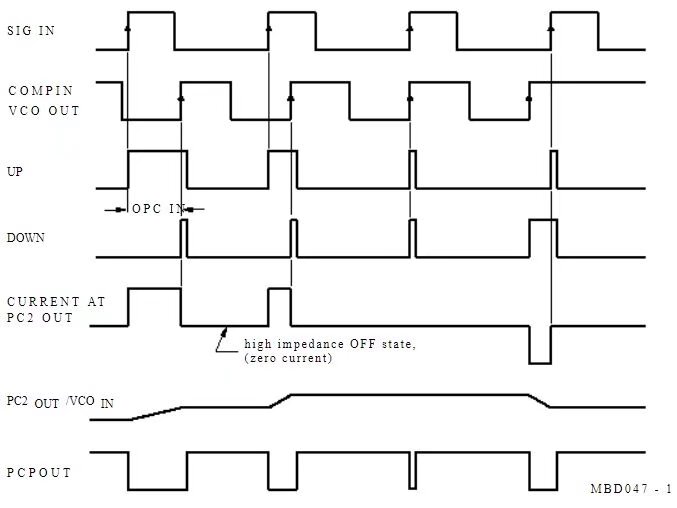

相比之下,由D触发器组成的复杂网络实现的2号鉴相器(PDII)可以实现更大的锁相范围。2号鉴相器在反馈信号超前输入信号时输出低电平,直到反馈信号出现上升沿之后变为高阻态。反之,则输出低电平,在输入信号上升沿后变为高阻态。2号鉴相器的锁相范围和捕获范围相同,且不受低通滤波器的影响。因为2号鉴相器优异的性能,其更被众多应用所青睐,不过它也不是万精油,相对1号鉴相器他对噪音更加敏感,[3]而且关于二号鉴相器也有出现鬼畜的反映,国外4hv论坛给出一种可能的解释:一旦漏掉一个脉冲,鉴相器就会认为出现了360度的相位差而去补偿。[4]2号鉴相器控制的VCO初始频率是VCO工作范围的中点,由于其锁相范围和捕获范围相同,一般不需要额外的扫频电路。

PD2原理图(左)工作波形(右)

对于74HC4046,其内部还有RS触发器实现的3号鉴相器(PDIII),因为不常用而且不是所有的4046系IC都有,这里不多介绍了。

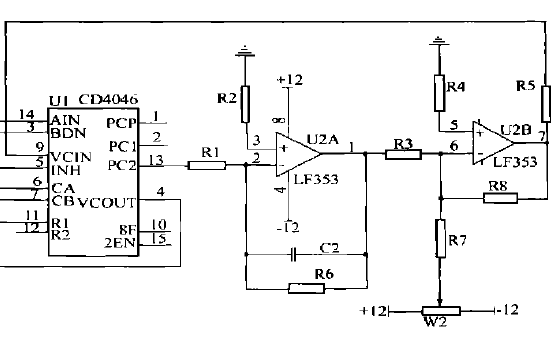

4046的环路滤波器可能是整个电路设计中最复杂的部分,我尚未找到国内资料对其详细的描述,而且因为采用鉴相器2的电路受LPF的影响相对较小,甚至出现了完全照搬的经验设计[5],这样的设计过程居然出自专业的电子工程师之手还堂堂地写在学报上,应该也算是EE界的迷惑行为了……国外方面,德州仪器关于4046系IC的应用有一篇

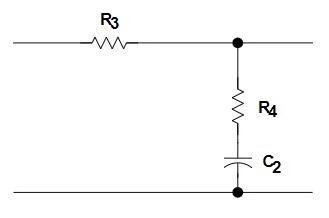

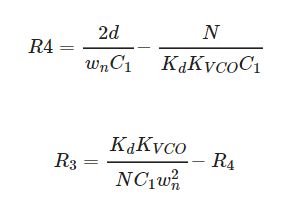

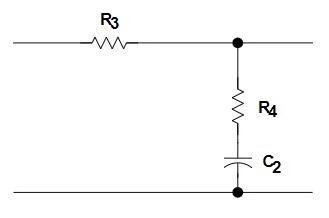

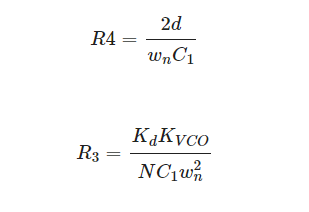

LPF可分为有源和无源两种。使用有源滤波器可以获得更好的线性度和单独的增益,并且方便移相器的设计(下文会提到),但也引入了额外的误差和噪声。无源LPF可以用普通的一阶RC滤波器实现,为了实现更灵活的设计,作为环路滤波器的LPF更常使用稍复杂的滞后超前型低通滤波器。该滤波器的器件取值可按如下公式计算:

其中N为分频系数;KVCO为压控振荡器增益,即VCO频率范围 / VCC;Kd为鉴相器增益,其对于PD1而言是VCC/π,对于PD2则是VCC/4π。设计时,通常先确定一个适宜大小的C2,并取wn= 输入频率 / 10,取d = 0.707。

其中N为分频系数;KVCO为压控振荡器增益,即VCO频率范围 / VCC;Kd为鉴相器增益,其对于PD1而言是VCC/π,对于PD2则是VCC/4π。设计时,通常先确定一个适宜大小的C2,并取wn= 输入频率 / 10,取d = 0.707。

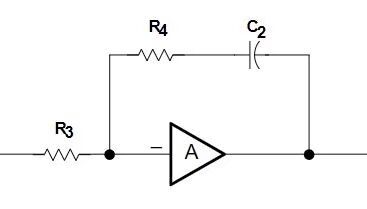

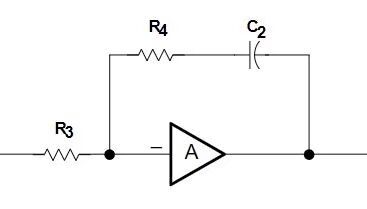

对于有源滤波器,计算方法则稍有不同:

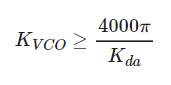

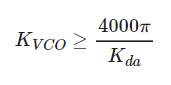

这里提到了一个“压控振荡器增益”的概念,此前没有给出计算方法——其实这是设计电路之初确定的参数。KVCO表征了VCO对于控制电压改变的敏感程度,要想使pll足够敏捷,这个值必须适当地大,一般取

[8]

[8]

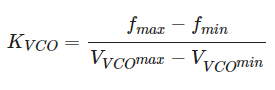

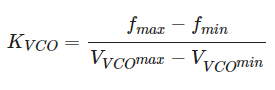

其中Kda为环路滤波器增益,如果使用无源滤波器的话则取1。KVCO与实际电路的关系是

其中f表示频率范围,VVCO表示控制电压范围。由于控制电压过低或过高会导致VCO进入非线性区,在VDD内设定一个数百毫伏的裕量可以保证精度。我们可以看出,在给定的VDD下,希望的工作频率范围越宽,KVCO就越小,意味着pll的响应越慢。所以希望同时得到大的工作频率范围和快的响应速度时,使用有源滤波器引入增益是很有必要的。

[8]

[8]其中Kda为环路滤波器增益,如果使用无源滤波器的话则取1。KVCO与实际电路的关系是

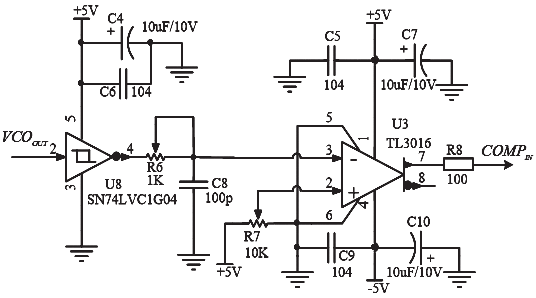

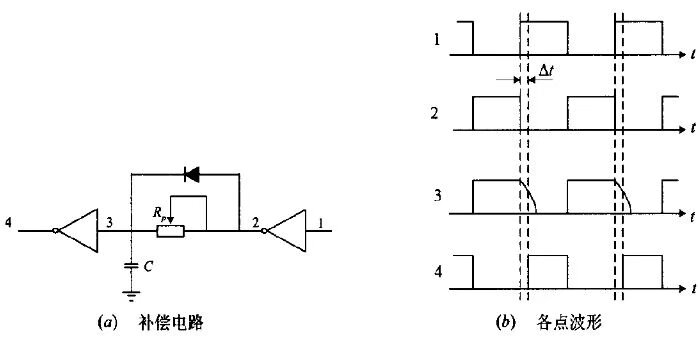

由于信号传输路径上各元件的延时,输出信号与输入信号会有一相位差。为补偿该相差,或为其他目的希望输出与输入信号有特定相移,需要在锁相环电路中设计移相功能。在该功能的实现上,国内工作者终于表现出相当的创造力,针对电路中的信号输入,反馈环路,LPF各环节均提出了对应的移相方法。其中,操作输入信号的方法较为不可取,它要求输入信号有一上升过程(如正弦波,三角波),通过比较器将输入信号整形,调整反相输入端的电压即可实现对输入信号的移相,进而使输出信号产生相同的相移。该方法对于方波输入无效,且受比较器速度性能限制。移相反馈信号的方法通过RC网络和整形电路将信号边沿延时,反馈环路为抵消该延时便会产生相位超前的信号。该方案的整形电路又有两种,分别使用比较器[9]和施密特触发器[10]实现,当然其速度也相应地受采用元件的限制。一般来说高速比较器相比高速施密特触发器较难获得,但因可以配置阈值电压,其调节相比使用施密特触发器的实现更加灵活。

使用比较器的电路(左)和使用施密特触发器的电路(右)

上述的两种方案都有一个问题,即只能使输出相位超前,这限制了PLL电路作为移相器的功能。这里给出一种相当巧妙的方法[11],通过对VCO的控制电压进行偏置,实现宽范围的移相,而且不受器件速度的限制。引文中的实现需要给运放双电源供电,然后通过在第二个运放构成的加法器的反相端叠加电压实现控制。其实,可以通过在两级运放的同相端设置一偏置电压Vbias来实现单电源供电,并通过调节任意一级的Vbias大小来实现控制,但这要求环路滤波器必须是有源LPF(即第一级反相放大器)。

引文给出的控制电路(左)和使用单电源的变体电路(右)

最后提一下开头提到的诸多型号的4046的差别。其中CD4046和HEF4046是CD4000系的IC,可以工作在15V的电压下,速度较慢,其VCO最高频率为1.4MHz。74系的4046和其他SN54/74系IC一样,只能工作在不超过5.5V的电压下,但也有着更高的速度:VCO频率最高能达到20MHz。型号中间的字母表示的特性也符合54/74系IC的标准:T表示兼容TTL电平输入,V表示可以耐受比VDD高的逻辑电平输入。

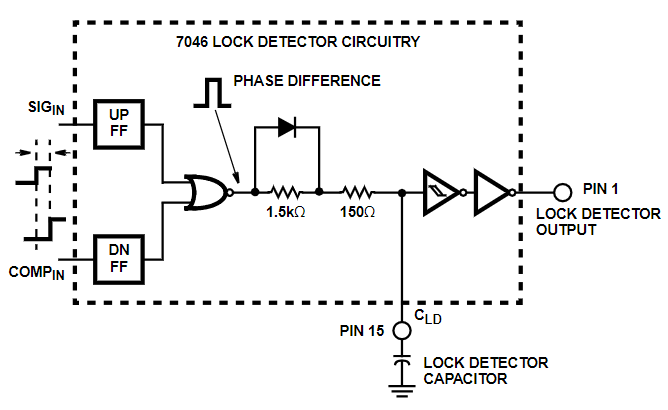

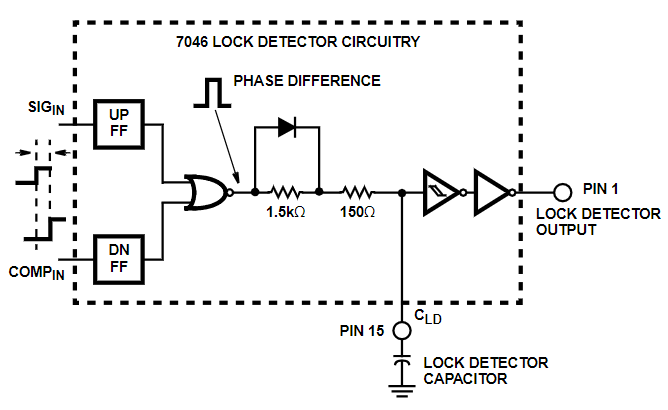

在很多文献中,4046的1脚被描述为“锁定指示”,往往连接一个LED来作为pll是否入锁的判断。事实上这个判断的依据并不可靠——该脚实际上反映了环路失锁的“程度”,当相位差越大时,该脚输出更多的电平。显然,在入锁时,因为输出一直为高,LED确实能指示入锁的状态;但失锁时,如果相位差较小,输出的低电平不够宽或多,LED只会微弱变暗。在74HC7046中内置了一个由RC滤波器和施密特触发器组成的检测电路,可以通过适当地设定外接电容的大小得到可靠的锁定指示。

74HC7046的入锁检测电路

如果要用一个特征区分开4大类4046,那一定是15脚的功能。在CD4046中,15脚是连接到VSS上的一个稳压管的负极;74HC4046中,15脚是三号鉴相器的输出;74HCT7046中,15脚用来接入锁定检测的RC滤波器的外接电容;74HCT9046中,15脚连接设定PDII输出电流源的限流电阻。

我们知道,RC振荡器的频率易受工作电压的影响。为了得到精确而稳定的频率输出,4046系IC对于供电的要求较高。在74HCT9046中,VCO供电的稳定由内置的带隙基准保证,相对放宽了对供电的要求。

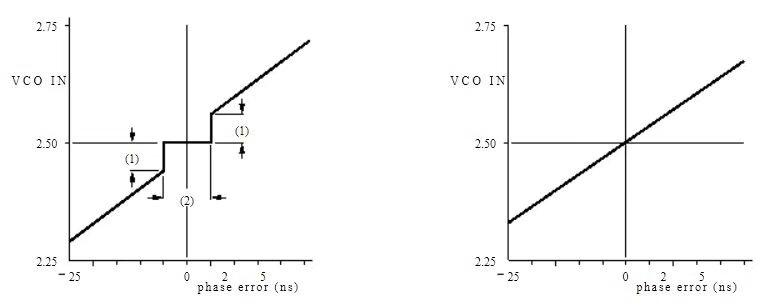

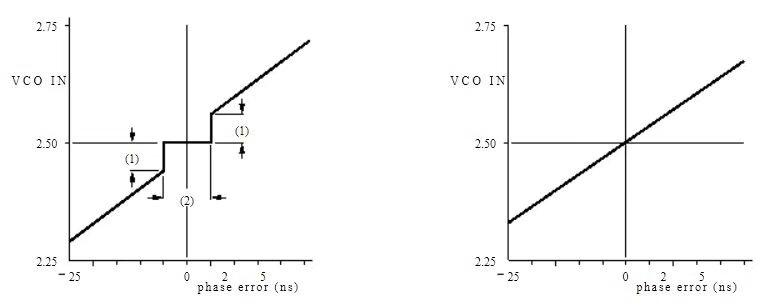

除74HCT9046以外的所有4046系IC,其二号鉴相器都因寄生电容而存在一个微小的死区,使得较小的相位差不能引起VCO的响应。9046中改进的PDII修复了这个问题。

4046/7046的PDII存在的死区(左)和9046中改进后的PDII的输出特性(右)

[1]:关于CD4046的相位比较器1(异或门)的一个问题 电源网在很多文献中,4046的1脚被描述为“锁定指示”,往往连接一个LED来作为pll是否入锁的判断。事实上这个判断的依据并不可靠——该脚实际上反映了环路失锁的“程度”,当相位差越大时,该脚输出更多的电平。显然,在入锁时,因为输出一直为高,LED确实能指示入锁的状态;但失锁时,如果相位差较小,输出的低电平不够宽或多,LED只会微弱变暗。在74HC7046中内置了一个由RC滤波器和施密特触发器组成的检测电路,可以通过适当地设定外接电容的大小得到可靠的锁定指示。

74HC7046的入锁检测电路

如果要用一个特征区分开4大类4046,那一定是15脚的功能。在CD4046中,15脚是连接到VSS上的一个稳压管的负极;74HC4046中,15脚是三号鉴相器的输出;74HCT7046中,15脚用来接入锁定检测的RC滤波器的外接电容;74HCT9046中,15脚连接设定PDII输出电流源的限流电阻。

我们知道,RC振荡器的频率易受工作电压的影响。为了得到精确而稳定的频率输出,4046系IC对于供电的要求较高。在74HCT9046中,VCO供电的稳定由内置的带隙基准保证,相对放宽了对供电的要求。

除74HCT9046以外的所有4046系IC,其二号鉴相器都因寄生电容而存在一个微小的死区,使得较小的相位差不能引起VCO的响应。9046中改进的PDII修复了这个问题。

4046/7046的PDII存在的死区(左)和9046中改进后的PDII的输出特性(右)

[2]:MC74HC4046A ON Semiconductor P8

[3]:MC74HC4046A ON Semiconductor P9

[4]:PLL SSTC with Type 2 phase comparator problems (added some info) 4hv

[5]:功率超声电源的频率跟踪电路 苏州大学学报 第30卷第2期 P69

[6]:CMOS Phase-Locked-Loop Applications Using the CD54/74HC/HCT4046A and CD54/74HC/HCT7046A Ti SCHA003B P31

[7]:Configuring and Applying the MC74HC4046A Phase-Locked Loop ON Semiconductor AN1410

[8]:MODELING, ANALYZING AND DESIGNING A PHASE-LOCKEDBATTERY CHARGER ournal of the Chinese Institute of Engineers, Vol. 30, No. 6, pp. 1037-1046 (2007) P1037

[9]:基于74HC4046兆赫兹级锁相控制电路的设计 电子技术 2011年45(2)

[10]:基于CD4046锁相环200KHZ的高频感应加热电源频率跟踪的研究 电子世界 2011年9月号

[11]:移相器的一种简单实现方法 微电子与基础产品 vol28