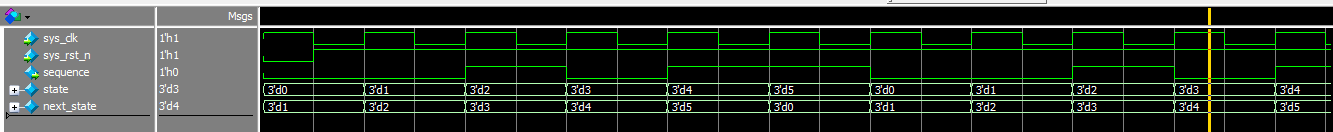

用一个二段式状态机产生序列信号:001011。

综合代码:

module fsm( input sys_clk, input sys_rst_n, output reg sequence ); parameter s0=3'd0, s1=3'd1, s2=3'd2, s3=3'd3, s4=3'd4, s5=3'd5; reg [2:0]state; reg [2:0]next_state; always @(posedge sys_clk or negedge sys_rst_n)begin if(!sys_rst_n) state<=s0; else state<=next_state; end always @(*)begin next_state=s0; case(state) s0:begin sequence=1'b0; next_state=s1; end s1:begin sequence=1'b0; next_state=s2; end s2:begin sequence=1'b1; next_state=s3; end s3:begin sequence=1'b0; next_state=s4; end s4:begin sequence=1'b1; next_state=s5; end s5:begin sequence=1'b1; next_state=s0; end default:next_state=s0; endcase end endmodule

仿真代码:

`timescale 1ns/1ns module fsm_tb; reg sys_clk; reg sys_rst_n; wire sequence; initial begin sys_clk=1; sys_rst_n=0; #10 sys_rst_n=1; end always #10 sys_clk=~sys_clk; fsm u_fsm( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .sequence (sequence) ); endmodule

仿真结果: