Quartus ii的pll ip核调用:

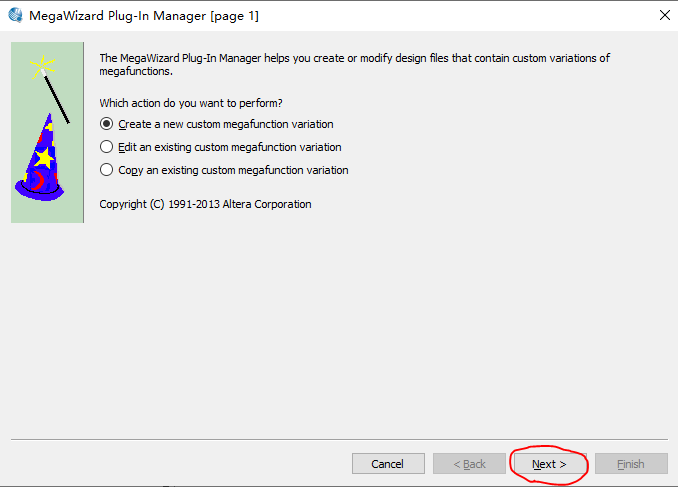

1、先建立好工程。点击“Tools”,接着点击“Mega Wizard Plug-In Manager”。

2、创建一个新的ip核:

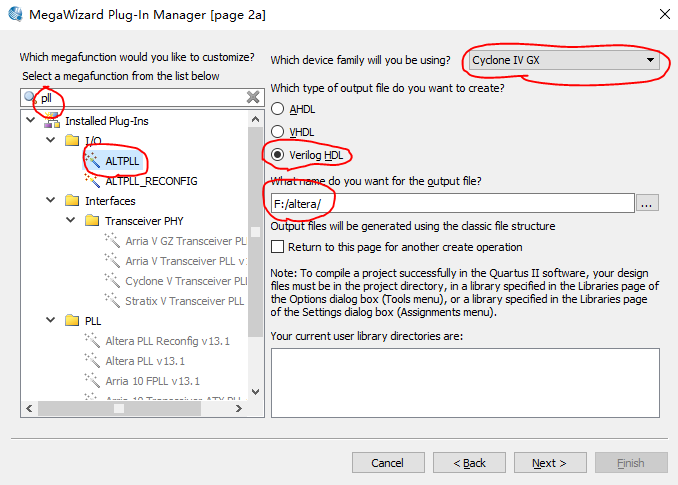

2、这里需要的是pll的ip核,所以就搜索“pll”,并选中“ALTPLL”,接着修改成fpga芯片型号,Verilog HDL,还有设置好pll ip核的路径和名称,这里的名称就相当于模块名。

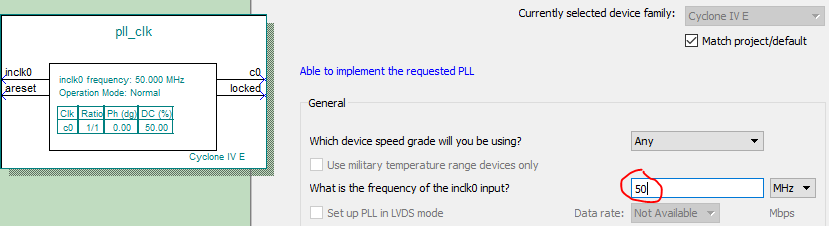

3、pll的ip核是对时钟分频并且输出,所以这里设置一个时钟,比如50MHz。

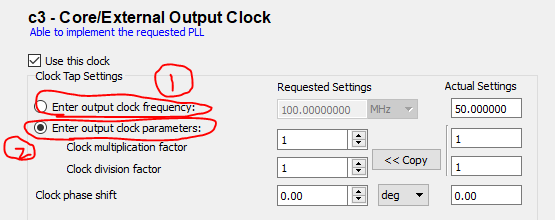

4、设置输出的时钟:

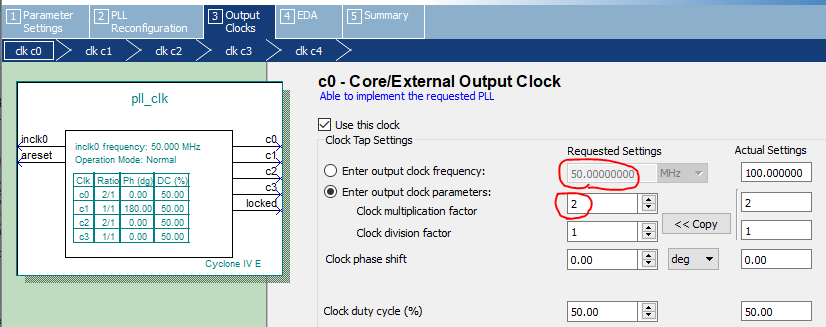

有两种方式去改变频率:方式1:直接填写输出的频率;方式2:使用乘法因子和除法因子。

比如这里c0我设成50MHz,又把乘法因子设置成2,那么c0的时钟频率是100MHz:

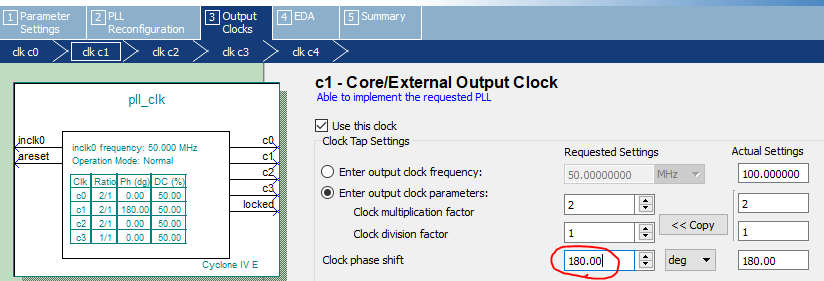

在c0时钟的基础上反转180°得到c1:

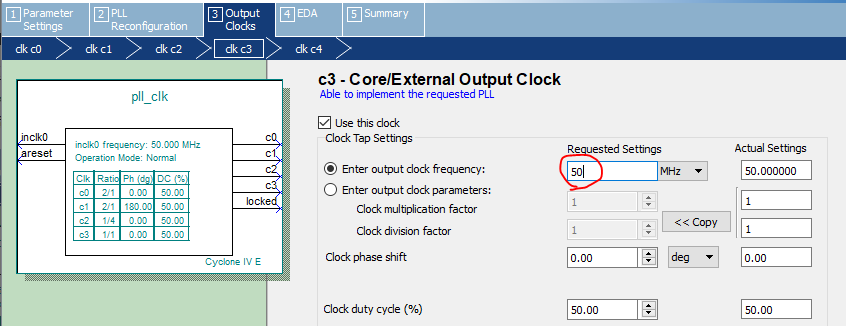

c2把100MHz分成4份,不知道为什么实际输出12.5MHz:

c3直接输出一个50MHz的时钟频率:

5、设置完成后,一直next,直到finish,最后yes。

6、然后为了测试,需要建立一个顶层文件,例化这个pll ip核。仿真用到的文件:

综合代码:

module pll_ip( input sys_clk, input sys_rst_n, output test_c0, output test_c1, output test_c2, output test_c3 ); wire rst_n;//作为其他模块的复位信号 wire locked; assign rst_n=sys_rst_n & locked; pll_clk u_pll_clk( .inclk0 (sys_clk), .areset (~sys_rst_n), .c0 (test_c0), .c1 (test_c1), .c2 (test_c2), .c3 (test_c3), .locked (locked) ); endmodule

仿真代码:

`timescale 1ns/1ns module pll_ip_tb; reg sys_clk; reg sys_rst_n; wire test_c0; wire test_c1; wire test_c2; wire test_c3; initial begin sys_clk<=1'b0; sys_rst_n<=1'b0; #10 sys_rst_n<=1'b1; end always #10 sys_clk<=~sys_clk; pll_ip u_pll_ip( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .test_c0 (test_c0), .test_c1 (test_c1), .test_c2 (test_c2), .test_c3 (test_c3) ); endmodule

7、仿真的时候,一个激励文件,一个顶层模块、例化模块pll_clk、一个altera_mf.v文件。其中altera_mf.v的位置需要打开Quartus ii软件的所在位置,搜索“altera_mf”,可以看到路径(...edasim_lib),复制到tb文件夹中与激励文件放一起。

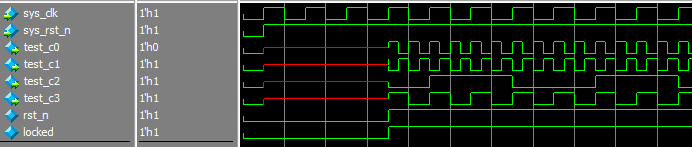

结果检验正确!