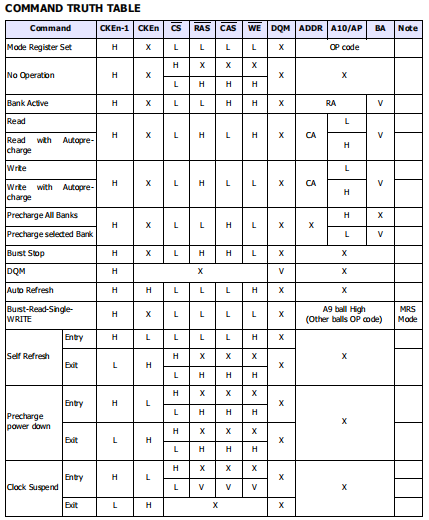

(3)向SDRAM写入数据。

观看视频:https://www.bilibili.com/video/BV16t411H7iw?p=7

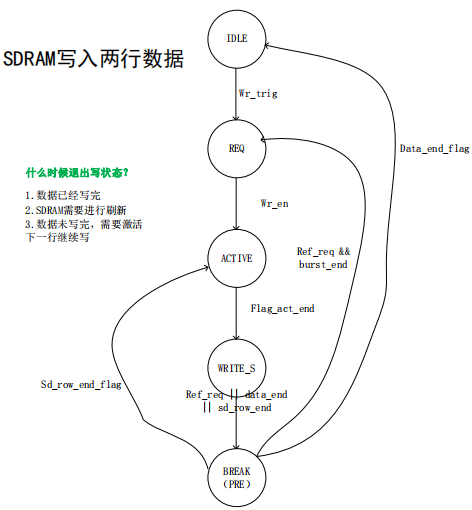

这里设计往SDRAM中写入两行数据。

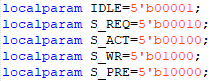

SDRAM写时序图:

‘写’的状态机:

状态REQ是写请求状态。

状态PRE是预充电状态。

退出‘写’的三种情况:

①数据已经写完

②SDRAM需要进行刷新了

③需要激活下一行

sdram写模块的时序设计图

依据上述两张时序图,可以实现写模块的代码。

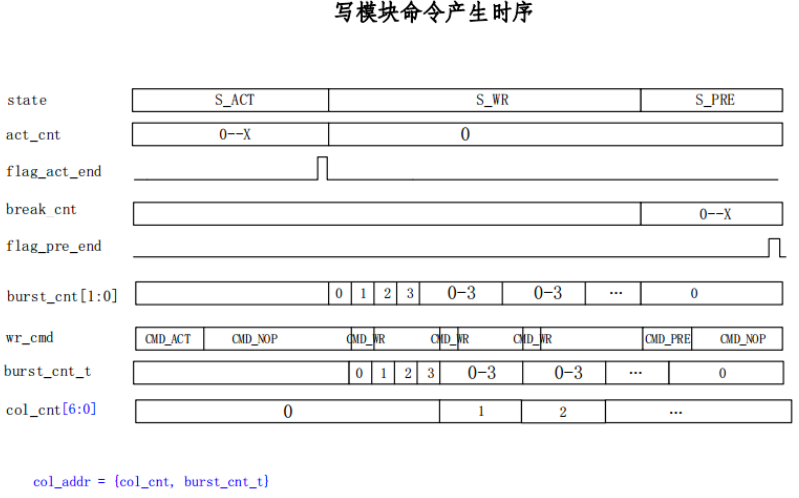

命令查询表格:

所以查询上面表格,写出如下命令:

代码设计不贴了。

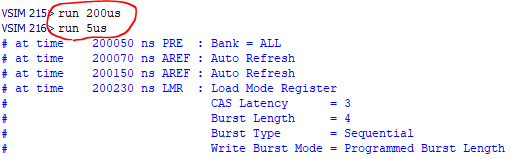

仿真情况如下:

激励文件中205us才开始触发写。

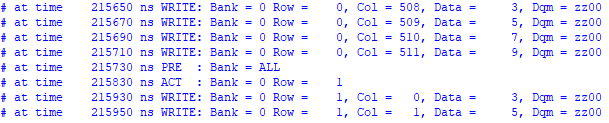

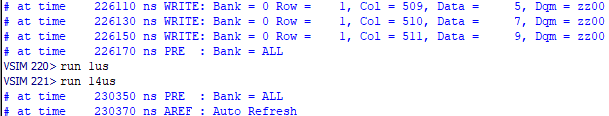

列地址写完512,然后换行Row=1。

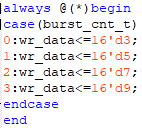

写数据:3,5,7,9。

写完两行之后,不再写,一直在刷新,每隔15us刷新一次。

需要跑15us才能看到刷新命令。

写end!