三种复位实现:同步复位、异步复位、异步复位同步释放

一、同步复位

同步复位是指复位信号只有在时钟有效边沿到来时才能生效的复位方法。如果时钟有效边沿未到来,即使是复位信号有效也不执行复位操作。

代码:

`timescale 1ns / 1ps module sync_reset( input clk, input rst_n, input data_in, output reg data_out ); always @ (posedge clk) if (!rst_n) data_out <= 1'b0; else data_out <= data_in; endmodule

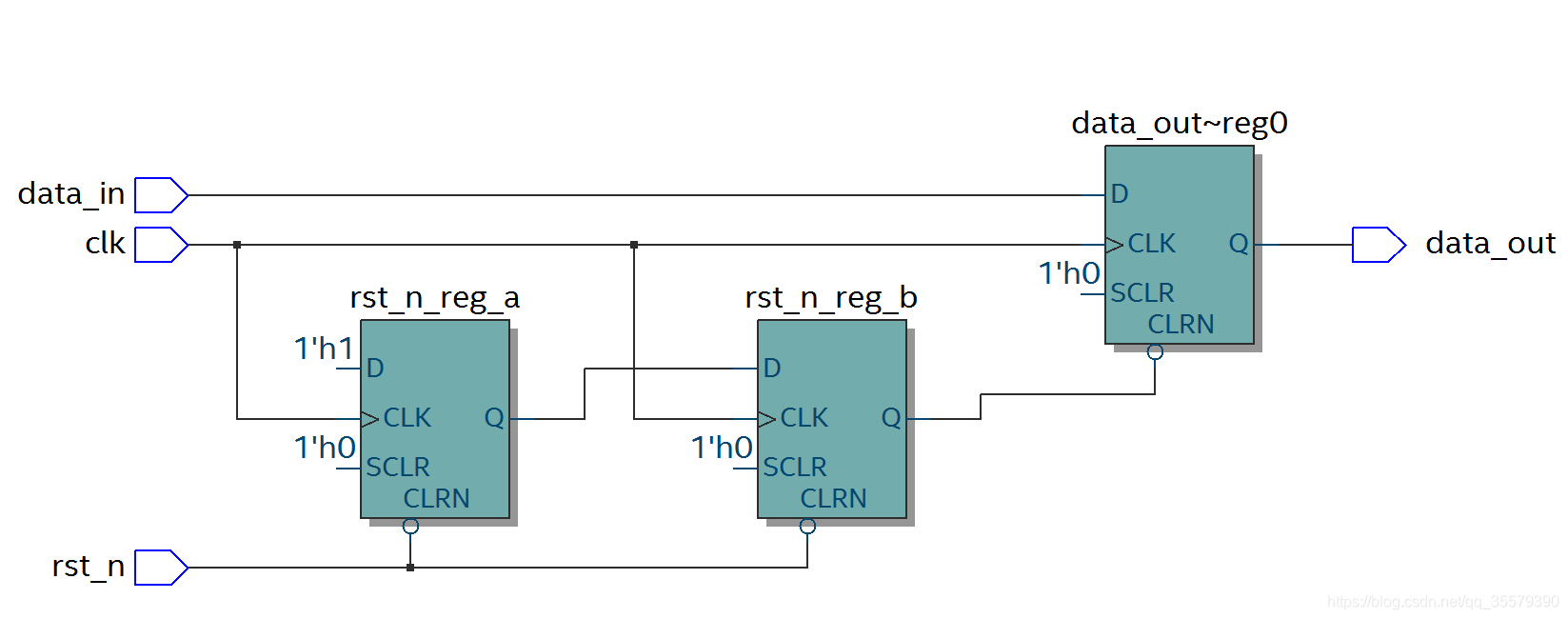

电路图:

采用同步复位的话,由于大多数寄存器没有单独的同步复位端口,综合出来的RTL一般是数据输入(data_in)和复位信号(rst_n)取与操作/如图的MUX。相比于异步复位,会额外消耗电路的组合逻辑资源。

二、异步复位

异步复位是指只要复位信号有效立即执行复位操作。即使是在时钟有效边沿未到来的时候,寄存器也执行复位操作。

代码:

`timescale 1ns / 1ps module async_reset( input clk, input rst_n, input data_in, output reg data_out ); always @ (posedge clk or negedge rst_n) if (!rst_n) data_out <= 1'b0; else data_out <= data_in; endmodule

电路图:

虽然异步复位没有占用额外的组合逻辑资源,但是其对复位信号的要求较高,假如复位信号中出现毛刺,会使整个寄存器执行复位操作。

总结一下同步与异步复位各自的优缺点

| 同步复位 | 异步复位 |

|---|---|

| 优点 | 优点 |

| 有利于时序分析 | 节省逻辑资源 |

| 有利于仿真器仿真 | 设计相对简单 |

| 能够滤除复位信号毛刺 | 信号识别方便 |

| 缺点 | 缺点 |

| 对复位信号的长度有要求,需要大于一个时钟周期 | 异步复位容易受到毛刺信号的干扰 |

| 大多数逻辑器件目标库内触发器没有同步复位端口,若采用同步复位会占用额外的组合逻辑资源 | 异步复位信号在释放时容易出现问题。异步复位信号在结束的时候,可能会不满足recovery和removal time,可能使电路进入亚稳态。 |

三、异步复位同步释放

代码:

`timescale 1ns / 1ps module test( input clk, input rst_n, input data_in, output reg data_out ); reg rst_n_reg_a,rst_n_reg_b; wire rst_n_sync; always @ (posedge clk or negedge rst_n) if (!rst_n) begin rst_n_reg_a <= 1'b0; rst_n_reg_b <= 1'b0; end else begin rst_n_reg_a <= 1'b1; rst_n_reg_b <= rst_n_reg_a; end assign rst_n_sync = rst_n_reg_b; always @ (posedge clk or negedge rst_n_sync) if (!rst_n_sync) data_out <= 1'b0; else data_out <= data_in; endmodule

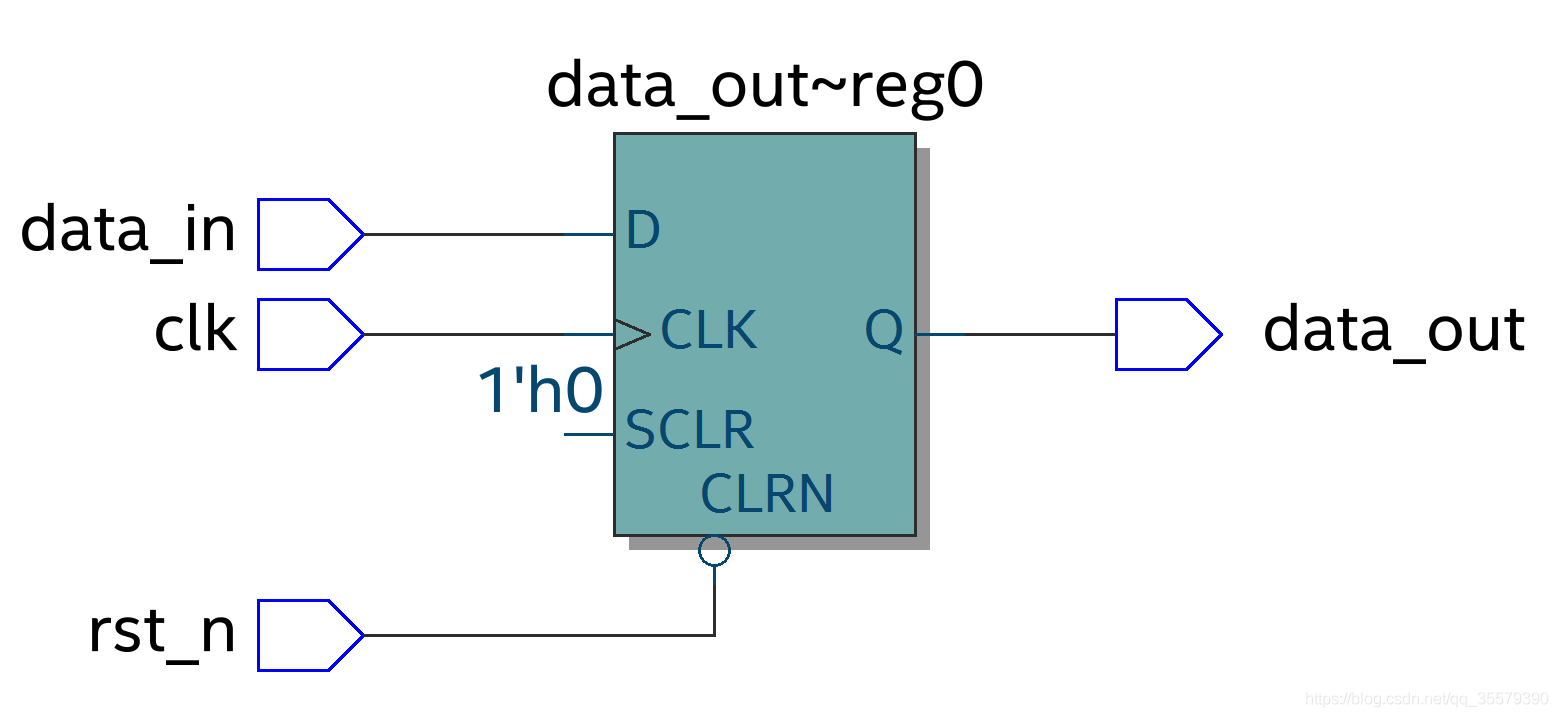

电路图: