ICC_lab总结

最近在学习后端的流程,做lab是最好不过了。但是有时候做过了lab,过了一段时间之后就会忘记,因此需要自己总结一下,加强印象。

ICC_lab1:数据设置和基本流程

数据设置:

一、数据准备:

在启动ICC之前,需要准备好下面的文件:

(1)非库文件

①ICC启动的环境设置文件:.synopsys_dc.setup文件,这个以后是需要我们书写的。

主要的设置内容有:

·禁止显示一些警告,比如创建库、布局布线过程中的一些警告;

·设置一些有用的功能操作(ICC中没有的),需要相应的设置文件

·设置一些变量开关状态(开或者关)

·设置允许记录shell的命令信息

·设置一些关联命令

·逻辑库设置(设置search_path ,target_libr,link_library,设置min库:包括标准单元库、IO库、ram库),这就需要库了

·定义一些变量,这些变量内容是不同路径下一些文件的名称

②设计的verilog门级网表:.v文件,这个文件可以通过综合完成,不需要我们生成。

③设计的平面布局图:.def文件,这个文件在本次实验中用到,这个通过布局规划得到,以后需要我们自己生成。

④时序约束文件:.sdc文件,主要是时序的约束,这个文件可以从.sdc(标准设计约束)文件得到,不需要我们书写。

⑤时序和优化控制文件:opt_ctrl.tcl文件,主要是对设计进行优化的设置,这个以后是需要我们自己书写的。

⑥检查零互联时的时序约束文件:zic_timing.tcl文件,主要是检查设计在0负载的时候,时序的情况。这个以后需要我们自己书写。

⑦创建电源和地的逻辑连接文件:derive_pg.tcl文件。顾名思义就是创建电源和地的逻辑连接;以后这个文件需要我们自己书写。

(2)参考库文件(ref文件夹),主要有:(参考库不需要我们书写,但是需要我们熟悉,因为在上面的设置中,需要用到这些库)

·普通的库文件(db):里面有标准单元库、IO单元库、RAM宏单元库等

·参考的milkyway物理库(mw_lib):里面有各种单元库(IO单元、标准单元等)文件夹

·工艺库文件夹(tech):主要是.tf工艺库文件

·寄生参数库(tlup):主要是RC参数(.tluplus库文件),用来提取寄生参数用。.map文件主要是用来映射的文件。

二、创建milkyway设计库

对于一个设计,需要根据参考可以,创建相应的milkyway库。

启动ICC后,第一件事就创建设计库

create library:主要是填写new library name(这个跟设计名称一样)、工艺库名字,不需要导入物理库;然后导入参考库ref中的库单元(ref中的sc、io、ram);勾选打开库,然后确定之后就可以完成mw_lib的创建了

三、加载/读入.v网表文件、tlu+(也就是RC参数)文件、约束以及控制文件

①确保设计库打开的情况下,导入.v文件(FILE-import design),导入过程中,需要注意设置顶层设计。

②加载tlup+寄生文件:file -- set tlu+(寄生文件在ref的寄生文件夹下面),注意需要对于的文件(max、min还是.map)

③检查物理库和逻辑库的一致性(check_library):

如果有缺失或者不匹配的标准单元库(standard cells)、IP cells、IOpads(注意不是pin),那么需要修改库,否则可以忽视警告消息。

④检查tlu+文件是否添加(check_tlu_plus_files):有三个passed才算通过。

⑤验证指定的已经加载的库(list_lib):查看.synopsys_dc.setup文件中定义的库是否正确。

⑥定义电源、地和网络之间的连接,同时检查是否有未连接的电源和地引脚:

⑦读入时序约束文件,进行时序约束

·读入时序约束之后,需要检查一下是否缺失或者不一致的约束:

·查看是否有时序例外或者时序异常:

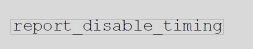

·检查是否有禁止时序分析的路径:

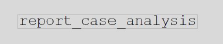

·检查约束的模式是否正确:

检查设计是否已针对特定的“模式”或“case”配置,例如“功能”与“测试”模式。 这是通过在定时分析和优化期间将控制引脚或端口约束为常量逻辑 0 或 1,而不是“硬连线”。 这有助于确认您的设计是否处于物理设计优化的正确“模式”:

·验证时钟是否正确建模:

⑧执行时序和优化脚本文件

⑨执行零互联约束:

source script/zic_timing.tcl

ZIC 模式将线网的容性负载设置为零。

执行完之后,保存相应的时序报告,可以查看相应的时序报告:

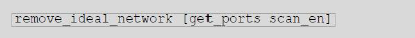

⑩删除理想的网络:

“扫描使能”信号(scan_en)被定义为一个理想的网络(见$ sdc_file),以防止综合缓冲这个信号。 删除理想的网络定义,以便在物理设计期间进行缓冲插入。

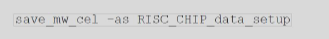

⑪保存单元设计:

基本流程:

一、设计规划

①读入布局规划文件:

这个.def在以后是需要我们进行设计生成的。

②确保标准单元不会放置在电源和接地金属路径下(此约束不是DEF 的一部分):

③保存设计规划后的设计:

二、布局

①进行布局,生成时序报告:

②布局完成之后,可以查看拥塞情况

③保存布局后的设计:

三、进行时钟树综合

①使用默认设置生成时钟树。 然而,为了允许 ICCompiler在时钟树合成期间计算实际时钟偏移,而不是结合来自约束的估计偏斜,首先去除“clockuncertainty,时钟不确定性”。 此外,启用保持时间修复:

最后那个是保持时序报告

②时钟树综合之后,可以查看时钟树的形状

③保存时钟树综合后的设计:

四、布线

①布线操作:

②布线之后,就可以进行查看各种时序报告

③保存布线后的设计:

基本的流程就是这样了。

最后,需要注意的是,当要打开某一个阶段的设计时,需要重新加载时序和控制优化:

第一个lab到这里结束了。

数据准备:各种文件、库文件-->创建milkway库-->加载/读入.v网表文件、tlu+(也就是RC参数)文件、约束以及控制文件(期间进行各种检查,执行各种文件)

基本流程:设计/布局规划-->布局-->时钟树综合-->布线