安装前的准备

安装git gcc g++

安装mpich mpich安装教程

安装cmake #ROSS 使用cmake编译

- 下载并解压得文件夹ROSS-master https://github.com/carothersc/ROSS

- 在编译之前,需要安装几个包

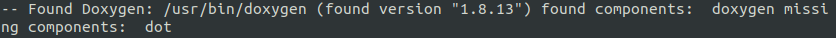

sudo apt-get install doxygen sudo apt-get install graphviz

否则会出现以下几个问题

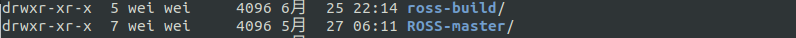

- 新建ross-build文件夹

mkdir ross-build

- 进入ross-build文件夹,编译ROSS

cd ross-build

cmake -DROSS_BUILD_MODELS=ON ../ROSS-master #注意参数DROSS_BUILD_MODELS 前面有个D - 执行命令

make

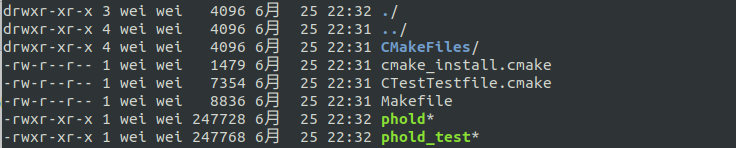

- 进入ross-build/models/文件夹,由于ROSS中自带一个小仿真示例phold,因此编译后有一个phold文件夹,里面有示例的可执行文件

如果编译成功,会有如上图的可执行文件,以下命令可以执行文件

如果编译成功,会有如上图的可执行文件,以下命令可以执行文件./phold

- 执行以下命令安装

sudo make install

##这是输出

wei@ubuntu:~/Experiment/ROSS/ross-build$ sudo make install [sudo] password for wei: [ 88%] Built target ROSS [ 94%] Built target phold_test [100%] Built target phold Install the project... -- Install configuration: "" -- Installing: /usr/local/bin/ross-config -- Installing: /usr/local/include/config.h -- Up-to-date: /usr/local/include -- Installing: /usr/local/include/hash-quadratic.h -- Installing: /usr/local/include/ross-types.h -- Installing: /usr/local/include/tw-eventq.h -- Installing: /usr/local/include/cmake -- Installing: /usr/local/include/instrumentation -- Installing: /usr/local/include/instrumentation/ross-lps -- Installing: /usr/local/include/instrumentation/ross-lps/analysis-lp.h -- Installing: /usr/local/include/instrumentation/st-instrumentation.h -- Installing: /usr/local/include/ross-inline.h -- Installing: /usr/local/include/ross-random.h -- Installing: /usr/local/include/queue -- Installing: /usr/local/include/queue/tw-queue.h -- Installing: /usr/local/include/ross.h -- Installing: /usr/local/include/ross-extern.h -- Installing: /usr/local/include/buddy.h -- Installing: /usr/local/include/network-mpi.h -- Installing: /usr/local/include/avl_tree.h -- Installing: /usr/local/include/ross-kernel-inline.h -- Installing: /usr/local/include/gvt -- Installing: /usr/local/include/gvt/mpi_allreduce.h -- Installing: /usr/local/include/tw-opts.h -- Installing: /usr/local/include/tw-timing.h -- Installing: /usr/local/include/rand-clcg4.h -- Installing: /usr/local/include/clock -- Installing: /usr/local/include/clock/aarch64.h -- Installing: /usr/local/include/clock/ppc64le.h -- Installing: /usr/local/include/clock/ia64.h -- Installing: /usr/local/include/clock/ppc.h -- Installing: /usr/local/include/clock/i386.h -- Installing: /usr/local/include/clock/bgl.h -- Installing: /usr/local/include/clock/amd64.h -- Installing: /usr/local/include/clock/bgq.h -- Installing: /usr/local/include/ross-gvt.h -- Installing: /usr/local/include/rio -- Installing: /usr/local/include/rio/io.h -- Installing: /usr/local/include/risa -- Installing: /usr/local/include/lz4.h -- Installing: /usr/local/lib/libROSS.a -- Installing: /usr/local/lib/ROSS-targets.cmake -- Installing: /usr/local/lib/ROSS-targets-noconfig.cmake -- Installing: /usr/local/lib/ROSSConfig.cmake -- Installing: /usr/local/lib/pkgconfig/ross.pc -- Installing: /usr/local/bin/phold

suang@Suang-PC:~/ross/ross-build/models/wifi$ sudo ./wifi

[sudo] suang 的密码:

./wifi

Mon Dec 10 16:50:37 2018

ROSS Revision: GITDIR-NOTFOUND

tw_net_start: Found world size to be 1

ROSS Core Configuration:

Total Nodes 1

Total Processors [Nodes (1) x PE_per_Node (1)] 1

Total KPs [Nodes (1) x KPs (16)] 16

Total LPs 8

Simulation End Time 100000.00

LP-to-PE Mapping linear

ROSS Event Memory Allocation:

Model events 125

Network events 16

Total events 140

*** START SEQUENTIAL SIMULATION ***

GVT #0: simulation 1% complete, max event queue size 64 (GVT = 1000.0962).

AVL tree size: 0

GVT #0: simulation 2% complete, max event queue size 64 (GVT = 2000.4051).

AVL tree size: 0

GVT #0: simulation 3% complete, max event queue size 64 (GVT = 3000.0585).

AVL tree size: 0

GVT #0: simulation 4% complete, max event queue size 64 (GVT = 4000.3256).

AVL tree size: 0

GVT #0: simulation 5% complete, max event queue size 64 (GVT = 5000.0213).

AVL tree size: 0

GVT #0: simulation 6% complete, max event queue size 64 (GVT = 6000.0707).

AVL tree size: 0

GVT #0: simulation 7% complete, max event queue size 64 (GVT = 7000.0323).

AVL tree size: 0

GVT #0: simulation 8% complete, max event queue size 64 (GVT = 8000.0494).

AVL tree size: 0

GVT #0: simulation 9% complete, max event queue size 64 (GVT = 9000.2333).

AVL tree size: 0

GVT #0: simulation 10% complete, max event queue size 64 (GVT = 10000.1372).

AVL tree size: 0

GVT #0: simulation 11% complete, max event queue size 64 (GVT = 11000.0290).

AVL tree size: 0

GVT #0: simulation 12% complete, max event queue size 64 (GVT = 12000.2154).

AVL tree size: 0

GVT #0: simulation 13% complete, max event queue size 64 (GVT = 13000.1736).

AVL tree size: 0

GVT #0: simulation 14% complete, max event queue size 64 (GVT = 14000.1232).

AVL tree size: 0

GVT #0: simulation 15% complete, max event queue size 64 (GVT = 15000.0390).

AVL tree size: 0

GVT #0: simulation 16% complete, max event queue size 64 (GVT = 16000.1374).

AVL tree size: 0

GVT #0: simulation 17% complete, max event queue size 64 (GVT = 17000.5183).

AVL tree size: 0

GVT #0: simulation 18% complete, max event queue size 64 (GVT = 18000.0038).

AVL tree size: 0

GVT #0: simulation 19% complete, max event queue size 64 (GVT = 19000.2315).

AVL tree size: 0

GVT #0: simulation 20% complete, max event queue size 64 (GVT = 20000.0264).

AVL tree size: 0

GVT #0: simulation 21% complete, max event queue size 64 (GVT = 21000.3946).

AVL tree size: 0

GVT #0: simulation 22% complete, max event queue size 64 (GVT = 22000.0033).

AVL tree size: 0

GVT #0: simulation 23% complete, max event queue size 64 (GVT = 23000.1237).

AVL tree size: 0

GVT #0: simulation 24% complete, max event queue size 64 (GVT = 24000.2685).

AVL tree size: 0

GVT #0: simulation 25% complete, max event queue size 64 (GVT = 25000.1103).

AVL tree size: 0

GVT #0: simulation 26% complete, max event queue size 64 (GVT = 26000.1966).

AVL tree size: 0

GVT #0: simulation 27% complete, max event queue size 64 (GVT = 27000.2675).

AVL tree size: 0

GVT #0: simulation 28% complete, max event queue size 64 (GVT = 28000.1820).

AVL tree size: 0

GVT #0: simulation 29% complete, max event queue size 64 (GVT = 29000.0163).

AVL tree size: 0

GVT #0: simulation 30% complete, max event queue size 64 (GVT = 30000.1591).

AVL tree size: 0

GVT #0: simulation 31% complete, max event queue size 64 (GVT = 31000.1583).

AVL tree size: 0

GVT #0: simulation 32% complete, max event queue size 64 (GVT = 32000.0610).

AVL tree size: 0

GVT #0: simulation 33% complete, max event queue size 64 (GVT = 33000.1511).

AVL tree size: 0

GVT #0: simulation 34% complete, max event queue size 64 (GVT = 34000.0042).

AVL tree size: 0

GVT #0: simulation 35% complete, max event queue size 64 (GVT = 35000.0206).

AVL tree size: 0

GVT #0: simulation 36% complete, max event queue size 64 (GVT = 36000.1189).

AVL tree size: 0

GVT #0: simulation 37% complete, max event queue size 64 (GVT = 37000.0366).

AVL tree size: 0

GVT #0: simulation 38% complete, max event queue size 64 (GVT = 38000.1218).

AVL tree size: 0

GVT #0: simulation 39% complete, max event queue size 64 (GVT = 39000.0318).

AVL tree size: 0

GVT #0: simulation 40% complete, max event queue size 64 (GVT = 40000.3313).

AVL tree size: 0

GVT #0: simulation 41% complete, max event queue size 64 (GVT = 41000.0872).

AVL tree size: 0

GVT #0: simulation 42% complete, max event queue size 64 (GVT = 42000.0348).

AVL tree size: 0

GVT #0: simulation 43% complete, max event queue size 64 (GVT = 43000.0212).

AVL tree size: 0

GVT #0: simulation 44% complete, max event queue size 64 (GVT = 44000.0468).

AVL tree size: 0

GVT #0: simulation 45% complete, max event queue size 64 (GVT = 45000.0369).

AVL tree size: 0

GVT #0: simulation 46% complete, max event queue size 64 (GVT = 46000.1923).

AVL tree size: 0

GVT #0: simulation 47% complete, max event queue size 64 (GVT = 47000.4953).

AVL tree size: 0

GVT #0: simulation 48% complete, max event queue size 64 (GVT = 48000.2416).

AVL tree size: 0

GVT #0: simulation 49% complete, max event queue size 64 (GVT = 49000.2224).

AVL tree size: 0

GVT #0: simulation 50% complete, max event queue size 64 (GVT = 50000.0624).

AVL tree size: 0

GVT #0: simulation 51% complete, max event queue size 64 (GVT = 51000.0855).

AVL tree size: 0

GVT #0: simulation 52% complete, max event queue size 64 (GVT = 52000.3024).

AVL tree size: 0

GVT #0: simulation 53% complete, max event queue size 64 (GVT = 53000.0489).

AVL tree size: 0

GVT #0: simulation 54% complete, max event queue size 64 (GVT = 54000.3475).

AVL tree size: 0

GVT #0: simulation 55% complete, max event queue size 64 (GVT = 55000.0670).

AVL tree size: 0

GVT #0: simulation 56% complete, max event queue size 64 (GVT = 56000.2891).

AVL tree size: 0

GVT #0: simulation 57% complete, max event queue size 64 (GVT = 57000.0279).

AVL tree size: 0

GVT #0: simulation 58% complete, max event queue size 64 (GVT = 58000.0093).

AVL tree size: 0

GVT #0: simulation 59% complete, max event queue size 64 (GVT = 59000.1050).

AVL tree size: 0

GVT #0: simulation 60% complete, max event queue size 64 (GVT = 60000.0675).

AVL tree size: 0

GVT #0: simulation 61% complete, max event queue size 64 (GVT = 61000.2059).

AVL tree size: 0

GVT #0: simulation 62% complete, max event queue size 64 (GVT = 62000.1262).

AVL tree size: 0

GVT #0: simulation 63% complete, max event queue size 64 (GVT = 63000.1914).

AVL tree size: 0

GVT #0: simulation 64% complete, max event queue size 64 (GVT = 64000.0650).

AVL tree size: 0

GVT #0: simulation 65% complete, max event queue size 64 (GVT = 65000.0662).

AVL tree size: 0

GVT #0: simulation 66% complete, max event queue size 64 (GVT = 66000.2696).

AVL tree size: 0

GVT #0: simulation 67% complete, max event queue size 64 (GVT = 67000.5576).

AVL tree size: 0

GVT #0: simulation 68% complete, max event queue size 64 (GVT = 68000.1615).

AVL tree size: 0

GVT #0: simulation 69% complete, max event queue size 64 (GVT = 69000.0314).

AVL tree size: 0

GVT #0: simulation 70% complete, max event queue size 64 (GVT = 70000.0277).

AVL tree size: 0

GVT #0: simulation 71% complete, max event queue size 64 (GVT = 71000.0134).

AVL tree size: 0

GVT #0: simulation 72% complete, max event queue size 64 (GVT = 72000.0383).

AVL tree size: 0

GVT #0: simulation 73% complete, max event queue size 64 (GVT = 73000.0005).

AVL tree size: 0

GVT #0: simulation 74% complete, max event queue size 64 (GVT = 74000.4647).

AVL tree size: 0

GVT #0: simulation 75% complete, max event queue size 64 (GVT = 75000.2984).

AVL tree size: 0

GVT #0: simulation 76% complete, max event queue size 64 (GVT = 76000.0145).

AVL tree size: 0

GVT #0: simulation 77% complete, max event queue size 64 (GVT = 77000.0706).

AVL tree size: 0

GVT #0: simulation 78% complete, max event queue size 64 (GVT = 78000.3715).

AVL tree size: 0

GVT #0: simulation 79% complete, max event queue size 64 (GVT = 79000.1613).

AVL tree size: 0

GVT #0: simulation 80% complete, max event queue size 64 (GVT = 80000.3776).

AVL tree size: 0

GVT #0: simulation 81% complete, max event queue size 64 (GVT = 81000.2426).

AVL tree size: 0

GVT #0: simulation 82% complete, max event queue size 64 (GVT = 82000.3880).

AVL tree size: 0

GVT #0: simulation 83% complete, max event queue size 64 (GVT = 83000.1023).

AVL tree size: 0

GVT #0: simulation 84% complete, max event queue size 64 (GVT = 84000.1727).

AVL tree size: 0

GVT #0: simulation 85% complete, max event queue size 64 (GVT = 85000.0687).

AVL tree size: 0

GVT #0: simulation 86% complete, max event queue size 64 (GVT = 86000.1371).

AVL tree size: 0

GVT #0: simulation 87% complete, max event queue size 64 (GVT = 87000.0317).

AVL tree size: 0

GVT #0: simulation 88% complete, max event queue size 64 (GVT = 88000.0129).

AVL tree size: 0

GVT #0: simulation 89% complete, max event queue size 64 (GVT = 89000.0214).

AVL tree size: 0

GVT #0: simulation 90% complete, max event queue size 64 (GVT = 90000.0014).

AVL tree size: 0

GVT #0: simulation 91% complete, max event queue size 64 (GVT = 91000.0680).

AVL tree size: 0

GVT #0: simulation 92% complete, max event queue size 64 (GVT = 92000.3160).

AVL tree size: 0

GVT #0: simulation 93% complete, max event queue size 64 (GVT = 93000.1190).

AVL tree size: 0

GVT #0: simulation 94% complete, max event queue size 64 (GVT = 94000.1758).

AVL tree size: 0

GVT #0: simulation 95% complete, max event queue size 64 (GVT = 95000.0055).

AVL tree size: 0

GVT #0: simulation 96% complete, max event queue size 64 (GVT = 96000.0239).

AVL tree size: 0

GVT #0: simulation 97% complete, max event queue size 64 (GVT = 97001.0282).

AVL tree size: 0

GVT #0: simulation 98% complete, max event queue size 64 (GVT = 98000.0179).

AVL tree size: 0

GVT #0: simulation 99% complete, max event queue size 64 (GVT = 99000.2030).

AVL tree size: 0

*** END SIMULATION ***

LP 0 had 4696 / 39957 failed Station to Access Point packets

LP 0 had 14243 / 39954 failed Access Point to Station packets

LP 1 had 4688 / 39930 failed Station to Access Point packets

LP 1 had 14242 / 39925 failed Access Point to Station packets

LP 2 had 4804 / 39905 failed Station to Access Point packets

LP 2 had 14191 / 39901 failed Access Point to Station packets

LP 3 had 4763 / 40009 failed Station to Access Point packets

LP 3 had 14238 / 40002 failed Access Point to Station packets

LP 4 had 4904 / 40114 failed Station to Access Point packets

LP 4 had 14209 / 40112 failed Access Point to Station packets

LP 5 had 4702 / 39867 failed Station to Access Point packets

LP 5 had 14180 / 39864 failed Access Point to Station packets

LP 6 had 4801 / 39972 failed Station to Access Point packets

LP 6 had 14440 / 39968 failed Access Point to Station packets

LP 7 had 4609 / 40009 failed Station to Access Point packets

LP 7 had 14251 / 40006 failed Access Point to Station packets

: Running Time = 0.6311 seconds

TW Library Statistics:

Total Events Processed 639431

Events Aborted (part of RBs) 0

Events Rolled Back 0

Event Ties Detected in PE Queues 0

Efficiency 100.00 %

Total Remote (shared mem) Events Processed 0

Percent Remote Events 0.00 %

Total Remote (network) Events Processed 0

Percent Remote Events 0.00 %

Total Roll Backs 0

Primary Roll Backs 0

Secondary Roll Backs 0

Fossil Collect Attempts 0

Total GVT Computations 0

Net Events Processed 639431

Event Rate (events/sec) 1013205.6

Total Events Scheduled Past End Time 64

TW Memory Statistics:

Events Allocated 141

Memory Allocated 82

Memory Wasted 429

TW Data Structure sizes in bytes (sizeof):

PE struct 640

KP struct 144

LP struct 136

LP Model struct 328

LP RNGs 80

Total LP 544

Event struct 152

Event struct with Model 160

TW Clock Cycle Statistics (MAX values in secs at 1.0000 GHz):

Initialization 0.0044

Priority Queue (enq/deq) 0.3426

AVL Tree (insert/delete) 0.0000

LZ4 (de)compression 0.0000

Buddy system 0.0000

Event Processing 0.0000

Event Cancel 0.0000

Event Abort 0.0000

GVT 0.0000

Fossil Collect 0.0000

Primary Rollbacks 0.0000

Network Read 0.0000

Other Network 0.0000

Instrumentation (computation) 0.0000

Instrumentation (write) 0.0000

Total Time (Note: Using Running Time above for Speedup) 2.1410

TW GVT Statistics: MPI AllReduce

GVT Interval 16

GVT Real Time Interval (cycles) 0

GVT Real Time Interval (sec) 0.00000000

Batch Size 16

Forced GVT 0

Total GVT Computations 0

Total All Reduce Calls 0

Average Reduction / GVT -nan

suang@Suang-PC:~/ross/r