lab1——编写模拟16bit-BCD码到14bit二进制表示的.v文件

1.编写verilog文件,注意基本语法、变量类型等等。如:

input 定义时不指明类型,output应指明(如reg),注意数据类型能否作为左值/右值;

定义reg变量时,注意可存储范围(如reg [2:0] i; 则i只能存放0-4的数);

注意并行性,for循环不可条件中断、跳出循环;

2.在windows下的cmd窗口调用iverilog.exe,注意文件位置与程序位置,必要时补全路径biniverilog...,对GTKwave模拟程序也同理

3.xxx_tb.v是一种惯用命名方式,tb代指testbench平台,有一些特殊语法,如$dumpfile("filename.vcd"),$dumpvar(option,file_pointer)(注:option=0,1,2...,是可选引用模块的层次,0代表引用所有该文件直接和间接定义的module)

4.iverilog命令行程序-o编译.vpp文件时,注意在命令行里包括所有需要引用的xxx.v文件和xxx_tb.v文件(一般需要生成的.vpp文件在最前,暂时不清楚其他文件的顺序在存在模块相互引用的情况下是否会影响编译),并检查xxx_tb.v文件和源文件中的模块名称,否则会报错"these modules were missing: ..."

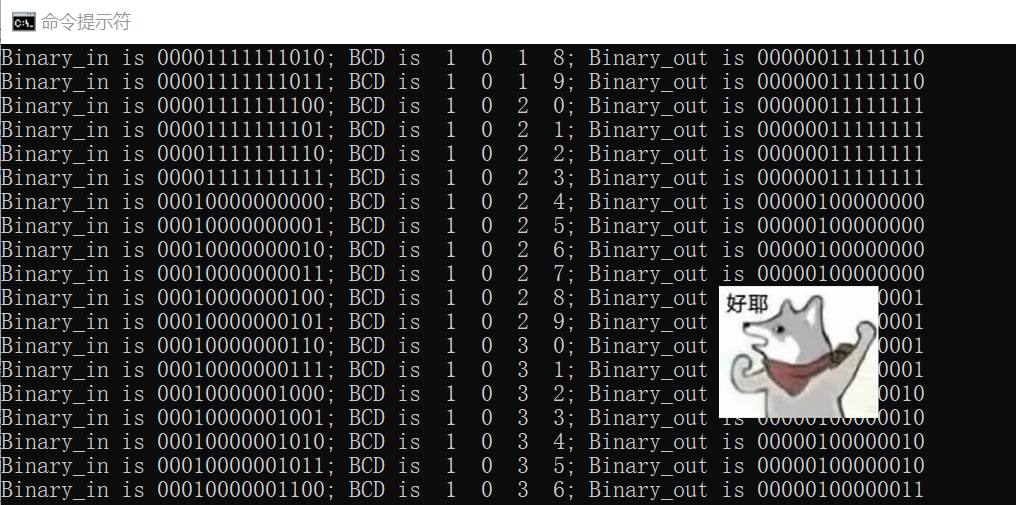

——lab1模拟结果:

TBC