这篇讲的是使用 verilog 硬件描述语言编写一个 3 - 8 译码器。

3 - 8 译码器是一个简单的组合逻辑,用于实现并转串,其输入输出关系如下:

| 输入 | 输出 |

-----------------

000 --> 0000_0001

001 --> 0000_0010

010 --> 0000_0100

011 --> 0000_1000

100 --> 0001_0000

101 --> 0010_0000

110 --> 0100_0000

111 --> 1000_0000

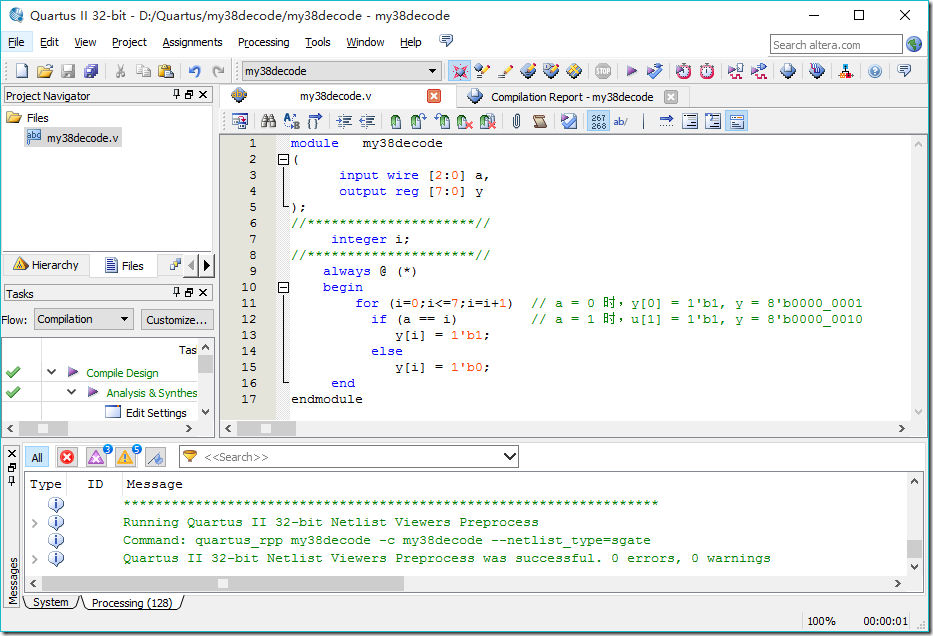

新建工程,并新建如下的代码的 verilog HDL 文件

module my38decode ( input wire [2:0] a, output reg [7:0] y ); //*********************// integer i; //*********************// always @ (*) begin for (i=0;i<=7;i=i+1) // a = 0 时,y[0] = 1'b1, y = 8'b0000_0001 if (a == i) // a = 1 时,u[1] = 1'b1, y = 8'b0000_0010 y[i] = 1'b1; else y[i] = 1'b0; end

endmodule

这段代码其实相当抽象(循环变量操作下标),但好在综合工具还是能够理解我们的用意。

建好的工程如下图:

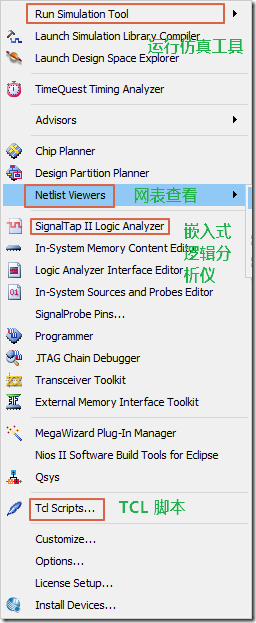

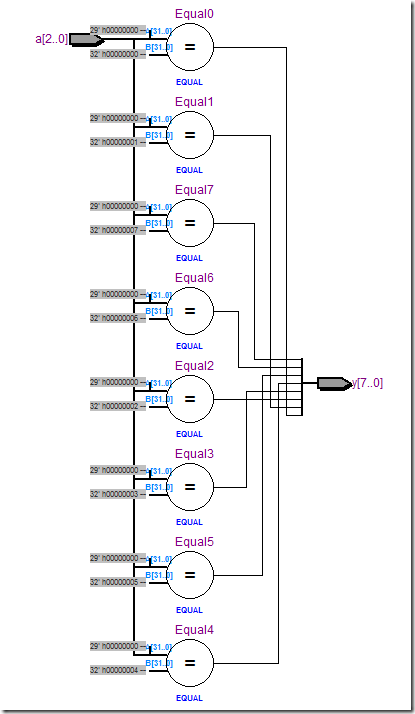

可以在 Tool --> Netlist Viewers --> RTL Viewer 查看生成的 RTL 网表文件。

下图为 Tool 菜单和生成的网表文件。可以看出我们写的代码生成了几个比较器,我们的输入信号被扩大至 32 位(前29位自动填 0);比较器的 B 端口连接的是一些常量,当 32 位比较器在输入相等时输出 1,不等则输出 0;7 个比较器输出分别连接到 y 的 7 个引脚上。如图,综合器在 RTL(寄存器传输级)成功的实现了我们的要求。