FPGA设计入门

基于Quartus-II软件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。软件基于quartusII 13.0版本,开发板基于Intel DE2-115。

一、输入原理图实现1位加法器

创建工程过程

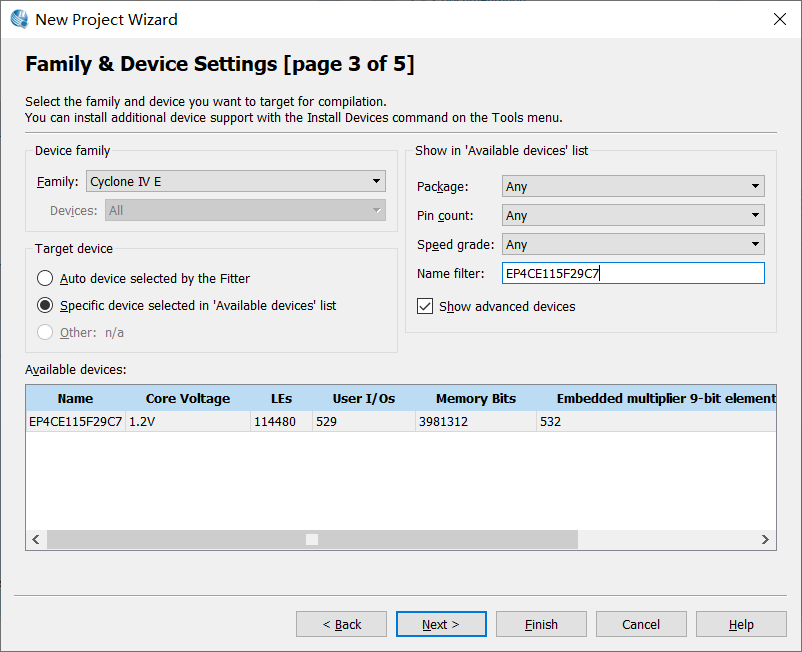

启动 Quartus II 软件,选择File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

1.绘制过程实现

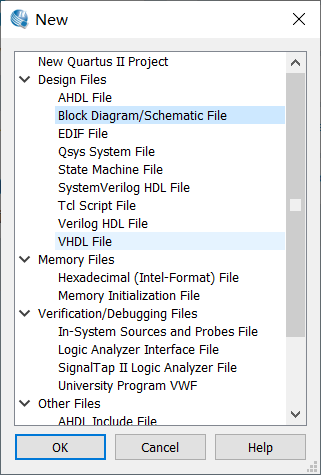

首先选择File->New,进入后选择Block Diagram/Schematic File

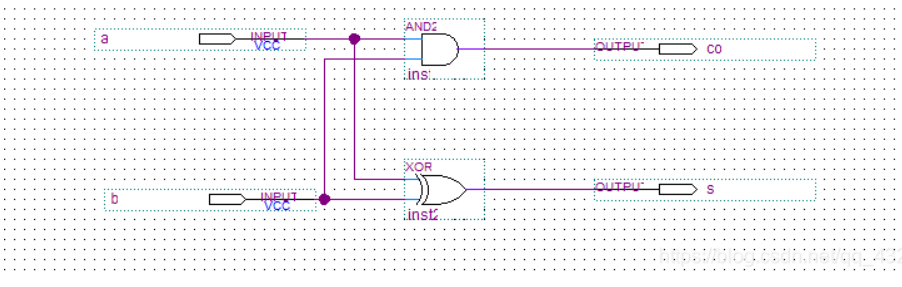

2.添加元件,完成效果

3.保存文件,并编译

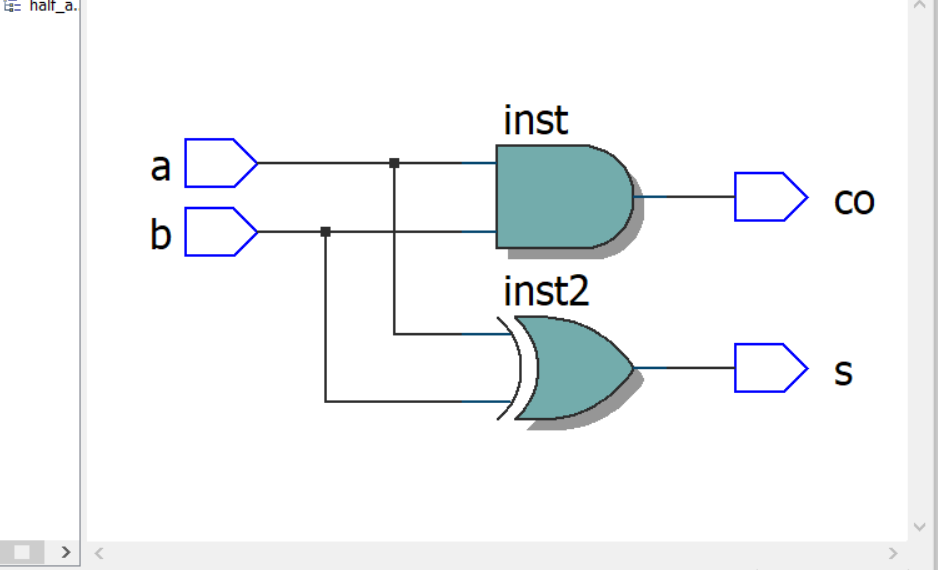

通过tool->Netlist Viewers->RTL Viewer,查看电路图

4.仿真实现

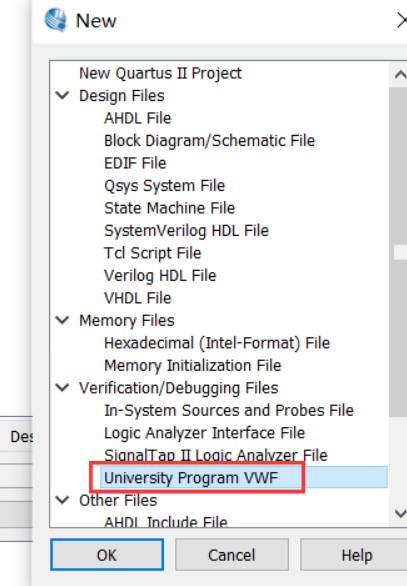

创建一个向量波形文件,选择菜单项 File→New->VWF

5.添加编辑信号,保存文件并启动功能仿真,进行仿真配置,选择tool->launch simulation library complier

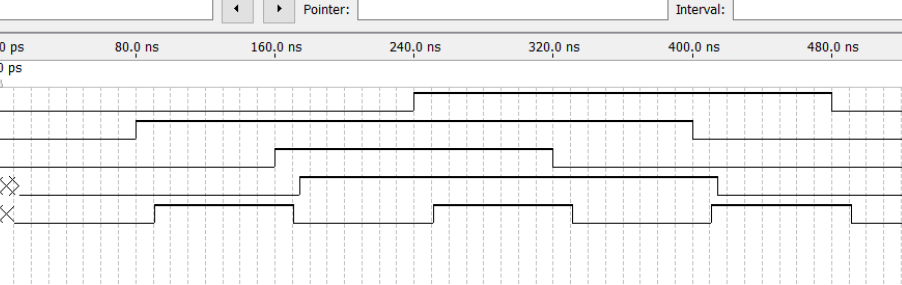

功能仿真结果

时序仿真结果

二、全加器原理图实现

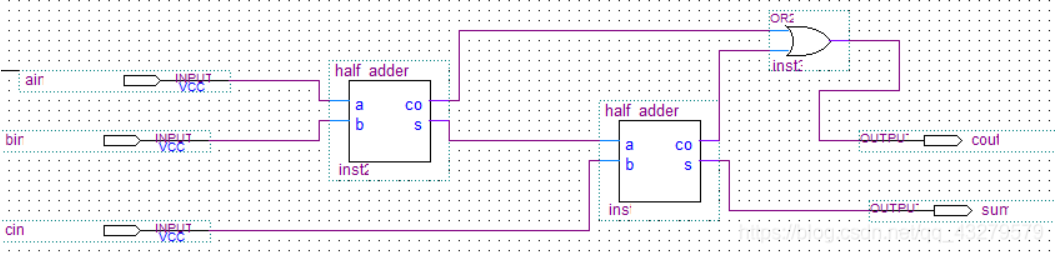

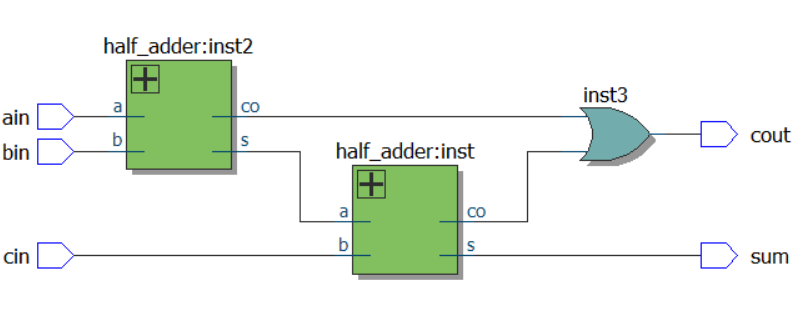

利用半加器元件实现全加器

1.绘制过程实现

首先选择File->New,进入后选择Block Diagram/Schematic File

2.选择元件添加输出效果图

3.保存文件,并编译

通过tool->Netlist Viewers->RTL Viewer,查看电路图

4.仿真实现

创建一个向量波形文件,选择菜单项 File→New->VWF

功能仿真结果

时序仿真结果