用你熟悉的设计方式设计一个可预置初值的7进制循环计数器,15进制的呢?

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Engineer: connor jiao // Create Date: 11:48 2020/6/16 // Design Name: // Module Name: // Function : 用你熟悉的设计方式设计一个可预置初值的7进制循环计数器,15进制的呢? // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module counter77( clk, rst_n, set, data, out ); input clk; input rst_n; input set; input [2:0]data; output reg[2:0]out; reg [2:0]cnt; always@(posedge clk or negedge rst_n) begin if(!rst_n)begin cnt<=0; end else if(set) cnt<=data; else cnt<=cnt+1'b1; end always@(posedge clk or negedge rst_n) begin if(!rst_n) out<=0; else out<=cnt; end endmodule

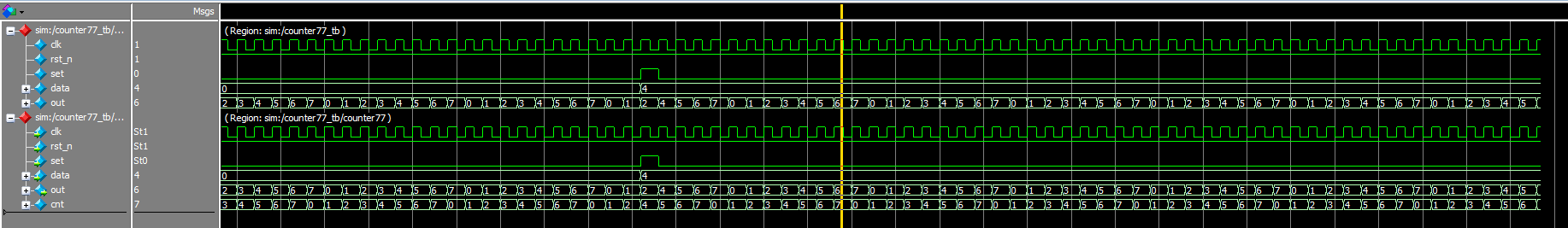

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Engineer: connor jiao // Create Date: // Design Name: // Module Name: // Function : // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module counter77_tb(); reg clk; reg rst_n; reg set; reg [2:0]data; wire [2:0]out; counter77 counter77( .clk(clk), .rst_n(rst_n), .set(set), .data(data), .out(out) ); initial clk=0; always #2 clk=~clk; initial begin rst_n=0; set=0; data=0; #201; rst_n=1; #201; set=1; data=4; #4; set=0; #201; $stop; end endmodule