在FPGA设计中,经常要对外部输入的信号捕捉上升沿。

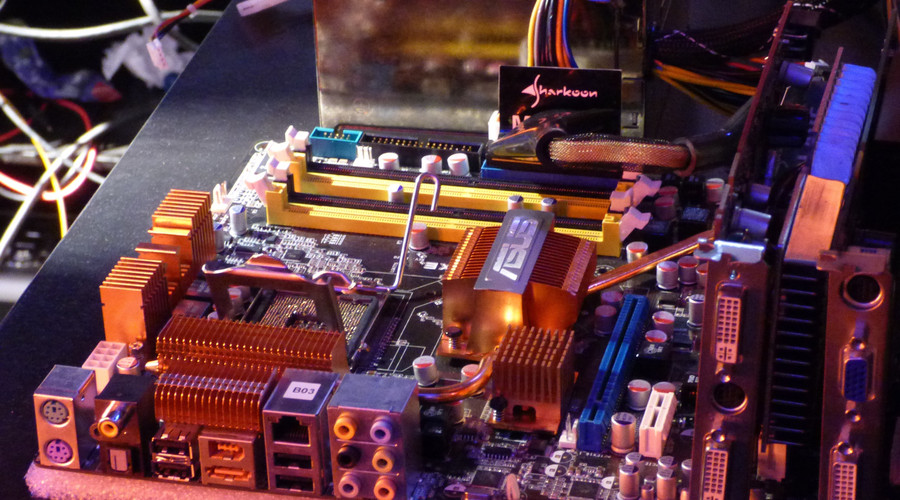

在某些设计中,外部输入信号为方波信号,由比较器输出。

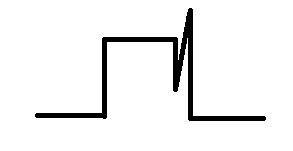

如上图,比较器输出方波后,电路设计欠佳,产生抖动,下降沿产生毛刺,如果FPGA逻辑设计不好,容易在方波下降沿时再次捕捉到上升沿。

在电路无法更改的情况下,只能更改FPGA逻辑设计,过滤毛刺。

在捕捉边沿中通常使用以下逻辑:

时序逻辑:

always@(posedge sys_clk)

begin

reg1 <= rising_in;

reg2 <= reg1;

end

组合逻辑:

assign rising_cap = reg1 & (~reg2);

方案一:

通过降频采集外部输入信号:

always@(posedge sys_clk)

begin

if(div_clk)

begin

reg1 <= rising_in;

reg2 <= reg1;

end

end

将sys_clk分频到div_clk,注意分频时要满足采样定理。通过降频,过滤毛刺。

方案二:

在某些设计中,由于使用方波上升沿进行完全同步,而且整个系统使用sys_clk,所以不能进行分频设计。

对信号进行多次采样,过滤毛刺。

always@(posedge sys_clk)

begin

reg1 <= rising_in;

reg2 <= reg1;

reg3 <= reg2;

reg4 <= reg3;

reg5 <= reg4;

reg6 <= reg5;

reg7 <= reg6;

reg8 <= reg7;

end

组合逻辑:

assign rising_cap = reg1 & reg2 & reg3 & reg4 & (~& reg5)

& (~& reg6) & (~& reg7) & (~& reg8);

在方波上升沿很陡的情况下,可使用上述方式,方波上升沿的上升时间可由电路电阻改变。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间