原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

简介

本文主要介绍verilog基础模块,夯实基础,对深入学习FPGA会有很大帮助。

数据类型

常量

整数:整数可以用二进制b或B,八进制o或O,十进制d或D,十六进制h或H表示,例如, 8’b00001111表示8位位宽的二进制整数,4’ha表示4位位宽的十六进制整数。

X和Z:X代表不定值,z代表高阻值,例如,5’b00x11,第三位不定值,3’b00z表示最低位为高阻值。

下划线:在位数过长时可以用来分割位数,提高程序可读性,如8’b0000_1111

参数parameter: parameter可以用标识符定义常量,运用时只使用标识符即可,提高可读性及维护性,如定义parameter width = 8 ; 定义寄存器reg [width-1:0] a; 即定义了8位宽度的寄存器。

参数的传递:在一个模块中如果有定义参数,在其他模块调用此模块时可以传递参数,并可以修改参数,如下所示,在module后用#()表示。

例如定义模块如下调用模块

module rom

#(

parameter depth =15,

parameter width =8

)

(

input[depth-1:0] addr ,

input[width-1:0] data ,

output result

);

endmodule

module top();

wire[31:0] addr ;

wire[15:0] data ;

wire result ;

rom

#(

.depth(32),

.width(16)

)

r1

(

.addr(addr),

.data(data),

.result(result)

);

endmodule

Parameter可以用于模块间的参数传递,而localparam仅用于本模块内使用,不能用于参数传递。Localparam多用于状态机状态的定义。

变量

变量是指程序运行时可以改变其值的量,下面主要介绍几个常用了变量类型

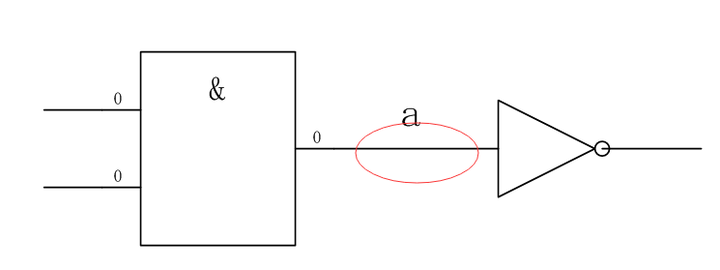

1.Wire 型

Wire 类型变量,也叫网络类型变量,用于结构实体之间的物理连接,如门与门之间,不能储存值,用连续赋值语句assign赋值,定义为wire [n-1:0] a ; 其中n代表位宽,如定义wire a ; assign a = b ; 是将b的结点连接到连线a上。如下图所示,两个实体之间的连线即是wire类型变量。

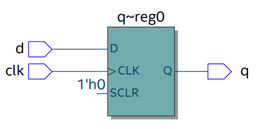

2.Reg 型

Reg 类型变量,也称为寄存器变量,可用来储存值,必须在always语句里使用。其定义为

reg [n-1:0] a ; 表示n位位宽的寄存器,如reg [7:0] a; 表示定义8位位宽的寄存器a。如下所示定义了寄存器q,生成的电路为时序逻辑,右图为其结构,为D触发器。

module top(d, clk, q);

input d ;

input clk ;

outputreg q ;

always@(posedge clk)

begin

q <= d ;

end

endmodule

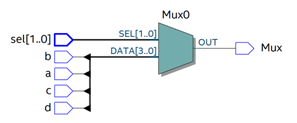

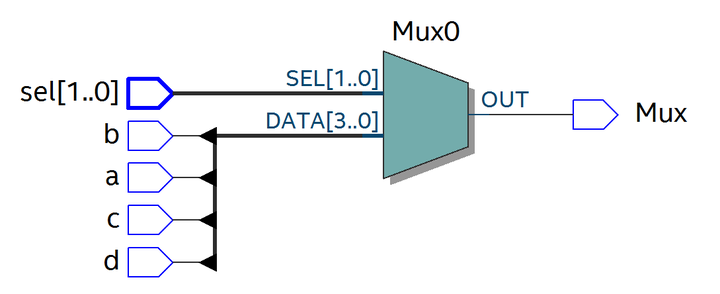

也可以生成组合逻辑,如数据选择器,敏感信号没有时钟,定义了reg Mux,最终生成电路为组合逻辑。

module top(a, b, c, d, sel, Mux);

input a ;

input b ;

input c ;

input d ;

input[1:0] sel ;

outputreg Mux ;

always@(sel or a or b or c or d)

begin

case(sel)

2'b00: Mux = a ;

2'b01: Mux = b ;

2'b10: Mux = c ;

2'b11: Mux = d ;

endcase

end

endmodule

3.Memory型

可以用memory类型来定义RAM,ROM等存储器,其结构为reg [n-1:0] 存储器名[m-1:0],意义为m个n位宽度的寄存器。例如,reg [7:0] ram [255:0]表示定义了256个8位寄存器,256也即是存储器的深度,8为数据宽度。

运算符

运算符可分为以下几类:

- 算术运算符(+,-,*,/,%)

- 赋值运算符(=,<=)

- 关系运算符(>,<,>=,<=,==,!=)

- 逻辑运算符(&&,||,!)

- 条件运算符(?:)

- 位运算符(~,|,^,&,^~)

- 移位运算符(<<,>>)

- 拼接运算符({ })

算术运算符

“+”(加法运算符),”-“(减法运算符),”*”(乘法运算符),”/”(除法运算符,如7/3 =2),“%”(取模运算符,也即求余数,如7%3=1,余数为1)

赋值运算符

“=”阻塞赋值,”<=”非阻塞赋值。阻塞赋值为执行完一条赋值语句,再执行下一条,可理解为顺序执行,而且赋值是立即执行;非阻塞赋值可理解为并行执行,不考虑顺序,在always块语句执行完成后,才进行赋值。如下面的阻塞赋值:

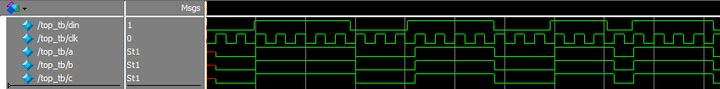

代码如下:激励文件如下

module top(din,a,b,c,clk);

input din;

input clk;

outputreg a,b,c;

always@(posedge clk)

begin

a = din;

b = a;

c = b;

end

endmodule

`timescale1 ns/1 ns

module top_tb();

reg din ;

reg clk ;

wire a,b,c ;

initial

begin

din =0;

clk =0;

forever

begin

#({$random}%100)

din =~din ;

end

end

always#10 clk =~clk ;

top t0(.din(din),.a(a),.b(b),.c(c),.clk(clk));

endmodule

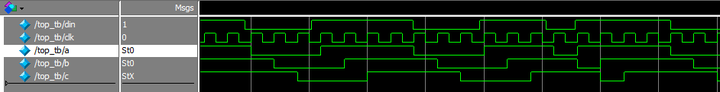

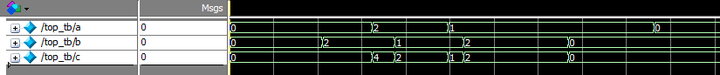

可以从仿真结果看到,在clk的上升沿,a的值等于din,并立即赋给b,b的值赋给c。

如果改为非阻塞赋值,仿真结果如下,在clk上升沿,a的值没有立即赋值给b,b为a原来的值,同样,c为b原来的值

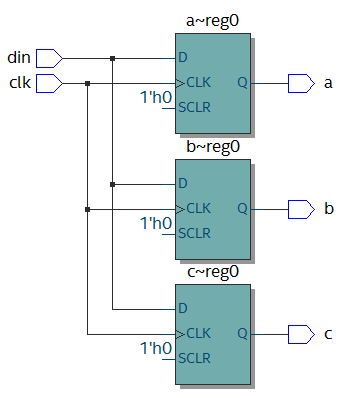

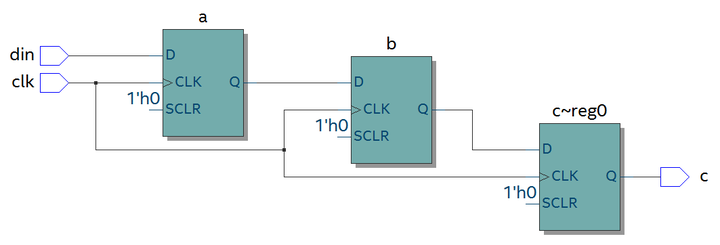

可以从两者的RTL图看出明显不同:

阻塞赋值RTL图非阻塞赋值RTL图

一般情况下,在时序逻辑电路中使用非阻塞赋值,可避免仿真时出现竞争冒险现象;在组合逻辑中使用阻塞赋值,执行赋值语句后立即改变;在assign语句中必须用阻塞赋值。

- 关系运算符

用于表示两个操作数之间的关系,如a>b,a<b,多用于判断条件,例如:

| If (a>=b) q <=1’b1 ; else q <= 1’b0 ;表示如果a的值大于等于b的值,则q的值为1,否则q的值为0 |

- 逻辑运算符

“&&”(两个操作数逻辑与),”||”(两个操作数逻辑或),”!”(单个操作数逻辑非)例如:

If (a>b && c <d) 表示条件为a>b并且c<d; if (!a)表示条件为a的值不为1,也就是0。

- 条件运算符

“?:”为条件判断,类似于if else,例如assign a = (i>8)?1’b1:1’b0 ;判断i的值是否大于8,如果大于8则a的值为1,否则为0。

- 位运算符

“~”按位取反,”|”按位或,”^”按位异或,”&”按位与,”^”按位同或,除了”~”只需要一个操作数外,其他几个都需要两个操作数,如a&b,a|b。具体应用在后面的组合逻辑一节中有讲解。

- 移位运算符

“<<”左移位运算符,”>>”右移位运算符,如a<<1表示,向左移1位,a>>2,向右移两位。

- 拼接运算符

“{ }”拼接运算符,将多个信号按位拼接,如{a[3:0], b[1:0]},将a的低4位,b的低2位拼接成6位数据。另外,{n{a[3:0]}}表示将n个a[3:0]拼接,{n{1’b0}}表示n位的0拼接。如{8{1’b0}}表示为8’b0000_0000.

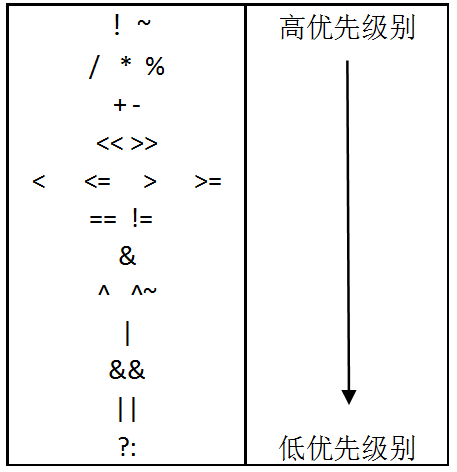

- 优先级别

各种运算符的优先级别如下:

组合逻辑

本节主要介绍组合逻辑,组合逻辑电路的特点是任意时刻的输出仅仅取决于输入信号,输入信号变化,输出立即变化,不依赖于时钟。

- 与门

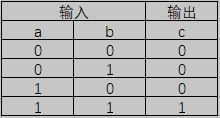

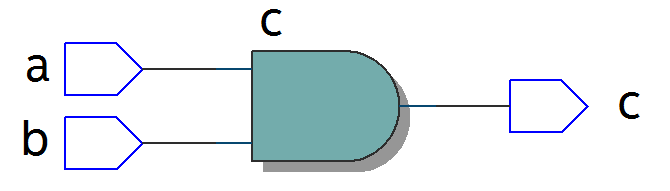

在verilog中以“&”表示按位与,如c=a&b,真值表如下,在a和b都等于1时结果才为1,RTL表示如右图

代码实现如下:激励文件如下:

module top(a, b, c);

input a ;

input b ;

output c ;

assign c = a & b ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

reg b ;

wire c ;

initial

begin

a =0;

b =0;

forever

begin

#({$random}%100)

a =~a ;

#({$random}%100)

b =~b ;

end

end

top t0(.a(a),.b(b),.c(c));

endmodule

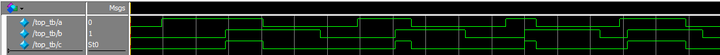

仿真结果如下:

如果a和b的位宽大于1,例如定义input [3:0] a, input [3:0]b,那么a&b则指a与b的对应位相与。如a[0]&b[0],a[1]&b[1]。

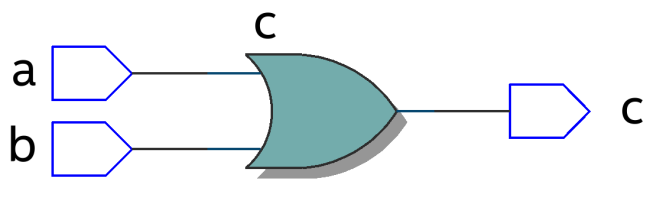

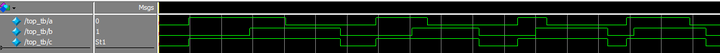

- 或门

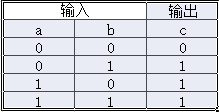

在verilog中以“|”表示按位或,如c = a|b , 真值表如下,在a和b都为0时结果才为0。

代码实现如下:激励文件如下

module top(a, b, c);

input a ;

input b ;

output c ;

assign c = a | b ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

reg b ;

wire c ;

initial

begin

a =0;

b =0;

forever

begin

#({$random}%100)

a =~a ;

#({$random}%100)

b =~b ;

end

end

top t0(.a(a),.b(b),.c(c));

endmodule

仿真结果如下:

同理,位宽大于1,则是按位或。

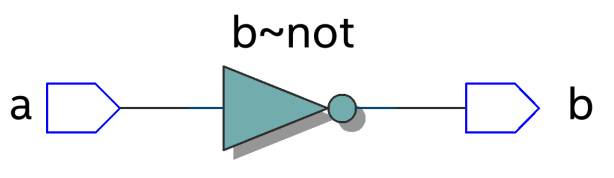

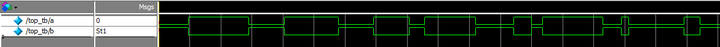

- 非门

在verilog中以“~”表示按位取反,如b=~a,真值表如下,b等于a的相反数。

代码实现如下:激励文件如下:

module top(a, b);

input a ;

output b ;

assign b =~a ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

wire b ;

initial

begin

a =0;

forever

begin

#({$random}%100)

a =~a ;

end

end

top t0(.a(a),.b(b));

endmodule

仿真结果如如下:

- 异或

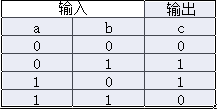

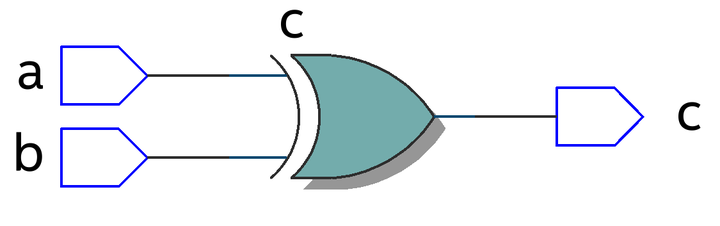

在verilog中以“^”表示异或,如c= a^b ,真值表如下,当a和b相同时,输出为0。

代码实现如下:激励文件如下:

module top(a, b, c);

input a ;

input b ;

output c ;

assign c = a ^ b ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

reg b ;

wire c ;

initial

begin

a =0;

b =0;

forever

begin

#({$random}%100)

a =~a ;

#({$random}%100)

b =~b ;

end

end

top t0(.a(a),.b(b),.c(c));

endmodule

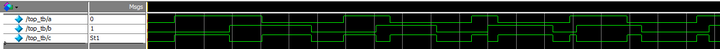

仿真结果如下:

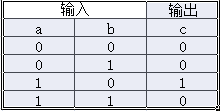

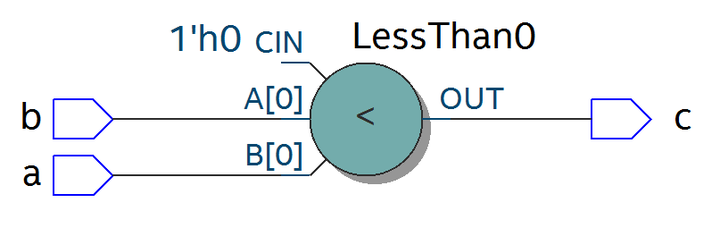

- 比较器

在verilog中以大于“>”,等于”==”,小于”<”,大于等于”>=”,小于等于”<=”,不等于”!=”表示,以大于举例,如c= a > b ;表示如果a大于b,那么c的值就为1,否则为0。真值表如下:

代码实现如下:激励文件如下:

module top(a, b, c);

input a ;

input b ;

output c ;

assign c = a > b ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

reg b ;

wire c ;

initial

begin

a =0;

b =0;

forever

begin

#({$random}%100)

a =~a ;

#({$random}%100)

b =~b ;

end

end

top t0(.a(a),.b(b),.c(c));

endmodule

仿真结果如下:

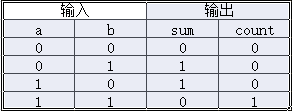

- 半加器

半加器和全加器是算术运算电路中的基本单元,由于半加器不考虑从低位来的进位,所以称之为半加器,sum表示相加结果,count表示进位,真值表可表示如下:

可根据真值表写出代码如下:激励文件如下:

module top(a, b, sum, count);

input a ;

input b ;

output sum ;

output count ;

assign sum = a ^ b ;

assign count = a & b ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

reg b ;

wire sum ;

wire count ;

initial

begin

a =0;

b =0;

forever

begin

#({$random}%100)

a =~a ;

#({$random}%100)

b =~b ;

end

end

top t0(.a(a),.b(b),

.sum(sum),.count(count));

endmodule

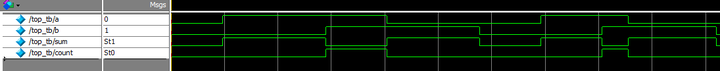

仿真结果如下:

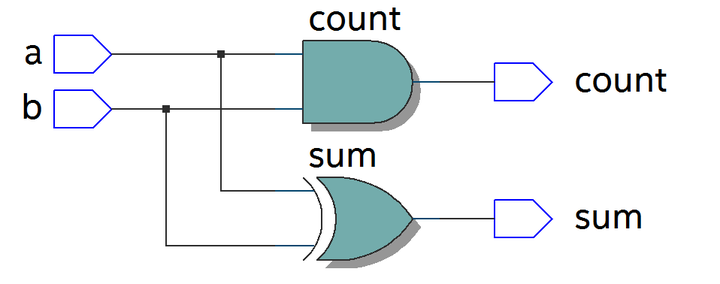

- 全加器

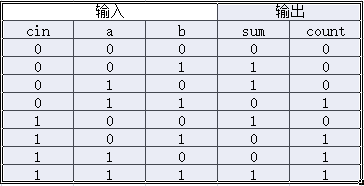

而全加器需要加上低位来的进位信号cin,真值表如下:

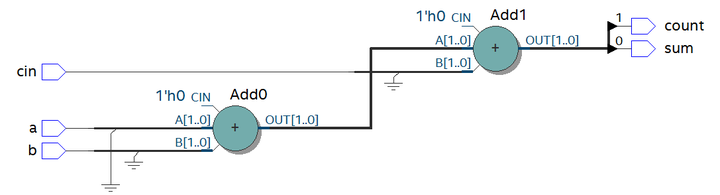

代码如下:激励文件如下:

module top(cin, a, b, sum, count);

input cin ;

input a ;

input b ;

output sum ;

output count ;

assign{count,sum}= a + b + cin ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

reg b ;

reg cin ;

wire sum ;

wire count ;

initial

begin

a =0;

b =0;

cin =0;

forever

begin

#({$random}%100)

a =~a ;

#({$random}%100)

b =~b ;

#({$random}%100)

cin =~cin ;

end

end

top t0(.cin(cin),.a(a),.b(b),

.sum(sum),.count(count));

endmodule

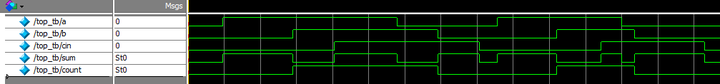

仿真结果如下:

- 乘法器

乘法的表示也很简单,利用”*”即可,如a*b,举例代码如下:

module top(a, b, c);

input[1:0] a ;

input[1:0] b ;

output[3:0] c ;

assign c = a * b ;

endmodule

`timescale1 ns/1 ns

module top_tb();

reg[1:0]a ;

reg[1:0]b ;

wire[3:0]c ;

initial

begin

a =0;

b =0;

forever

begin

#({$random}%100)

a =~a ;

#({$random}%100)

b =~b ;

end

end

top t0(.a(a),.b(b),.c(c));

endmodule

仿真结果如下:

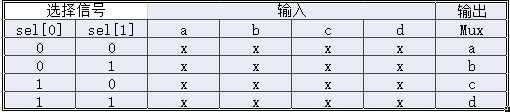

- 数据选择器

在verilog中经常会用到数据选择器,通过选择信号,选择不同的输入信号输出到输出端,如下图真值表,四选一数据选择器,sel[1:0]为选择信号,a,b,c,d为输入信号,Mux为输出信号。

代码如下:激励文件如下:

module top(a, b, c, d, sel, Mux);

input a ;

input b ;

input c ;

input d ;

input[1:0] sel ;

outputreg Mux ;

always@(sel or a or b or c or d)

begin

case(sel)

2'b00: Mux = a ;

2'b01: Mux = b ;

2'b10: Mux = c ;

2'b11: Mux = d ;

endcase

end

endmodule

`timescale1 ns/1 ns

module top_tb();

reg a ;

reg b ;

reg c ;

reg d ;

reg[1:0] sel ;

wire Mux ;

initial

begin

a =0;

b =0;

c =0;

d =0;

forever

begin

#({$random}%100)

a ={$random}%3;

#({$random}%100)

b ={$random}%3;

#({$random}%100)

c ={$random}%3;

#({$random}%100)

d ={$random}%3;

end

end

initial

begin

sel =2'b00;

#2000 sel =2'b01;

#2000 sel =2'b10;

#2000 sel =2'b11;

end

top

t0(.a(a),.b(b),.c(c),.d(d