CPU高速缓存

从80486在CPU内部新增了高速缓存,他是内存的缓存

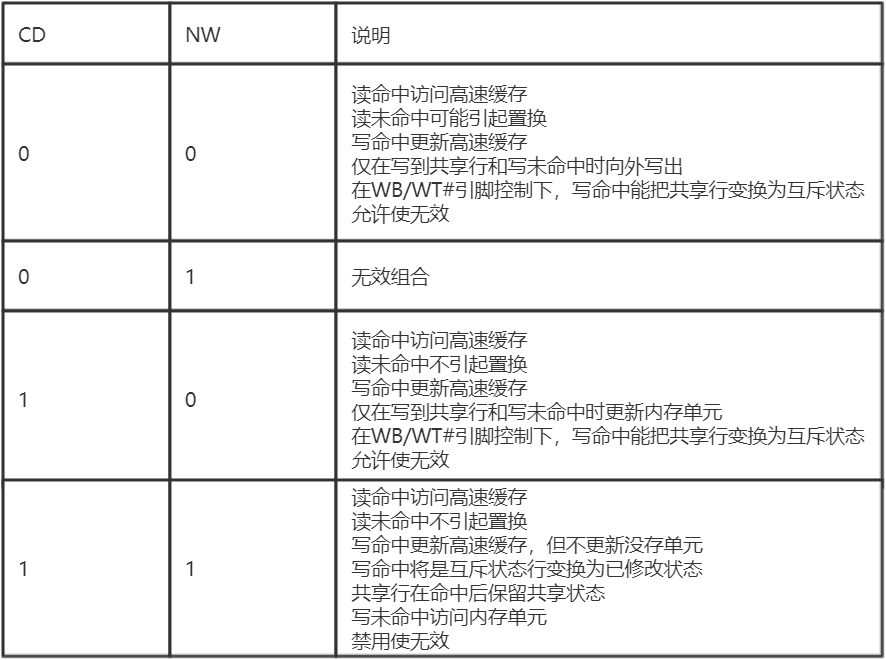

CR0 中页新增了两位用于控制高速缓存的工作方式 CD 和 NW,他们控制逻辑如下

同时新增两个指令

INVD

清空高速缓存

WBINVD

先回写缓存然后清空缓存

具体没去深究怎么回是,其中使无效的意思就是能不能用 上面两条指令。

其他新增指令

BSWAP OPRD

对OPRD进行大小端切换,OPRD可以使8位,16位,32位

XADD OPRD1, OPRD2

先交换OPRD1和OPRD2的值,再相加的结果存到OPRD1, 相当于 OPRD1 = OPRD1+OPRD2; OPRD2 = OPRD1

CMPXCHG OPRD1, OPRD2 ;

if(OPRD1 == AX/AL/EAX){ OPRD1 =OPRD2; ZF = 1 } else{ AX/AL/EAX = OPRD1; ZF = 0; }

CMPXCHG8B

CMPXCHG 的8字节比较版本

INVLPG OPRD

清理虚拟地址OPRD转换到物理地址的转译缓存

比如 虚拟地址VALUE1 = > 物理地址VALUE2, 这个转译规则由于经常用,所以被CPU记录在缓存中,这样就不必每次查表,那么INVLPG VALUE1,就可以使这条规则中缓存中清除。

CPUID

获取CPU的一些信息

RDTSC

读始终周期计数

每个始终周期CPU都会累加一个64位的计数,用此命令可以读取这个计数。

RDMSR / WDMSR

读写DMSR