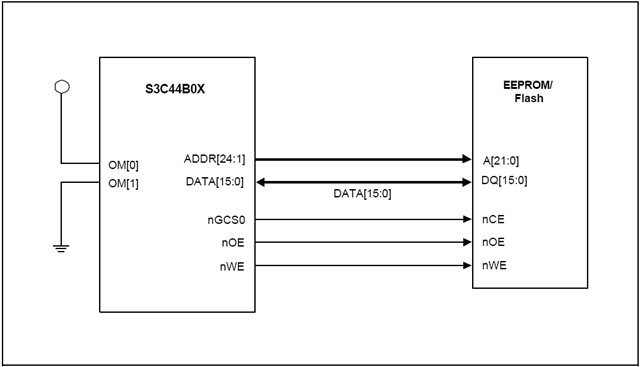

1、硬件连接

当系统复位后, s3c44b0x从0x00000000地址处读取指令。并且s3c44b0x在复位后必须进行系统参数配置。

因此这段特殊代码(BOOT ROM镜像)必须位于地址0x00000000, boot ROM的数据总线宽度可以通过OM[1:0]引脚进行配置。

表1.1、ROM Bank 0数据总线宽度

| OM[1:0] | 数据总线宽度 |

| 00 | 8-bit(byte) |

| 01 | 16-bit(half-word) |

| 10 | 32-bit(word) |

| 11 | 测试模式 |

s3c44b0x开发板上使用的BOOT ROM芯片为:Am29LV160DB-90 (16 Megabit (2 M x 8-Bit/1 M x 16-Bit))

图1.1、使用HALF-WORD EEPROM/FLASH进行HALF-WORD BOOT ROM设计参考:

图2.1、s3c44b0x开发板Am29LV160DB-90实际电路![clip_image002[7] clip_image002[7]](https://images.cnblogs.com/cnblogs_com/arci/201104/201104171627288719.jpg)

注:此处2.0R5是用于容量扩展, 实际电路板上并无此电阻

2、软件初始化

参考s3c44b0x用户指南可知, 与BOOT ROM相关的寄存器有:

(1)、总线宽度与等待控制寄存器(BWSCON)

(2)、BANK控制寄存器(BANKCON0: nGCS0)

表2.1、BWSCON与BOOT ROM相关的选项为:

| BWSCON | Bit | 描述 | 起始状态 |

| DW0 | [2:1] | 指示bank 0的数据总线宽度(只读) 00 = 8-bit, 01 = 16-bit, 10 = 32bit 通过OM[1:0]引脚进行选择 | - |

| ENDIAN | [0] | 指示bank 0的endian模式(只读) 0 = Little endian, 1 = Big endian 通过ENDIAN引脚进行选择 | - |

表2.2、BANKCON0

| BANKCON0 | Bit | 描述 | 起始状态 |

| Tacs | [14:13] | Address set-up before nGCSn | 00 |

| Tcos | [12:11] | Chip selection set-up nOE | 00 |

| Tacc | [10:8] | Access cycle | 111 |

| Toch | [7:6] | Chip selection hold on nOE | 00 |

| Tcah | [5:4] | Address holding time after nGCSn | 00 |

| Tpac | [3:2] | Page mode access cycle @ Page mode | 00 |

| PMC | [1:0] | Page mode configuration | 00 |

注: All types of master clock in this memory controller correspond to the bus clock.

所有此存储器控制器主机时钟的类型与总线时钟相符.

For example, MCLK in DRAM and SRAM is same as the bus clock, and SCLK in SDRAM is also the same as the bus

clock. In this chapter (Memory Controller), one clock means one bus clock.

例如, DRAM和SRAM中的MCLK与总线时钟相同, 并且SDRAM的SCLK也与总线时钟相同, 在这章中(存储器控制器), 1个时钟是指一个总线时钟.

其中: 由于Am29LV160DB-90不支持Page Mode(Am29PL160C支持Page Mode), Tpac和PMC对于BOOT ROM不需要进行设置,

需要进行设置的值有: Tacs, Tcos, Tacc, Toch, Tcah.

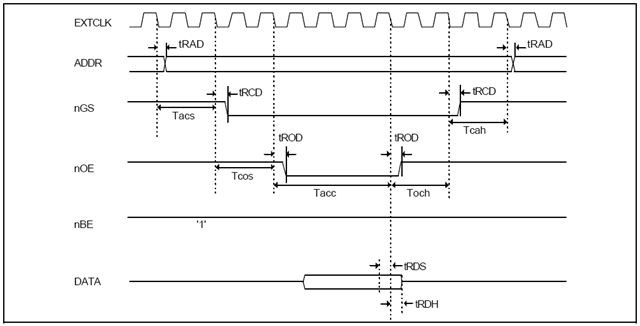

图2.1 s3c44b0x ROM/SRAM 读时序 (I) (Tacs=2,Tcos=2, Tacc=4, Toch=2, Tcah=2, PMC=0, ST=0)

注:对于bank 0, ST不可设置, ST = 0

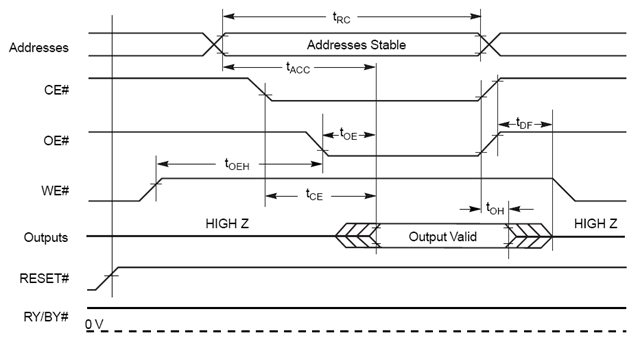

图2.2 Am29LV160DB-90读操作时序

根据图2.1和图2.2可知:

| s3c44b0x | Am29LV160DB-90 |

| Tacs + tRCD – tRAD | tACC – tCE |

| Tcos - tRCD + tROD | tCE - tOE |

| Tacc - tROD + tROD | tRC - tACC + tOE |

| Toch | 0 |

| Tcah | 0 |

通过查看s3c44b0x和Am29LV160D数据手册, 可知:

s3c44b0x: tRCD = 11ns, tRAD = 12ns, tROD = 11ns

Am29LV160D: tACC = 90ns, tCE = 90ns. tOE = 35ns, tRC = 90ns

因此Tacs = 1ns, Tcos = 55ns, Tacc = 35ns, Toch = 0ns, Tcah = 0ns

假设系统总线时钟为60MHz, one clock = 1 / (60MHz) = (50 / 3)ns

Tacs = 1ns = 1 / (50 / 3) clock = 0.06 clock = 0 clock

Tcos = 55ns = 55 / (50 / 3) clock = 3.3 clock = 4 clocks

Tacc = 35ns = 35 / (50 / 3) clock = 2.1 clock = 3 clocks

Toch = 0ns = 0 clock

Tcah = 0ns= 0 clock

BANKCON0 = 0b 00 11 010 00 00 00 00 = 0x00001a00

到此s3c44b0x BOOT ROM配置完成