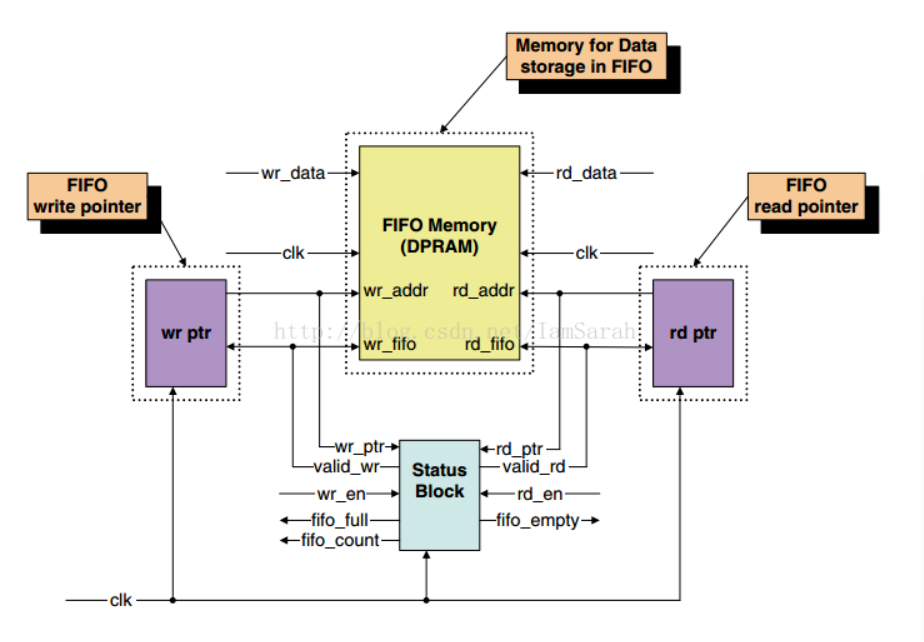

同步FIFO的结构图:

有四个逻辑块组成:RAM(实现数据的存取)、读控制(读地址控制)、写控制(写地址控制)、状态块(控制空满判断)

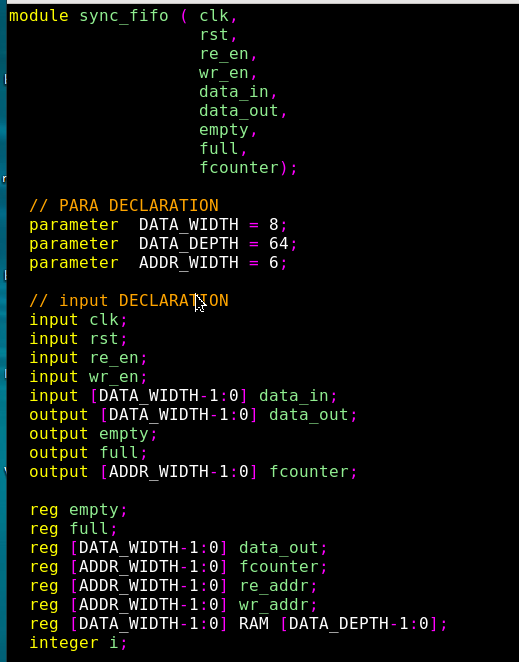

接口定义:时钟信号(clk)、复位信号(fifo_rst)、使能信号(read_en、write_en)、数据信号(fifo_in、fifo_out)、空满信号(fifo_empty、fifo_full)、计数器

参数声明:data_width、addr_width

信号类型定义:wire clk、fifo_rst、read_en、write_en、fifo_in

reg fifo_out、fifo_emoty、fifo_full

reg read_addr、write_addr

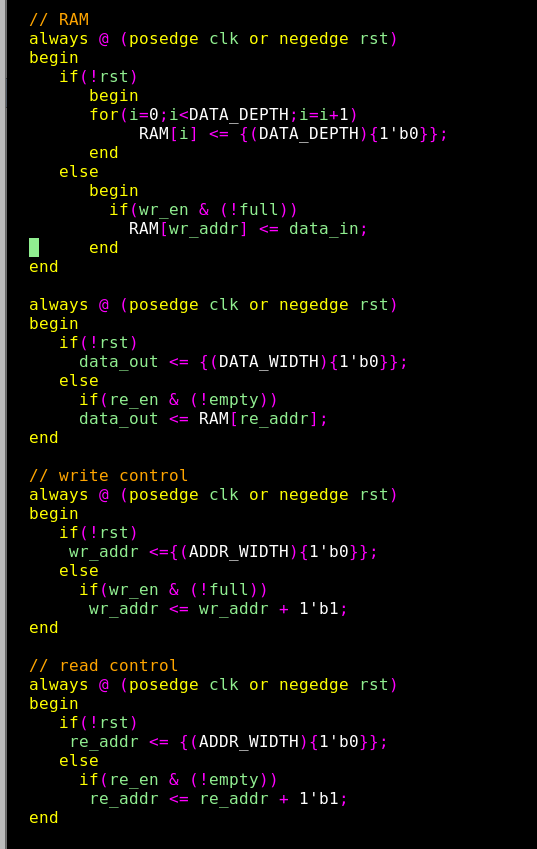

四大程序块:

- RAM结构实现(可以写也可以通过例化实现)

- 计数器控制实现

- 读写地址的控制实现

- 空满信号的判断实现