第四章 处理器体系结构

4.1 Y86指令集体系结构

一、程序员可见的状态

程序员可见状态:程序中的每条指令都会读取或修改处理器状态的某些部分

--8个程序寄存器:%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp.他们都可以存储一个字;

%esp被入栈、出栈、调用和返回指令作为栈指针;

其他情况时寄存器没有固定的含义或固定值

--3个一位条件码:ZF、OF、SF.保存最近的算术或逻辑指令所造成影响的有关信息

--PC(程序计数器):存放当前正在执行指令的地址。

--存储器:一个很大的字节数组,保存着程序和数据;

Y86用虚拟地址来引用存储器位置,硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地址,指明数据实际保存在存储器中哪个地方

--Stat:状态码,程序状态的最后一个部分,表明程序执行的总体状态,指示是正常运行还是出现了某种异常

二、Y86指令

--halt:这个指令将会终止指令的执行。

--nop:这是一个占位指令,它不做任何事情,后续为了实现流水线,它有一定的作用。

--xxmovl:这是一系列的数据传送指令,其中r代表寄存器,m代表存储器,i代表立即数。比如rrmovl指令,则代表将一个寄存器的值,赋给另外一个寄存器。

--opl:操作指令,比如加法,减法等等。

--jxx:条件跳转指令,根据后面的条件进行跳转。

--cmovxx:条件传送指令,后面的xx代表的是条件。特别的是,条件传送只发生在两个寄存器之间,不会将数据传送到存储器。

--call与ret:方法的调用和返回指令。一个将返回地址入栈,并跳到目标地址。一个将返回地址入PC,并跳到返回地址。

--push与pop:入栈和出栈操作。

三、指令编码

--对于opl、jxx、cmovxx指令来说,都有一个fn标识,占用4个二进制位(半个字节)。这个便是指令的功能部分,这个是由于它们的指令编码一样,但功能有所不同所造成的。比如对于opl,就有加、减、与、异或等操作,那么它们的指令编码第一个字节就分别为十六进制的60、61、62、63。

--Y86指令集图中可看见指令的字节级编码。每条指令需要1-6个字节不等。每条指令的第一个字节表明指令的类型。这个字节分为两个部分,每部分4位:高4位是代码部分,低4位是功能部分。功能值只有在一组相关指令共用一个代码时才有用。

--有的指令只有一个字节长,因为可能附加有寄存器指示符字节,指定一个或两个寄存器。这些寄存器字段为rA,rB。有则有,无则无,只有一个的则将第二个设为0xF。

四、Y86异常

--对于Y86来说,程序猿可见的状态中就有stat状态码,它标识了程序执行的状态。Y86需要有能力根据stat去做一些处理。不过为了简单起见,这里除了正常执行之外,都将停止指令的执行。真实当中,会有专门的异常处理程序。

--Y86有四种不同的状态码,AOK(正常)、HLT(执行halt指令)、ADR(非法地址)和INS(非法指令)。

五、Y86程序和Y86指令详情

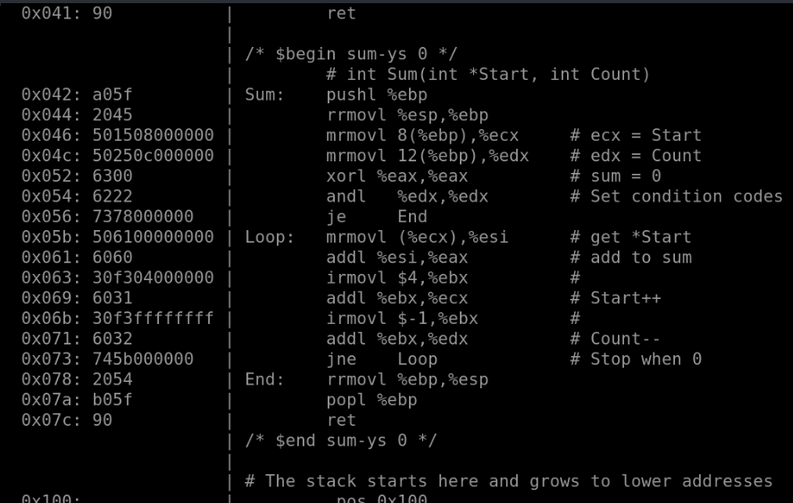

--比如对于X86指令中的 addl $4,%ecx 这样的指令,由于Y86当中的addl指令中不包含立即数,所以Y86需要先将立即数存入寄存器,即使用irmovl指令,然后再使用addl来处理加法运算。

--创建Y86代码的唯一工具是汇编器。

--以“.”开头的词是汇编命令,他们告诉汇编器调整地址,以便在那儿产生代码或插入一些数据。命令.pos0告诉编译器应该从地址0处开始产生代码。这个地址是所有Y86程序的起点。

4.2 逻辑设计和硬件控制语言HCL

一、逻辑门

--逻辑门产生的输出,等于它们输入位值的某个布尔函数。

--AND &&

OR ||

NOT !

二、组合电路和布尔表达式

--逻辑门产生的输出,等于它们输入位值的某个布尔函数。

--两个或多个逻辑门的输出不能连接在一起,否则可能会使线上的信号矛盾,导致一个不合法的电压或电路故障。

--网必须无环。

三、字级的组合电路和HCL整数表达式

--所有字级的信号都声明为int,不指定字的大小

--算数/逻辑单元(ALU)是很重要的组合电路,有三个输入,标号为A、B的两个数据输入和一个控制输入。根据控制输入的设置,电路会对数据输入执行不同的算数或逻辑操作。

四、集合关系

--判断集合关系的通用格式是:iexpr in {iexpr1,iexpr2,...,iexprk}

五、存储器和时钟

--时钟寄存器(简称寄存器)存储单个位或字,时钟信号控制寄存器加载输入值

--随机访问存储器(简称存储器)存储多个字,用地址来选择该读或该写哪个字

4.3 Y86的顺序实现

一、将处理组织成阶段

--取指:取指阶段从存储器读取指令字节,地址为程序计数器PC的值

--译码:译码阶段从寄存器文件读入最多两个操作数

--执行:在执行阶段,算数/逻辑单元要么根据ifun的值执行指令指明的操作,计算机存储器引用的有效地址,要么增加或减少栈指针

--访存:访存阶段可以将数据写入存储器,或从存储器读出数据

--写回:写回阶段最多可以写两个结果到寄存器文件

--更新PC:将PC设置成下一条指令的地址

二、SEQ硬件结构和时序:看书上P258图

三、SEQ阶段的实现

--取指阶段:取指阶段包括指令存储器硬件单元。以PC作为第一个字节(字节0)的地址,这个单元一次从存储器读出6个字节,第一个字节被解释称指令字节,分为两个4位数。标号为“icode”和“ifun”的控制逻辑块计算指令和功能码等于从存储器读出值,或者当指令地址不合法时(imem_error指明),这些值对应于nop指令。

--译码和写回阶段:都要访问寄存器文件。寄存器文件有四个端口,支持同时进行两个读(端口A、B)和两个写(E、M),每个端口都有一个地址连接和一个数据连接。根据指令代码icode以及寄存器指示值rA和rB,可能还会根据执行阶段计算出的Cnd条件信号。

--执行阶段:执行阶段包括算术/逻辑单元(ALU)第一步每条指令的ALU计算,执行阶段还包括条件码寄存器。

--访存阶段:访存阶段的任务是读或者写程序数据,两个控制块产生存储器地址和存储器输入数据的值,另外两个块产生控制信号表明应该执行读操作还是写操作。当执行读操作时数据存储器产生值valM。

--更新PC阶段:SEQ中最后一个阶段会产生程序计数器的新值,依据指令的类型和是否要选择分支,新的PC可能是valC、valM、valP

*实验楼

*遇到的问题

希望老师讲一下为什么指令pop%esp,会使函数的返回Oxabcd,以及其他的Y86指令也会这样吗

*参考资料

-最重要当然是书,好多概念都是照着书打的

-参考了闫佳歆的博客,主要是看她重点学习了哪里,我也照着学