最近在学习DE1-SOC,写一点应用笔记。理解有偏差的地方还望小伙伴们多多指点^_^

一、Cyclone –V Interconnection

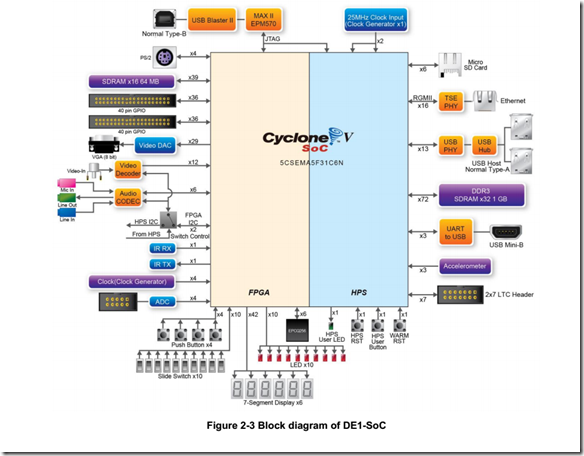

DE1-SOC是基于Cyclone V设计的板卡,在Cyclone-V集成了FPGA与Arm Core A9,并分别连接了不同的外设,可通过HPS-FPGA AXI bridges进行二者间的数据通信。如图:

The HPS contains the following HPS-FPGA AXI bridges:

■ FPGA-to-HPS Bridge

■ HPS-to-FPGA Bridge

■ Lightweight HPS-to-FPGA Bridge

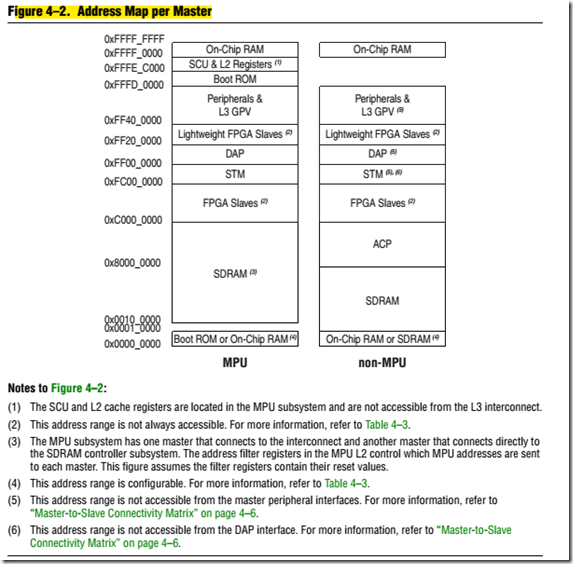

每种总线可以访问的地址范围如下:

由该表可以得出,Lightweight HPS-to-FPGA Bridge可以访问0xFF20_0000-0xFF40_0000的外设地址空间,可用于控制数据的通信;HPS-to-FPGA Bridge则可以访问0xC000_0000-0xFC00_000近1G的物理地址空间,适合于大量数据的高速传输;而FPGA-to-HPS Bridge将HPS作为Slave,可以访问HPS全部的物理地址空间

对三种Bridge的访问在物理上都是由相应的Axi接口完成,由于Qsys中自含将Avalon总线转化为axi总线的机制,所以在自定义IP中,使用Avalon总线即可。

二、Avalon 总线读写时序

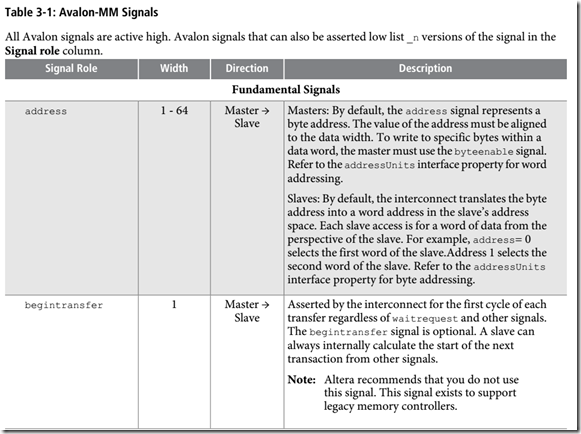

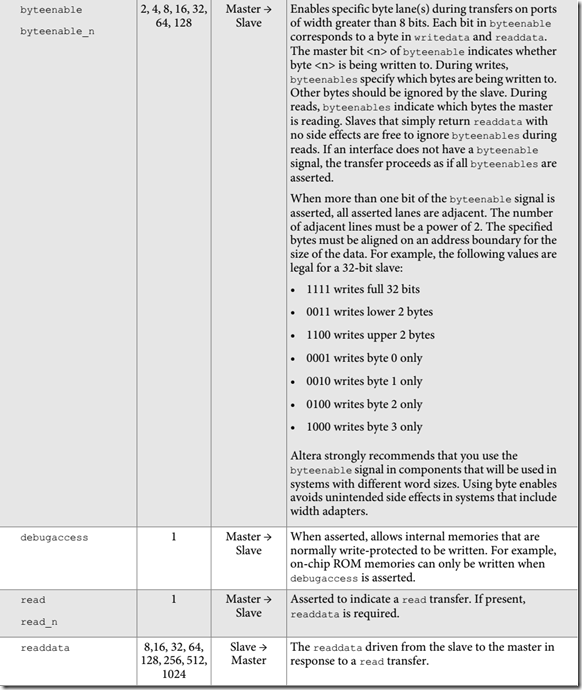

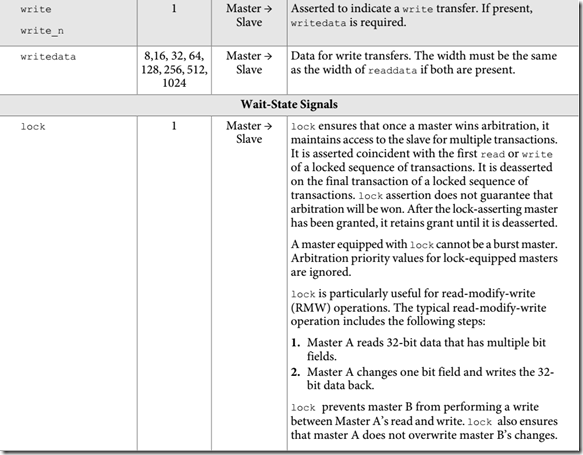

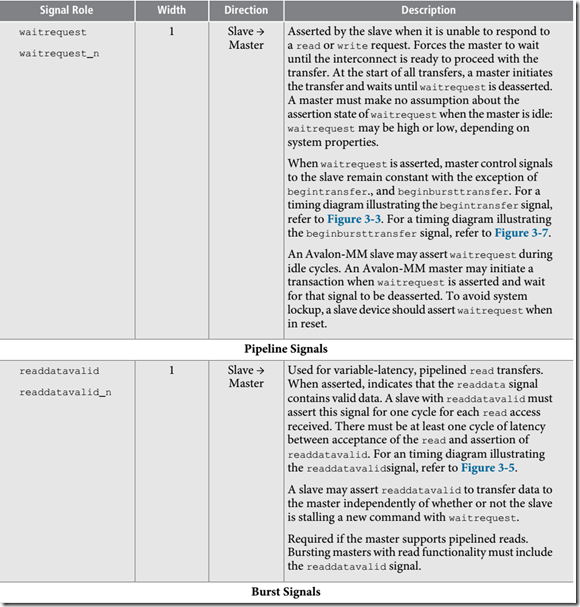

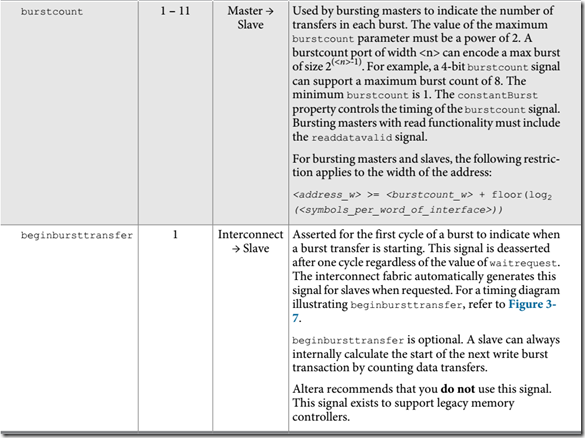

Avalon 总线信号及其描述如下,实际应用时可根据传输方式的选定而选用部分信号

Avalon 总线有以下几种读写方式:

Typical Read and Write Transfers

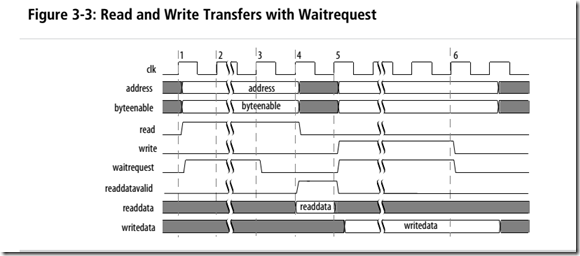

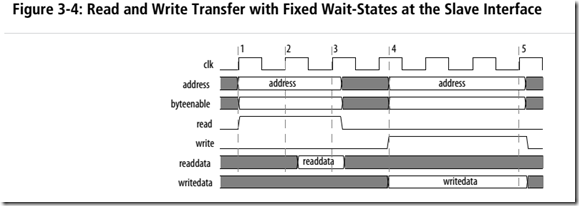

Read and Write Transfers with Fixed Wait-States

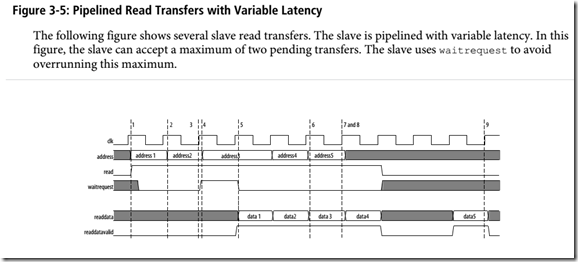

Pipelined Transfers

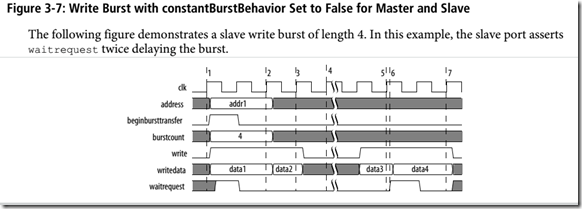

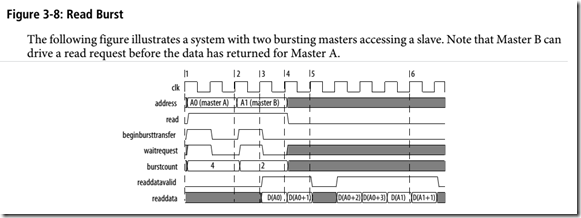

Burst Transfers

重点要掌握好的信号一个是waitrequest,另一个是readdatavalid。在任何传输方式中,当总线给出的waitrequest信号有效时,要发起读写的主/从设备应当保持输出的地址信号、读写信号、写数据时的数据信号以及在burst传输中的burstcount信号有效,直到waitrequest信号为低,表明目标设备已经接收请求,然后方可发起下一次传输。