在前一篇文里已经整理了一些Cyclone-V与Avalon-MM的资料,在这篇文里给一个 Slave设备的简单实现——7段数码管实现。

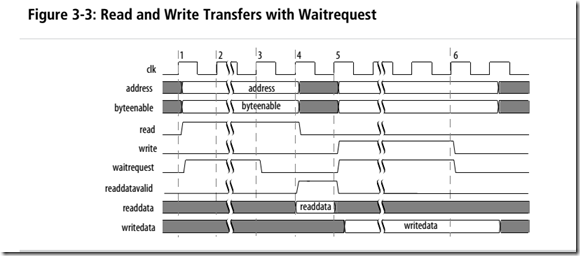

先上一个Avalon-MM的一般时序图:

一、硬件设计

IP逻辑实现:

当作为Avalon总线的Slave时,上图中的控制信号、地址信号都为输入,另外还会有一个ChipSlect信号。当有设备发出对该设备的read/write请求时,ChipSlect信号有效,同时addres为从设备的寄存器地址。例如该设备基址为0x0100,有两个32位寄存器,那么当某主设备发出地址0x0104选中该设备时,ChipSelect有效,同时从设备收到的Address为1(在该例中地址以words为单位)。

7段数码管控制器是一个只写设备,故只需要clk,chipselect,address,write,及writedata信号即可。SystemVerilog实现逻辑如下:

//seg7.sv module BCD2Seg( input logic [3:0] din, output logic [7:0] dout ); always_comb begin case (din) 'b0000:dout<='b100_0000; 'b0001:dout<='b111_1001; 'b0010:dout<='b111_1001; 'b0011:dout<='b011_0000; 'b0100:dout<='b001_1001; 'b0101:dout<='b010_0010; 'b0110:dout<='b000_0010; 'b0111:dout<='b111_1000; 'b1000:dout<='b000_0000; 'b1001:dout<='b001_0000; default:dout<='b111_1111; endcase end endmodule module seg7_disp #(parameter N=6)( input logic clk,reset,chipselect, input logic [3:0]byteenable, input logic write, input logic [31:0] writedata, output logic [47:0] segout ); //assert(N<=8); logic [N-1:0][3:0] bcdcon;//to decoder genvar i; generate for(i=0;i<N;i++) begin:gen1 BCD2Seg ui(.din(bcdcon[i][3:0]),.dout(segout[i*8+7:8*i])); end endgenerate always @(posedge clk) begin if(reset) bcdcon<=0; if(chipselect=='b1) begin if(write) bcdcon <=writedata; end end endmodule

Avalon 总线IP封装

1)打开Qsys,在IP Catalog中选择New Component 新建用户器件(IP Core),编辑必要的信息并选择文件,Analyze File

2)编辑Signals和Interfaces选项卡,根据Module信号的功能选择对应的SignalType,在Interfaces选项卡设置clock.reset,以及avalon信号的parameter

注意:这里WORDS与SYMBOL的区别

![image_thumb[1] image_thumb[1]](http://images0.cnblogs.com/blog/723157/201502/242254420807549.png)

![image_thumb[3] image_thumb[3]](http://images0.cnblogs.com/blog/723157/201502/242254438142221.png)

![image_thumb[6] image_thumb[6]](http://images0.cnblogs.com/blog/723157/201502/242254457218904.png)

![image_thumb[8] image_thumb[8]](http://images0.cnblogs.com/blog/723157/201502/242254476113359.png)

![image_thumb[10] image_thumb[10]](http://images0.cnblogs.com/blog/723157/201502/242254488143360.png)