SystemVerilog Instance Worlds

When generating an UVM testbench and in particular the DUT - testbench communication it is helpful to understand the differences between the two different "instance worlds" of SystemVerilog and the order in which things are created.

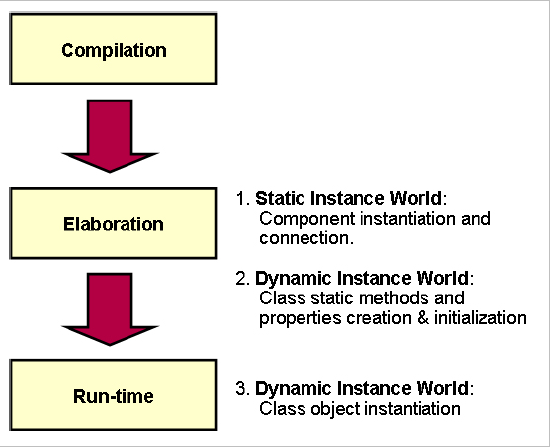

SystemVerilog Simulation Steps or Phases

A SystemVerilog simulation consists of three steps or phases (not to be confused with UVM phases): compilation, elaboration and run-time.

Static Instance World

Many SystemVerilog component instances are created during elaboration before the simulation begins. Once simulation begins instances of these components are neither created nor destroyed but remain throughout the simulation. We refer to this as the static instance world. Components that belong to this world are module instances, interface instance, checker instances, primitive instances and the top level of the design hierarchy.

Dynamic Instance World

Component instances that may be created and destroyed during simulation (the SystemVerilog run phase) belong to what is referred to as the dynamic instance world. Components that belong to this world are classes. There is an exception to this however. Class methods and properties that are eclared as static are created prior to runtime. They are, however, created after the component instances of the static world. This exception is often used to reate and initialize class properties (including class objects) before simulation. This is referred to as static initialization. The UVM factory is an example of an object that is statically initialized.

During Elaboration:

1. Component instances of the static world

2. Static methods and static properties of classes

During run-time:

1. Class instances

SystemVerilog一般提供了四种不同实例之间的通信手段或连接:

ports,pointers, Verilog hierarchical paths, and shared variables,For class based testbenches ports may not be used.

Hierarchical paths are not recommended. Pointers are the common means used. Shared variables may be used in limited areas.

建议共享变量只能用于初始化或状态类型有沟通当信息读写之间明确的关系。