在DE2关于Nios ii的范例中,有一个Reset_Delay.v的模块,代码如下:

1 module Reset_Delay(iRST,iCLK,oRESET);

2 input iCLK;

3 input iRST;

4 output reg oRESET;

5 reg [23:0] Cont;

6 always@(posedge iCLK or negedge iRST)

7 begin

8 if(!iRST)

9 begin

10 oRESET <= 1'b0;

11 Cont <= 24'h0000000;

12 end

13 else

14 begin

15 if(Cont!=24'hFFFFFF)

16 begin

17 Cont <= Cont+1;

18 oRESET <= 1'b0;

19 end

20 else

21 oRESET <= 1'b1;

22 end

23 end

24 endmodule

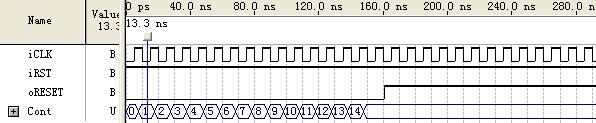

由于其中的Cont是24位2进制,数值太大不好仿真,可以将其改为4位二进制从而便于观察!改为4位2进制时的仿真波形如下:

前面的一段时间(iRST位高电平):

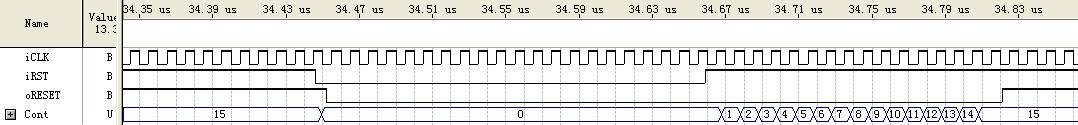

当后面的一段时间(iRST产生负脉冲):

结论:

由此可知,Reset_Delay.v模块应该是:给Nios II CPU提供有效的复位信号,即上电复位信号[若iCLK=50MHz(20ns)则产生(24'hFFFFFF)*20ns=0.3355443s宽度的复位信号]和手动复位信号的延时[宽度=手动复位负脉冲宽度+0.3355443s]