首先,要指出,本文不描述任何IP的功能与使用。

在开发一个大型FPGA项目时,多人协作是必不可少的。这个时候,如何提交设计给负责集成的人,是项目开发中最关键的问题之一。

常用的一个方法是,提交网表。网表的提交可以算是相当方便的操作了,这在ISE的时期还体会不到,但到了Vivado中,正如amazing icecream在博文http://blog.chinaaet.com/detail/37153中描述的,dcp的引入,让网表这一非常好用的功能发挥了其应有的作用。对于部分设计,直接使用dcp提交设计,已经足够。

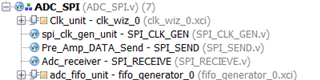

但正如amazing icecream在博文http://blog.chinaaet.com/detail/37165中描述的,dcp不支持嵌套这一问题,成为Vivado在工程化管理中最严重的问题之一。比如,如果遇到如下的设计

设计中包含了两个IP的xci。如果IP使用的OOC模式,则和dcp模块一样,都使用网表提交给顶层ADC_SPI。如果再将ADC_SPI模块打包成dcp,就会出现dcp文件的嵌套。调用ADC_SPI这个dcp网表时,会出现错误,无法读取其中的dcp模块的信息。

这就意味着,使用dcp的模块,只能是纯代码的模块,无法使用任何IP,哪怕是FIFO、BRAM之类的简单IP。另外,dcp也无法多次提交,所有开发者只能提交一次dcp网表,而无法层级提交dcp网表。

所以,本文介绍一下IP Packager这个工具,来解决上述的工程问题。目前的IP Packager仍然不支持包含dcp网表,但是生成子dcp网表的工程也可以封装为IP,所以可以用IP的方法来层级嵌套。

IP Packager,用来将自己的设计打包,封装成IP。然后在IP Catalog中导入后就可以与Xilinx提供的IP一起使用。其操作相对简单,难度低,可操作性很强。该工具为Vivado独有,ISE似乎没有类似的工具可以使用。

如何使用呢?首先,准备一个设计,由于IP Packager在封装IP时并不会检查设计是否有问题,比如是否有源文件确实等,需要开发者自己确认设计是否完整。

然后在菜单栏中选择“Tool”->“Create and Package IP…”,如下图所示。

弹出如下界面,有兴趣可以自行阅读说明或参考相关文档,点击Next

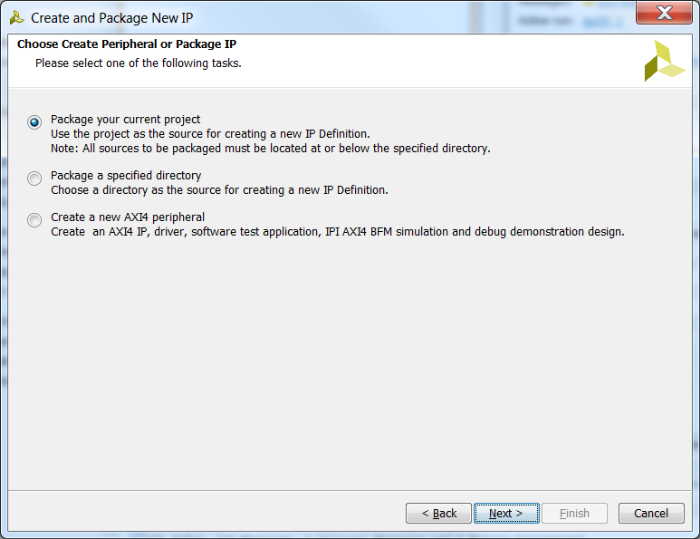

在下一个界面中,选择第一项,然后点击Next。这里说明一下,第一项是将工程封装成IP,第二是将某个目录下的源文件封装成IP,第三项是封装AXI4的外设,有兴趣可以自行阅读说明文字或查询文档。

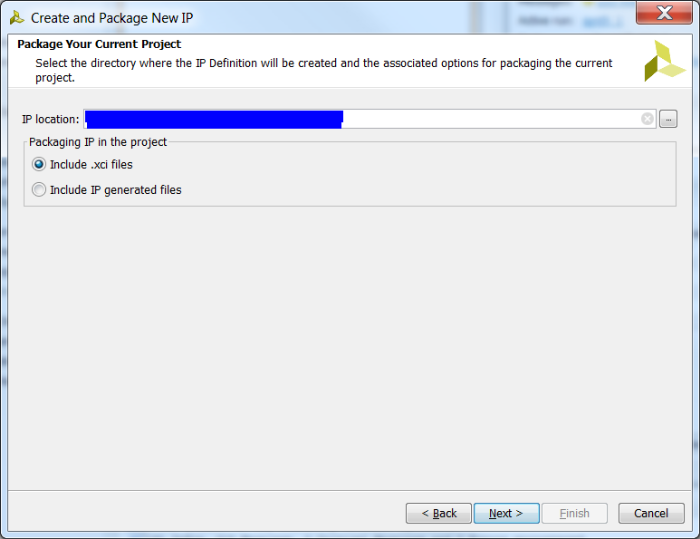

下一界面选择IP的路径,用于日后导入IP文件,同时选择仅包括xci文件还是包括所有IP已经生成的网表。这里选择“Include .xci files”

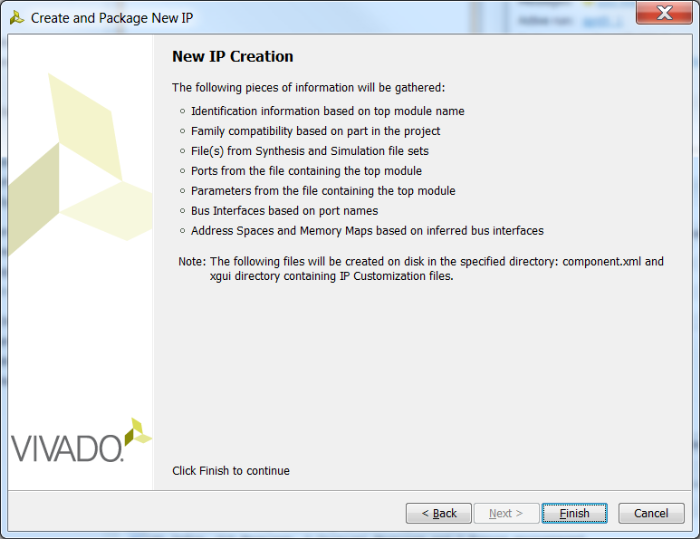

最后一页点击Finish即可

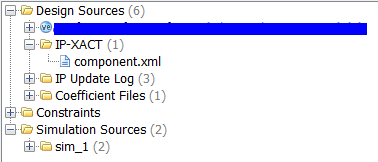

设置完成之后,可以发现在Project Manager窗口下的Hierarchy标签中,会多一个IP-XACT,下面会有一个component.xml,其中保存着封装IP的信息。

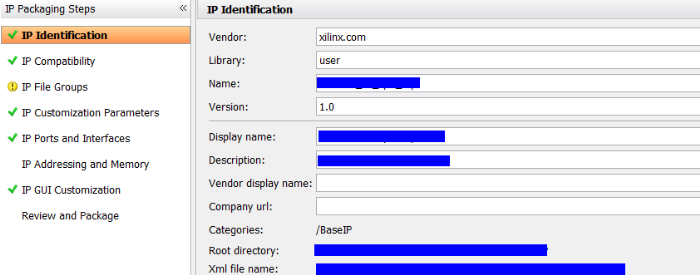

在Package IP的主界面里,列出了IP的定制化选项

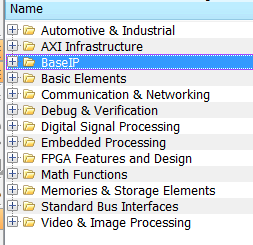

在第一项中,可以设置IP的信息,其中Categories是导入后IP存放的位置,默认为BaseIP,及IP Catalog导入后,可以再BaseIP中找个该IP

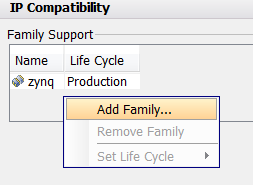

需要注意的是第二项“IP Compatibility”,点开后如下图所示。

从图中可以看到,此IP在封装时是兼容Zynq系列的,但是不兼容其他系列,为了让其支持其他系列的FPGA,可以右键弹出菜单,点击“Add Family”。

在弹出的“Choose Family Support”中选择希望添加的FPGA。

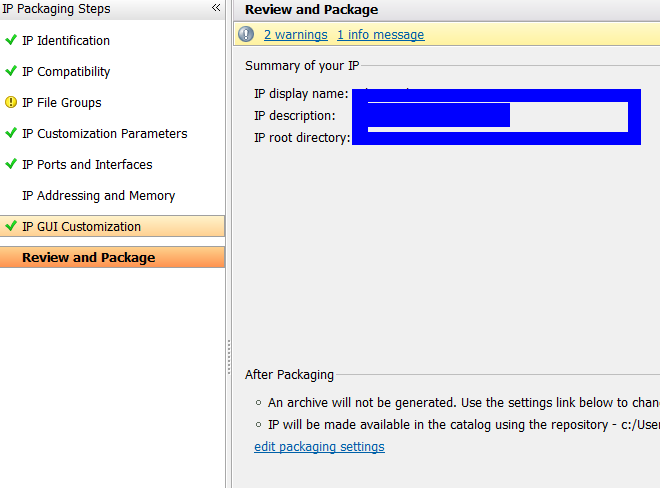

在最后一步“Review and Package”中,点击下方的edit packaging settings, 可以打开设置界面。

在蓝色框中,勾选“Create archive IP”即可生成zip压缩文件,用来保存IP信息,便于存档及使用。点击OK后回到Vivado主界面,然后点击Re-package IP即可刷新输出文件。

此时, IP封装的工作已经全部完成。

IP封装好以后,下一步就是如何调用该IP。首先打开IP Catalog。无论是单独建一个管理IP的工程,还是在Project Manager中点击IP Catalog,都可以。

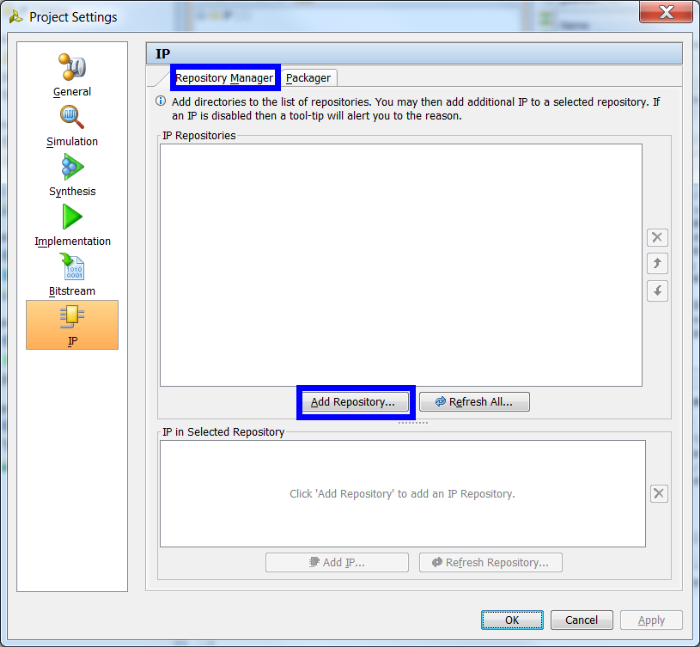

进入IP Settings,界面如下图所示

在“Repository Manager”标签中,点击“Add Repository…,如上图蓝框所示。

添加好刚才进行IP封装的路径后,即可自动识别出IP

点击OK返回IP Catalog主界面,即可在IP Catalog中找到相关IP。注意,只有IP兼容FPGA芯片时,该IP才会显示在IP Catalog中。比如IP封装式选择的是V7,主工程是K7,则无法使用;但是IP封装中添加兼容K7后,主工程是K7时就可以在IP Catalog中找到该IP

IP Packager的问题是,代码无法加密,不具有类似dcp的不可读功能。

考虑到Vivado目前仍然比较新,不排除在今后的版本中添加IP Packager的加密功能和dcp的嵌套功能。

如有兴趣,赶快去定制自己的IP Core吧。

转载:http://blog.chinaaet.com/ad604/p/37169