本文基于Vivado 2014.2,通过一个简单的设计来讨论Vivado Logic Analyzer的功能。

在上一篇http://blog.chinaaet.com/detail/37242中,设置好了需要捕获的信号。

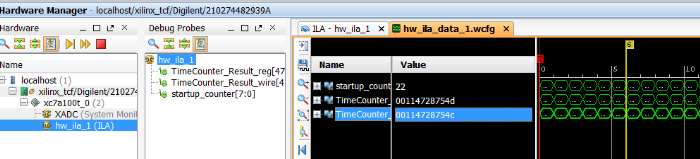

完成Implementation后,生成bit文件,打开Hardware Manager,下载并配置好FPGA,开始Vivado Logic Analyzer的使用。

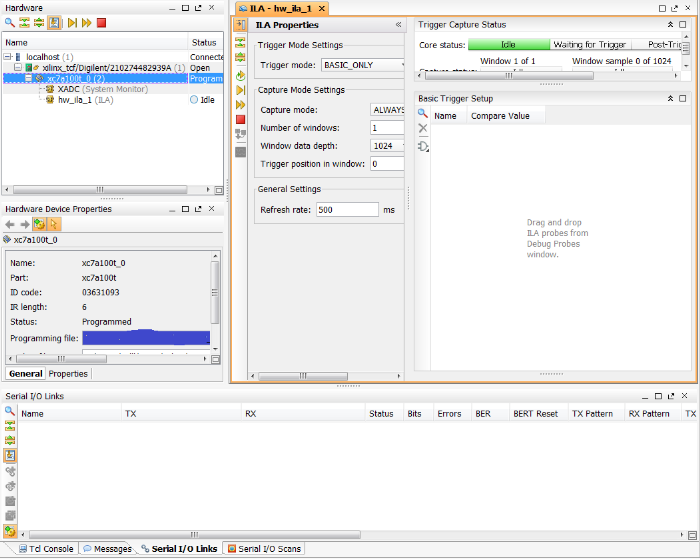

1. 下载好bit文件后的界面如下图所示。

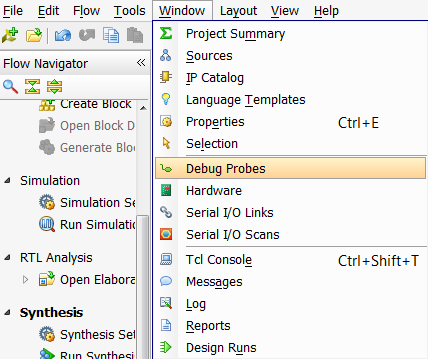

2. 这里有个问题,Vivado 2014.2中,Debug Probes窗口不会自动打开,可以再Windows选项单中找到该窗口。

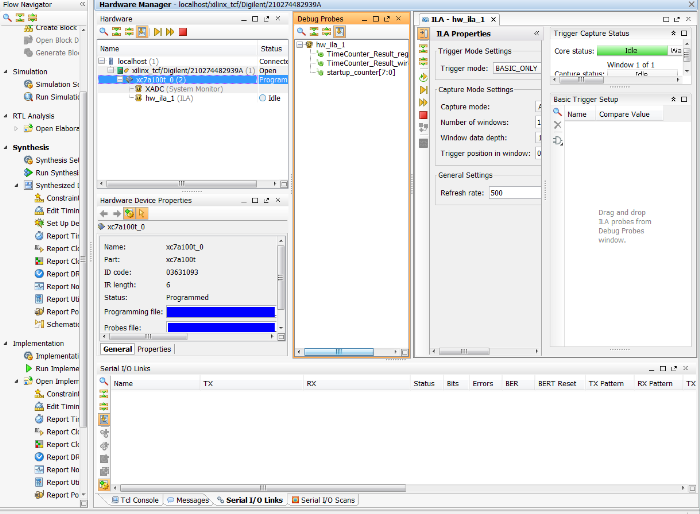

3. 打开Debug Probes窗口后的界面如下图所示。

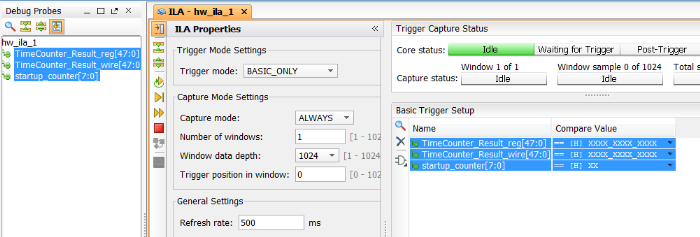

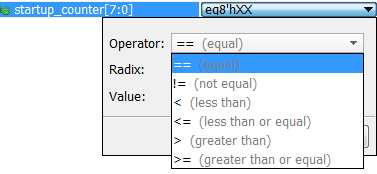

4. 在Debug Probes中,把需要观察的信号拖到Basic Trigger Setup中,可以设置触发信号。

5. 设置好触发信号之后,就可以开始捕获信号。

6. 每一组触发条件可以设置Operator、Radix和Value来设置具体的触发条件,多个触发条件还可以进行组合。

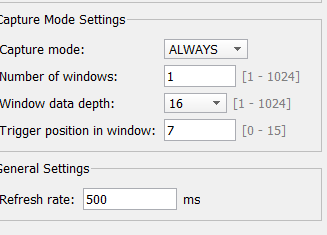

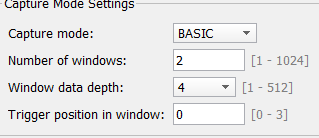

7. 为了便于观察,在Window data depth将数据设为16个数据。

8. 设置好之后重新捕获数据,可以看到一次只捕获16个数据。

9. 可以设置窗口的数目,这里将Number of Windows设为2,代表两个窗口,每次捕获的数据为4个。

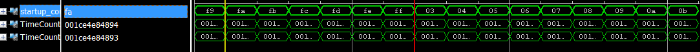

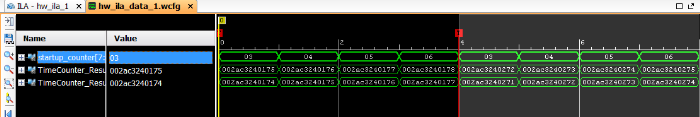

10. 重新触发后,可以看到,触发了两次,每次的触发条件都是一致的,即startup_counter = 8’h03。从下方的两个计数器可以看到,是先后的两次捕获。

转载:http://blog.chinaaet.com/luozhongpin1989/p/37264