关于信号的延迟---verilog

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: chensimin // // Create Date: 2018/02/08 11:39:20 // Design Name: // Module Name: signal_detect // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module signal_detect( input wire clk, input wire rst, input wire signal_en //input wire signal //output wire signal_existence ); reg signal; always @(posedge clk or posedge rst) begin if(rst) signal <= 1'b0; else if(signal_en) signal <= 1'b1; else signal <= 1'b0; end reg signal_delay; wire signal_rise; always @(posedge clk or posedge rst) begin if(rst) signal_delay <= 1'b0; else signal_delay <= signal; end assign signal_rise = !signal_delay && signal; endmodule /* add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns} add_force {/signal_detect/signal_en} -radix hex {0 0ns} {1 300ns} {0 400ns} */

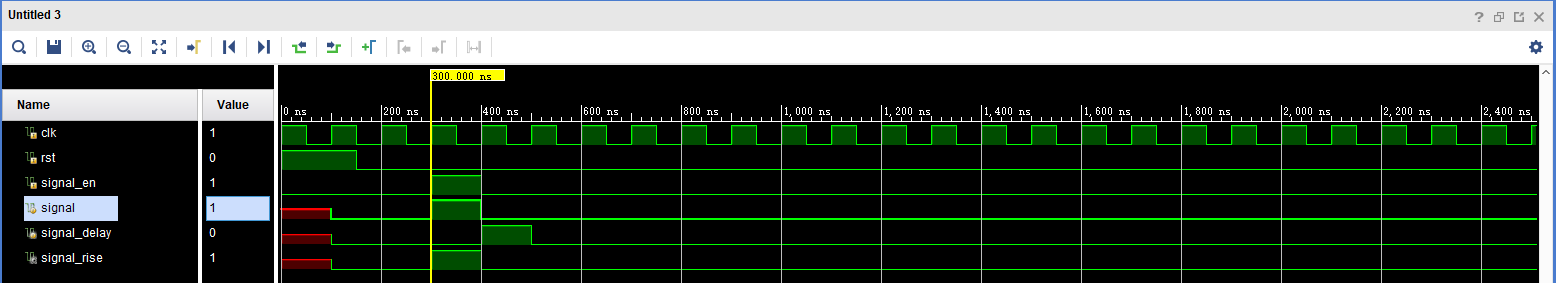

仿真波形:

容易犯下这样一种错误:

module signal_detect( input wire clk, input wire rst, input wire signal //input wire signal //output wire signal_existence ); reg signal_delay; wire signal_rise; always @(posedge clk or posedge rst) begin if(rst) signal_delay <= 1'b0; else signal_delay <= signal; end assign signal_rise = !signal_delay && signal; endmodule /* add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns} add_force {/signal_detect/signal} -radix hex {0 0ns} {1 300ns} {0 400ns} */

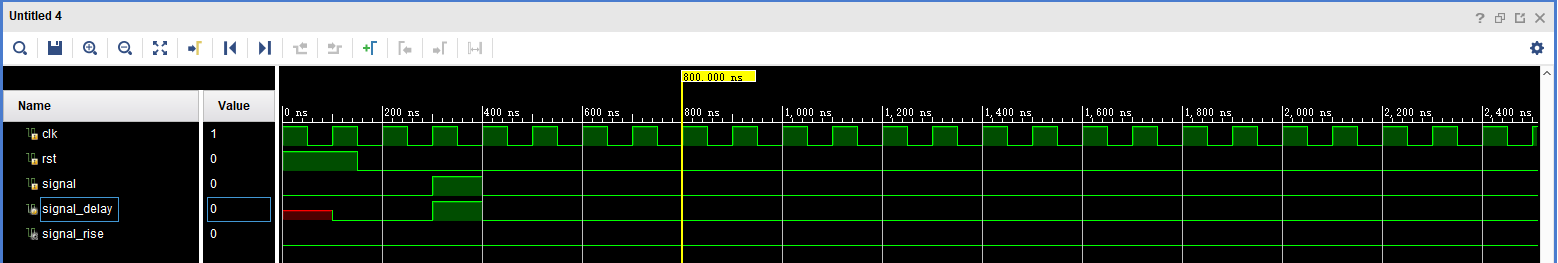

仿真波形:

像这种写法,根本就起不到边沿检测的作用,只是对外部信号进行一次采集。