Verilog手绘FVH信号

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: chensimin // // Create Date: 2018/09/17 13:20:06 // Design Name: // Module Name: ntsc_fvh // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module ntsc_fvh( input wire clk, //27MHz input wire rst, input wire enable, output wire hsout, output wire vsout, output wire oeout ); parameter THSOUT = 65; //2.4us parameter H_TOTAL = 1716; //64us parameter V_TOTAL = 525; wire hsout_falling; //------------------------------------------------- reg [15:0]hsout_cnt = 0; always @(posedge clk or posedge rst) begin if(rst) hsout_cnt <= 0; else if(enable) begin if(hsout_cnt == H_TOTAL) hsout_cnt <= 1; else hsout_cnt <= hsout_cnt + 1'b1; end else hsout_cnt <= 0; end //------------------------------------------------- reg hsout_reg = 1'b1 ; always @(posedge clk or posedge rst) begin if(rst) hsout_reg <= 1'b1; else if(enable) begin if(hsout_cnt <= THSOUT - 1 || hsout_cnt == H_TOTAL) hsout_reg <= 1'b0; else if(hsout_cnt >= THSOUT && hsout_cnt <= H_TOTAL - 1) hsout_reg <= 1'b1; end else hsout_reg <= 1'b1; end //------------------------------------------------- reg hsout_reg_delay = 1'b1; always @(posedge clk or posedge rst) begin if(rst) hsout_reg_delay <= 1'b1; else if(enable) hsout_reg_delay <= hsout_reg; else hsout_reg_delay <= 1'b1; end //------------------------------------------------- reg [15:0] hsout_falling_cnt = 0; always @(posedge clk or posedge rst) begin if(rst) hsout_falling_cnt <= 0; else if(enable) begin if(hsout_falling_cnt == V_TOTAL) begin hsout_falling_cnt <= V_TOTAL; if(hsout_falling) hsout_falling_cnt <= 1; end else if(hsout_falling) hsout_falling_cnt <= hsout_falling_cnt + 1'b1; end else hsout_falling_cnt <= 1'b0; end //------------------------------------------------- reg vsout_reg = 1'b1; reg oeout_reg = 1'b0; always @(posedge clk or posedge rst) begin if(rst) begin vsout_reg <= 1'b1; oeout_reg <= 1'b0; end else if(enable) begin if(hsout_falling_cnt < 4 || (hsout_falling_cnt == 4 && hsout_cnt < 871 && hsout_cnt >1)) begin vsout_reg <= 1'b1; oeout_reg <= 1'b0; end else if(hsout_falling_cnt == 4 && hsout_cnt == 871) begin vsout_reg <= 1'b0; oeout_reg <= 1'b1; end else if(hsout_falling_cnt == 7 && hsout_cnt == 871) vsout_reg <= 1'b1; else if(hsout_falling_cnt == 267 && hsout_cnt == 13) begin vsout_reg <= 1'b0; oeout_reg <= 1'b0; end else if(hsout_falling_cnt == 270 && hsout_cnt == 13) vsout_reg <= 1'b1; else begin vsout_reg <= vsout_reg; oeout_reg <= oeout_reg; end end end //------------------------------------------------- assign hsout_falling = hsout_reg_delay && (!hsout_reg); assign hsout = hsout_reg; assign vsout = vsout_reg; assign oeout = oeout_reg; endmodule /* add_force {/ntsc_fvh/clk} -radix hex {1 0ns} {0 25000ps} -repeat_every 50000ps add_force {/ntsc_fvh/rst} -radix hex {1 0ns} {0 100ns} add_force {/ntsc_fvh/enable} -radix hex {1 0ns} */

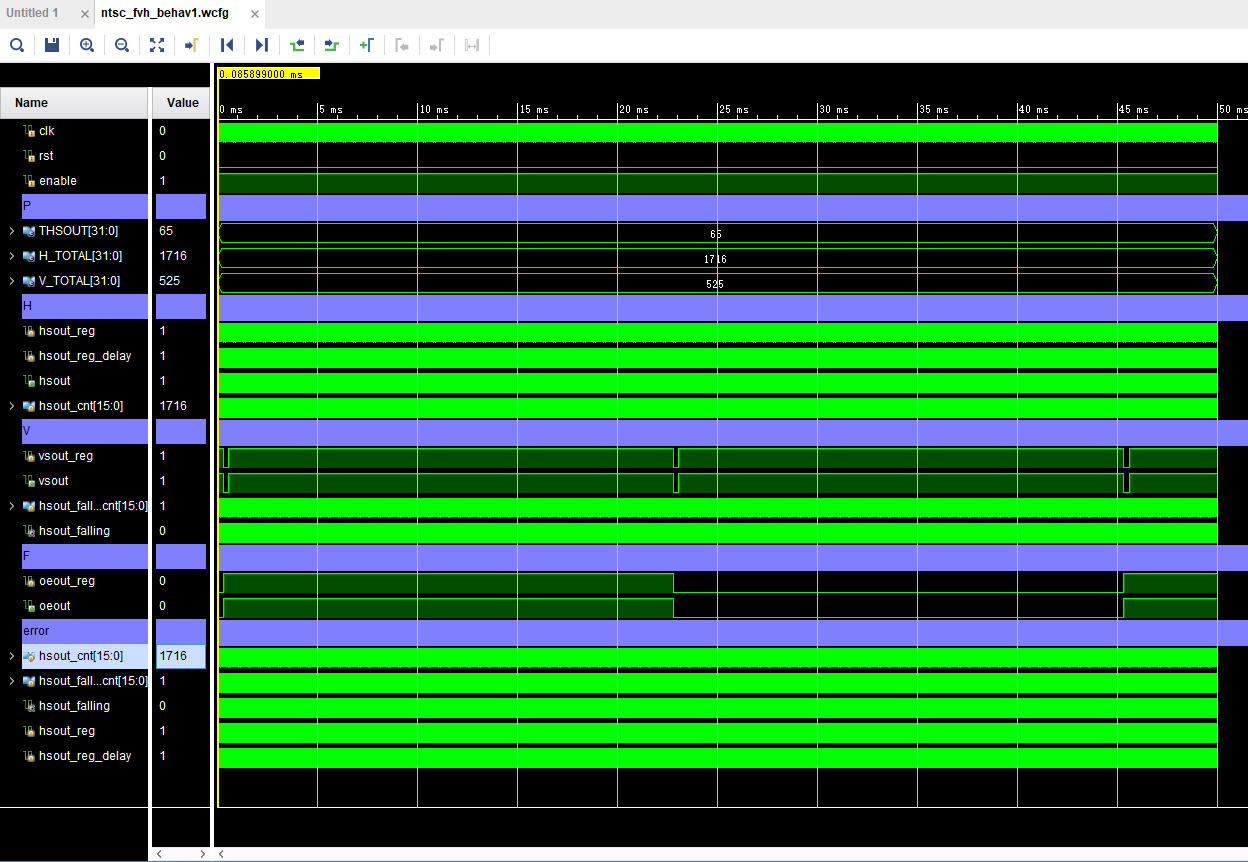

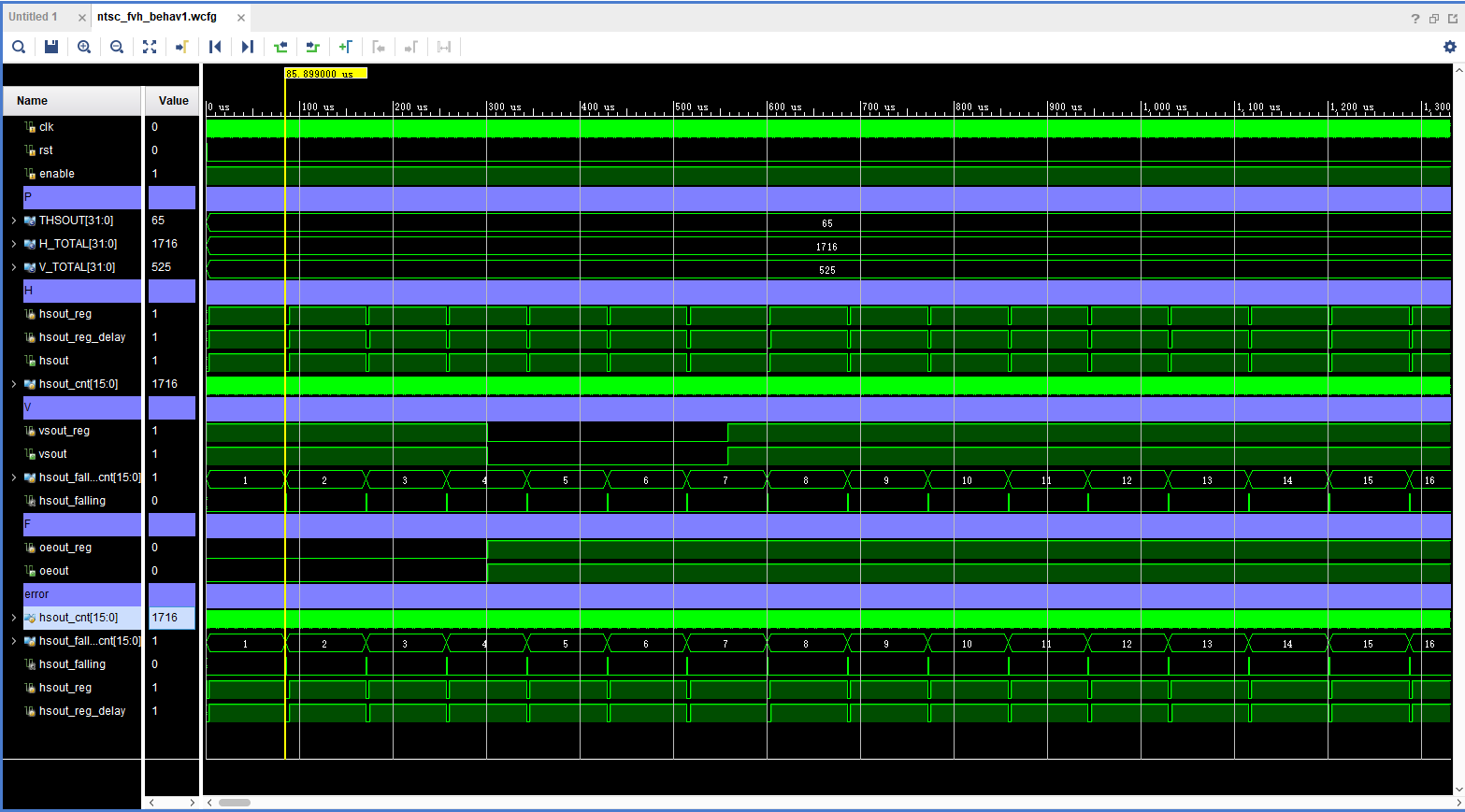

仿真结果: