作为一个硬件程序设计民工,最近一直在学习python,写个爬虫,排个序,再画个界面,其实还是挺好玩的。然而这不是我的主业啊!!!-_-|||

下学期开学就要找工作了,明天刚好是新的一个月,还是滚回去调我的FPGA吧。

今天先更新一个很小很小的例子作为开端,这是前几天xxx给我出的一道很随意的题目,主要是看面对一个项目,如何进行需求分析,模块功能划分以及仿真验证,当然还有如何写文档。

一、需求分析

设计一个十字路口交通等控制系统,其要求如下:

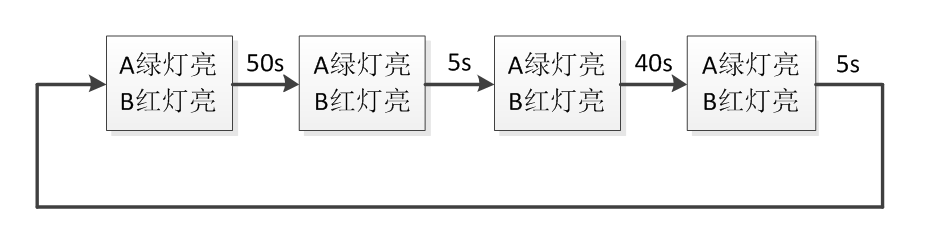

(1)东西(用A表示)、南北(用B表示)方向均有红灯、绿灯、黄灯指示,东西向持续时间暂定为50s、5s和45s(对应南北向持续时间为40s、5s和55s),要求可以更改该时间。交通灯正常运行的切换示意图如图1.1所示。

图1.1 交通控制系统正常运行切换示意图

(2)系统设有时钟,以倒计时方式显示每一路允许通行的时间。

(3)当任何一个方向出现特殊情况时,系统可由交警手动控制进入特殊运行状态,即红灯全亮,时钟停止计时,东西、南北向所有车辆停止通行;当特殊运行状态结束后,系统恢复工作,继续正常运行。

二、原理分析

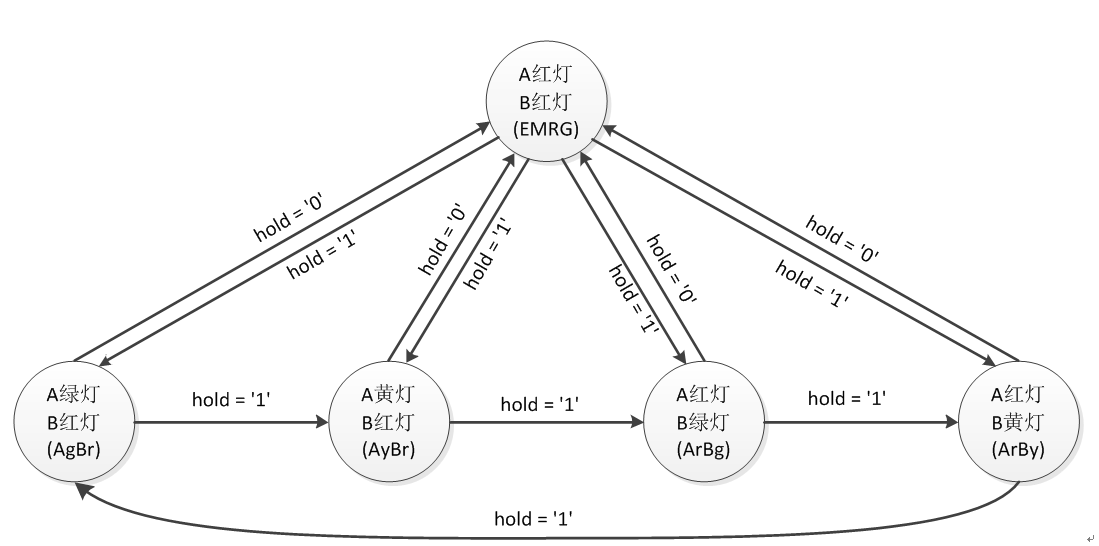

本系统以秒为时间单位运行,其核心工作过程可用状态机进行描述:

EMRG:紧急制动状态,东西(A)方向红灯亮,南北(B)方向红灯亮,当紧急制动信号(hold=’0’)时进入这种状态;

AgBr:东西(A)方向绿灯亮,南北(B)方向红灯亮,此状态持续50秒的时间;

AyBr:东西(A)方向黄灯亮,南北(B)方向红灯亮,此状态持续5秒的时间;

ArBg:东西(A)方向红灯亮,南北(B)方向绿灯亮,此状态持续40秒的时间;

ArBy:东西(A)方向红灯亮,南北(B)方向黄灯亮,此状态持续5秒的时间。

图2.1 交通控制系统状态转移图

当紧急制动信号无效(hold=’1’)时,状态机按照AgBr->AyBr->ArBg->ArBy->AgBr循环;当紧急制动信号有效(hold=’0’) 时,状态机进入EMRG,两个方向红灯全亮,计数器停止计数;当紧急制动信号再恢复无效时,状态机会回到原来的状态继续执行。

三、系统框架

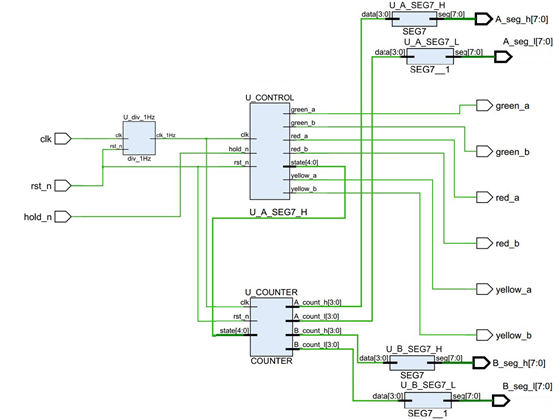

如图3.1所示,本系统主要有分频器、控制器、计数器和数码管译码器组成。

图3.1交通信号灯控制系统原理图

分频器将系统时钟分频成1Hz时钟信号,将其输出到信号灯控制器和倒计时计数器模块;控制器实现100s的计数(该计数值为AgBr,AyBr,ArBg,ArBy四个状态的时间总和,可由用户自行修改),100s是交通信号控制系统完成一次大循环所需的时间,在该时间内控制系统的状态转移以及AB两路信号的输出;倒计时模块实现50s、45s和5s的倒计时,该计数值可由用户自行修改;数码管译码模块负责将一位十进制数转换成对应的数码管段码值。

四、模块设计

1、分频器设计

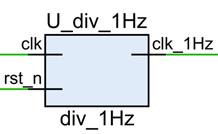

负责将输入的系统时钟(通常以MHz为量级)分频成1Hz时钟信号,供后级模块使用。

其接口信号如图4.1所示,clk为系统时钟信号;rst_n为系统复位信号,低电平有效;clk_1Hz为输出信号。除此之外,该模块向上一级模块提供一个参数接口,用于配置当前系统时钟。

图4.1 分频器模块接口

2、控制器设计

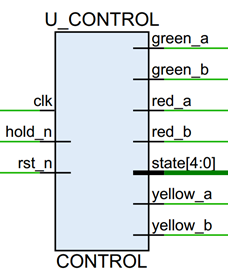

负责在时钟信号的控制下,交替控制两路红绿黄信号的输出;当出现紧急状态时,可手动控制两路的信号灯输出红色;当紧急状态解除后,恢复到进入紧急状态之前的状态。

各个状态之间的切换使用状态机来实现,状态机采用三段式独热编码,其中5'b00001表示EMRG、5'b00010表示AgBr、5'b00100表示AyBr、5'b01000表示ArBg、5'b10000表示ArBy。

其接口信号如图4.2所示,clk为1Hz时钟信号;rst_n为系统复位信号,低电平有效;hold_n为紧急制动输入,低电平有效;red_a,green_a,yellow_a, red_b,green_b,yellow_b分别为AB两路的红绿黄交通信号灯输出;state表示当前交通信号灯的状态,该信号输出到倒计时模块。

图4.2 控制器模块接口

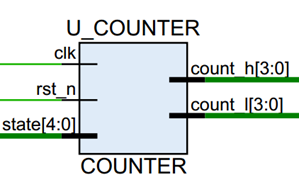

3、计数器设计

负责在时钟信号的控制下,对每一个state进行倒计时,倒计时的初值由用户设置;并将该倒计时按十位和个位分别输出。

其接口信号如图4.3所示,clk为1Hz时钟信号;rst_n为系统复位信号,低电平有效;state为控制器输出,每当state改变时,计数器重载计数初值并开始倒计时;count_h,count_l分别为倒计时数值的十位和个位,输出到数码管译码模块。

图4.3 计数器模块接口

图4.3 计数器模块接口

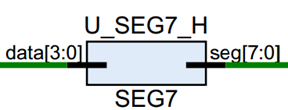

4、数码管译码器设计

将一位十进制数转换为数码管对应的段码值,数码管采用共阳极接法。

其接口信号如图4.4所示,data为一位十进制数输入;seg为8比特段码值输出,信号按照从低到高的顺序依次为数码管的dp、seg_a、seg_b、seg_c、seg_d、seg_e、seg_f、seg_g。

图4.4 数码管译码模块接口

五、验证项

由于该设计顶层除时钟和复位信号外,仅有一个紧急制动(hold)信号,因此只需要对该信号进行验证即可。

方法:产生一个随机的时间(时间值为5000000 ± 500ns),系统运行到该时间以后,使hold_n拉低并保持10000 ± 1000ns,观察此时系统的运行状态;重复5次。

六、仿真结果

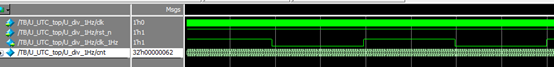

1、分频器仿真结果

图6.1分频器仿真结果

在仿真环境下使用的分频系数是100。

2、控制器仿真结果

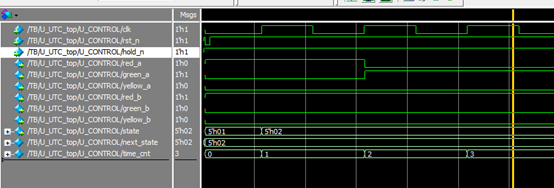

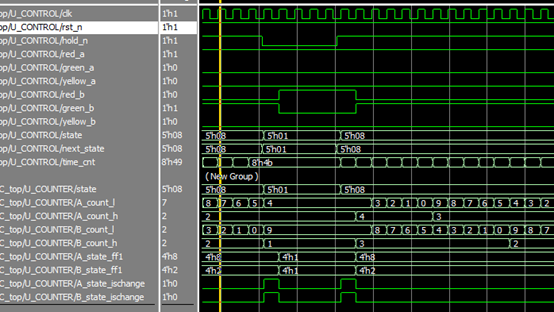

如图6.2所示,当系统复位或初始化时,控制器会短暂的进入一个紧急状态,1s以后开始正常工作。

图6.2 复位之后仿真结果

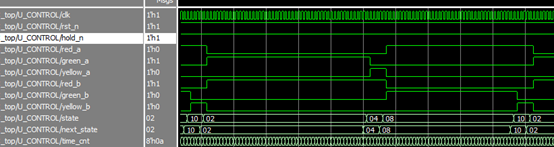

系统正常运行仿真结果如图6.3所示,A路绿灯持续50s后进入黄灯状态,此时B路一直处于红灯状态;B路绿灯持续40s后进入黄灯状态,此时A路一直处于红灯状态。

图6.3 正常运行仿真结果

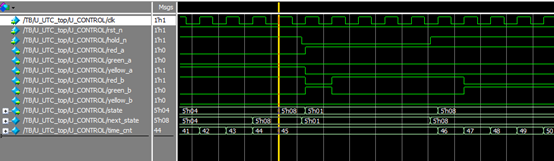

如图6.4所示,当hold按下时,系统进入紧急制动状态。此时AB两路均亮红灯,倒计时暂停;当hold释放时,系统恢复到进入紧急状态之前的状态,倒计时继续。

图6.4 紧急制动状态仿真

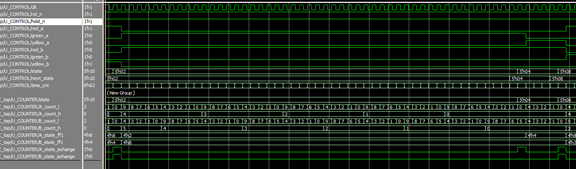

3、计数器仿真结果

系统正常运行时计数器各信号如图6.5所示,此时A路绿灯时间为50s,黄灯时间为5s,红灯时间45秒;B路绿灯时间为40s,黄灯时间为5s,红灯时间55秒。

图6.5 正常运行仿真结果

当出现紧急状态时,两路均停止计时;退出紧急状态后恢复计时。

图6.6 紧急状态仿真结果

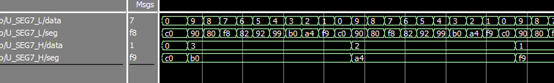

4、数码管译码仿真结果

数码管采用共阳极接法:

图6.7 数码管译码仿真结果

以下是控制器的部分代码:

1 //================================================================================================== 2 // Filename : control.v 3 // Created On : 2016-06-19 10:21:38 4 // Last Modified : 2016-06-22 20:15:01 5 // Revision : 6 // Author : christ_song 7 // Company : Xidian ISN 8 // Email : christsong0127@gmail.com 9 // 10 // Description : 控制两路红绿灯的状态切换 11 // hold信号表示紧急制动 12 // 13 //================================================================================================== 14 `include "define.v" 15 16 module CONTROL( 17 input clk, 18 input rst_n, 19 input hold_n, 20 output reg red_a, 21 output reg green_a, 22 output reg yellow_a, 23 output reg red_b, 24 output reg green_b, 25 output reg yellow_b, 26 //与倒计时模块的接口 27 output reg [4:0] state 28 ); 29 30 // localparam EMRG = 5'b00001; 31 // localparam AgBr = 5'b00010; 32 // localparam AyBr = 5'b00100; 33 // localparam ArBg = 5'b01000; 34 // localparam ArBy = 5'b10000; 35 localparam TimeRound = `AgBr_time + `AyBr_time + `ArBg_time + `ArBy_time + 8'd3; 36 37 reg [4:0] next_state; 38 reg [7:0] time_cnt; 39 always @(posedge clk or negedge rst_n) 40 if (!rst_n) 41 time_cnt <=#1 8'b0; 42 else if(!hold_n) 43 time_cnt <=#1 time_cnt; 44 else if(time_cnt >= TimeRound) 45 time_cnt <=#1 8'b0; 46 else 47 time_cnt <=#1 time_cnt + 1'b1; 48 49 always @(posedge clk or negedge rst_n) 50 if (!rst_n) 51 state <=#1 `EMRG; 52 else 53 state <=#1 next_state; 54 always @(*) 55 case(state) 56 `EMRG: 57 if(!hold_n) 58 next_state = `EMRG; 59 else if(time_cnt < `AgBr_time) 60 next_state = `AgBr; 61 else if(time_cnt < `AgBr_time + `AyBr_time + 8'd1) 62 next_state = `AyBr; 63 else if(time_cnt < `AgBr_time + `AyBr_time + `ArBg_time + 8'd2) 64 next_state = `ArBg; 65 else 66 next_state = `ArBy; 67 `AgBr: 68 if(!hold_n) 69 next_state = `EMRG; 70 else if(time_cnt < `AgBr_time) 71 next_state = `AgBr; 72 else 73 next_state = `AyBr; 74 `AyBr: 75 if(!hold_n) 76 next_state = `EMRG; 77 else if(time_cnt < `AgBr_time + `AyBr_time + 8'd1) 78 next_state = `AyBr; 79 else 80 next_state = `ArBg; 81 `ArBg: 82 if(!hold_n) 83 next_state = `EMRG; 84 else if(time_cnt < `AgBr_time + `AyBr_time + `ArBg_time + 8'd2) 85 next_state = `ArBg; 86 else 87 next_state = `ArBy; 88 `ArBy: 89 if(!hold_n) 90 next_state = `EMRG; 91 else if(time_cnt < TimeRound) 92 next_state = `ArBy; 93 else 94 next_state = `AgBr; 95 default: 96 next_state = `EMRG; 97 endcase 98 always @(posedge clk or negedge rst_n) 99 if (!rst_n) begin 100 {red_a, green_a, yellow_a} <=#1 3'b100; 101 {red_b, green_b, yellow_b} <=#1 3'b100; 102 end 103 else 104 case(state) 105 `EMRG: 106 begin 107 {red_a, green_a, yellow_a} <=#1 3'b100; 108 {red_b, green_b, yellow_b} <=#1 3'b100; 109 end 110 `AgBr: 111 begin 112 {red_a, green_a, yellow_a} <=#1 3'b010; 113 {red_b, green_b, yellow_b} <=#1 3'b100; 114 end 115 `AyBr: 116 begin 117 {red_a, green_a, yellow_a} <=#1 3'b001; 118 {red_b, green_b, yellow_b} <=#1 3'b100; 119 end 120 `ArBg: 121 begin 122 {red_a, green_a, yellow_a} <=#1 3'b100; 123 {red_b, green_b, yellow_b} <=#1 3'b010; 124 end 125 `ArBy: 126 begin 127 {red_a, green_a, yellow_a} <=#1 3'b100; 128 {red_b, green_b, yellow_b} <=#1 3'b001; 129 end 130 endcase 131 132 endmodule

仿真代码:

1 //================================================================================================== 2 // Filename : TB.v 3 // Created On : 2016-06-19 10:05:43 4 // Last Modified : 2016-06-21 21:03:59 5 // Revision : 6 // Author : christ_song 7 // Company : Xidian ISN 8 // Email : christsong0127@gmail.com 9 // 10 // Description : Testbench for Urban Traffic Control system 11 // 12 // 13 //================================================================================================== 14 `timescale 1ns/1ps 15 16 module TB; 17 18 reg clk; 19 reg rst_n; 20 reg hold_n; 21 wire red_a; 22 wire green_a; 23 wire yellow_a; 24 wire red_b; 25 wire green_b; 26 wire yellow_b; 27 wire [7:0] A_seg_l; 28 wire [7:0] A_seg_h; 29 wire [7:0] B_seg_l; 30 wire [7:0] B_seg_h; 31 32 UTC_top #(100) U_UTC_top 33 ( 34 .clk(clk), 35 .rst_n(rst_n), 36 .hold_n(hold_n), 37 .red_a(red_a), 38 .green_a(green_a), 39 .yellow_a(yellow_a), 40 .red_b(red_b), 41 .green_b(green_b), 42 .yellow_b(yellow_b), 43 .A_seg_l(A_seg_l), 44 .A_seg_h(A_seg_h), 45 .B_seg_l(B_seg_l), 46 .B_seg_h(B_seg_h) 47 ); 48 49 initial begin 50 clk = 0; 51 rst_n = 1; 52 hold_n = 1; 53 #30 54 sys_rst(100); 55 repeat(5) hold; 56 #10000; 57 $stop; 58 end 59 60 always #5 clk = ~clk; 61 62 task sys_rst; 63 input [10:0] rst_time; //调用task的时候,将参数赋值给rst_time 64 begin 65 rst_n = 0; 66 #rst_time; 67 rst_n = 1; 68 end 69 endtask 70 71 task hold; 72 integer i,hold_time; 73 begin 74 i = 5000000 + $random % 500; 75 hold_time = 10000 + $random % 1000; 76 #i 77 hold_n = 0; 78 #hold_time; 79 hold_n = 1; 80 end 81 endtask 82 83 endmodule

#2020.10.23 更新#

早就不维护博客了,没想到还有人会看,放个链接吧,不提供任何帮助,需要请自取!

链接: https://pan.baidu.com/s/1_5UXqXqatNDOjauQODLUDg 提取码: sd8t