在第一篇文章中,我简单介绍了一下PLL的相关的基础知识,在这篇文章中,我们主要介绍怎么修改官方的verilog程序,然后应用到我们的工程中去。

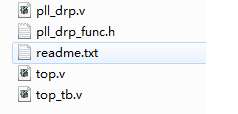

1. 参考文件主要有以下几个:

pll_drp.v 主要是PLL_DRP这个模块怎么使用,里面主要包含了一个rom和一个状态机,还有一些参数的计算,引用的是pll_drp_func.h这个文件中的函数,计算好之后,然后初始化到rom中,readme是一些更新信息,也可以打开看看,

top文件是一些模块的例化,以及输出时钟的原语,最后的top_tb.v文件就是我们的测试文件了。拿到这份功成后,我们先仿真看一下吧。

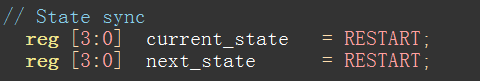

2.笔者应用的是ise + modelsim仿真的,在笔者仿真时发现一个错误,就是在pll_drp.v文件中,需要把

这两个信号定义道RESTART之后,要不然不能仿真的。然后我把仿真文件的最后一句注释了,这样就可以一直有信号了://$stop ......

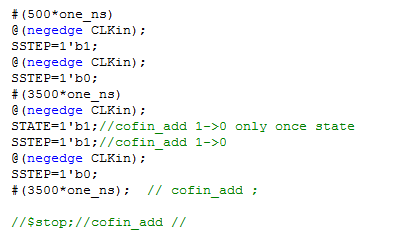

接着,启动仿真吧:

这里由几个控制信号需要说明:在系统刚上电时,SRDY会输出一个clk的高电平,之后才可以进行重新配置PLL的操作,配的过程就是使能STTEP信号,并不在STEEP信号有效的情况下判断STATE的值是1还是0,选择重配的状态时S1还是S2,之后等待SRDY再次有效之后就说明PLL已经配置ok了,这里用户可以自己在加自己的状态,比如S3。。。,但是需要例化rom,而且STAE信号要改成2bit来区分是哪个状态,也就是照猫画虎。

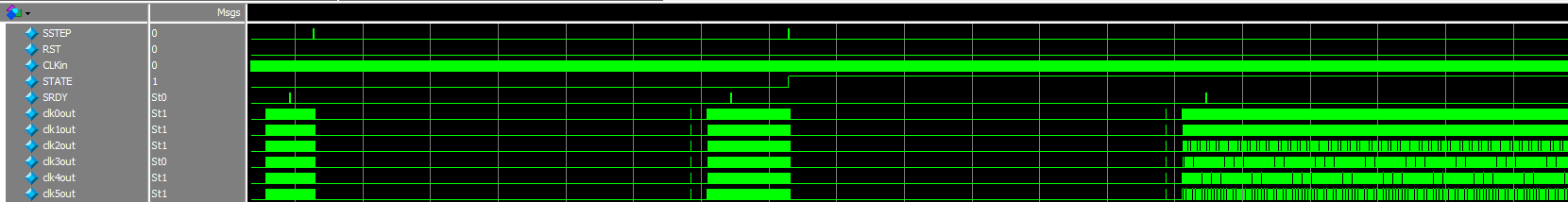

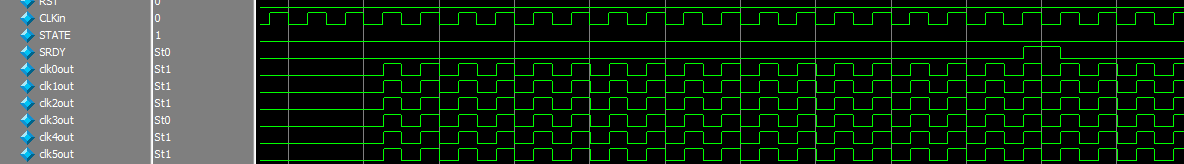

接下来放大看一下,第一部分(和系统时钟一模一样):

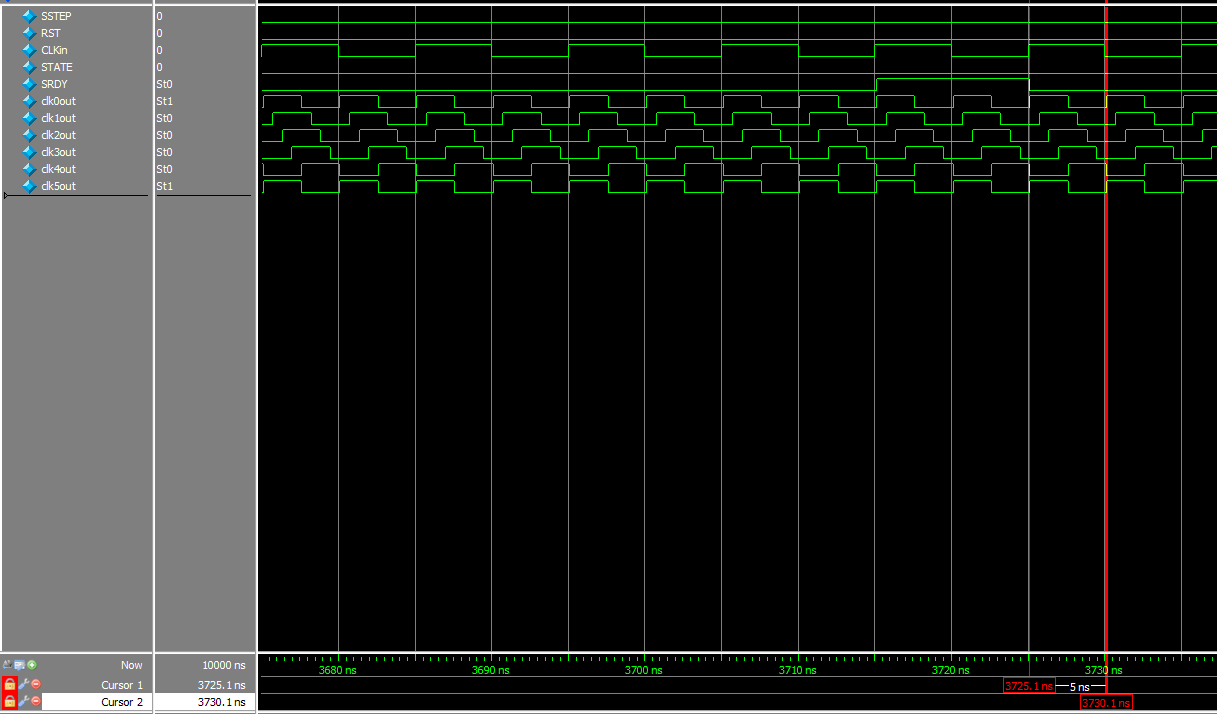

第二部分(加载第一组参数S1):

6路时钟都倍频了一倍,且相位都有变化,好激动啊,由官方参考的代码心里安心多了。。。。QAQ

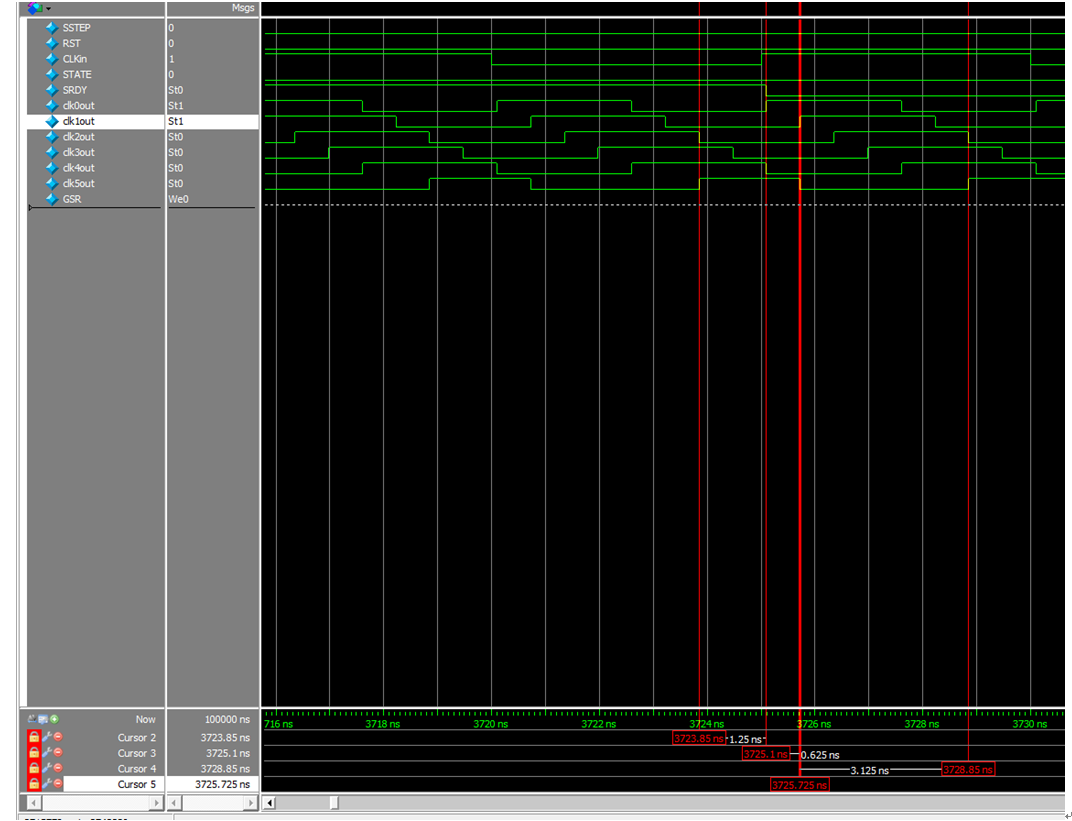

详细分析一下:

从图中可以看到0.625的45°相移,可以看到周期是3.125+0.625+1.25 ns = 5ns,占空比是50%,和我们的计算参数是一致的。至此,我们已经了解了PLL重配置的基本概念和简单的修改方法了,参数的计算公式如上所示,值得注意的是反馈的参数取值范围是1-64,分频的参数取值范围是1-128,千万不能超过这个范围,否则可能会出错,公式在下面。。。

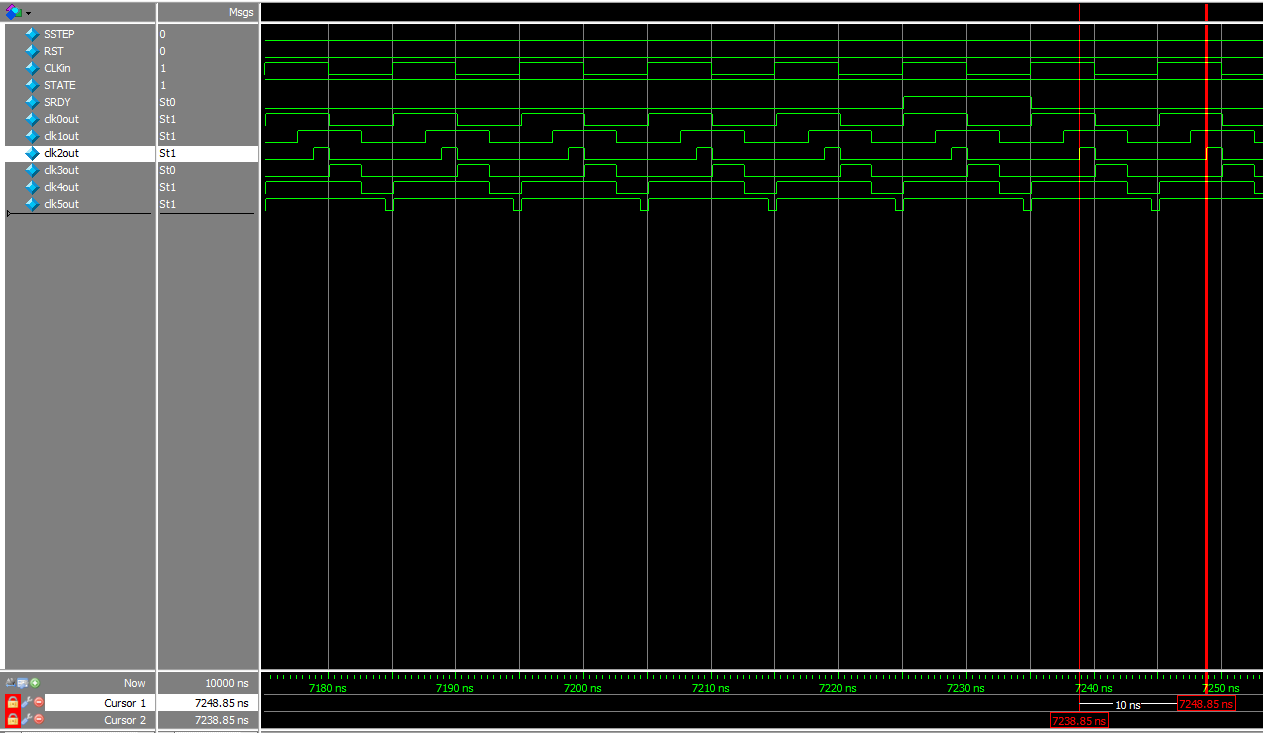

第三部分(加载第二组参数S2):

相位和占空比也发生了变化。。。。

3.那么我们如何修改才能应用到我们的工程中去呢。

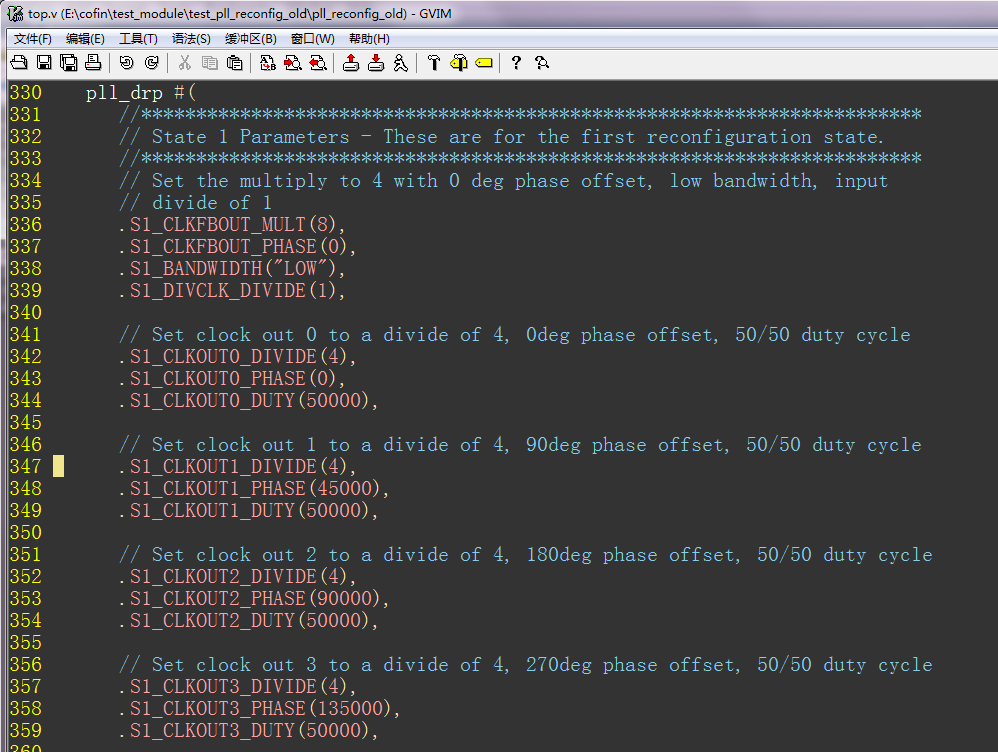

打开top文件,可以看到如下所示的例化参数:

这些参数该怎么设置是什么意思呢?如下:

计算参数说明:

输出频率 :(反馈系数 / 设置输出的系数)* 输入时钟 (注:假设输入分频为1)

输出相移 :数值 / 1000

输出占空比 :数值 / 100_000

举例:

如上图设置的:8 / 4 * 100Mhz = 200Mhz, 对应的时钟周期是5ns。

45000 / 1000 = 45度。

45°* 5ns/360° = 0.625ns

50000 / 100_000 = 0.5 占空比

看到这里相信聪敏的你已经知道怎么玩这份工程了,只要修改这里的参数就可以了。

5.总结:

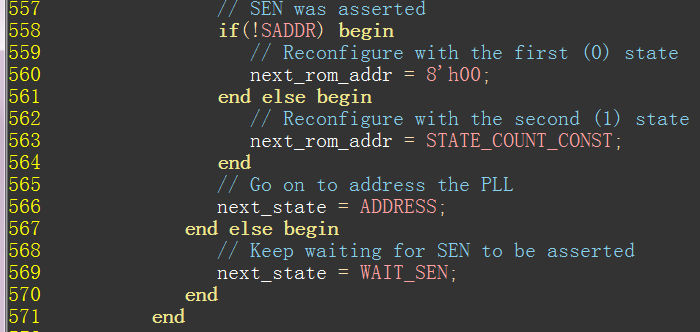

本文主要阐述了官方工程如何修改,比较浅易懂的介绍了PLL的重配置,就是利用ROM来配置PLL,用户可以修改官方的例化的参数,也可以自己再添加相应的n组参数去初始化rom,但是状态机哪里也需要修改呢,状态机的转移图在上一篇文章中已经分析过了,这里我贴一下需要修改状态机的位置,打开pll_drp.v,如图:

这里会判断SADDR的值,然后选择开始配置rom的地址,可自行添加修改,本文可能还有一些没有说到的地方,大家自己动手试试吧,欢迎和我讨论,,转贴请注明出处,谢谢,下一节我们谈论一下如何更灵活的动态配置PLL,需要工程文件请向博主索要。

---------cofin_add