第一章:

最近百度了一些fir滤波器的资料,都没有自己想要的。容我吐槽一大段文字>。。

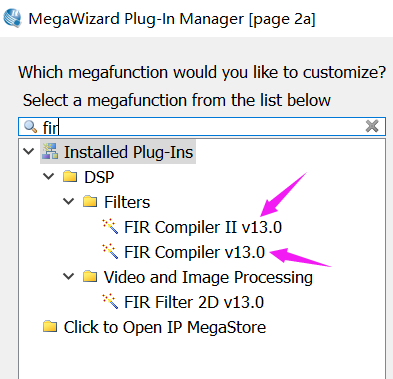

在旧版的quartus中,比如13.0,有两个fir滤波器的选项,如下所示:

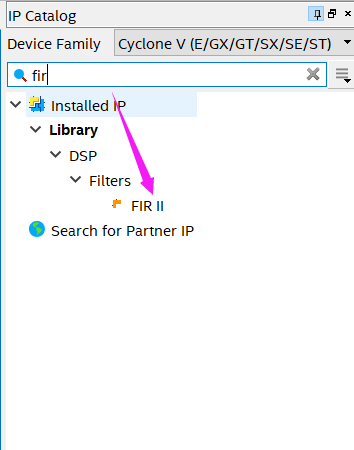

网上很多都是讲不带II的那个,而在新版的quartus已经找不到这个IP了,如下所示:

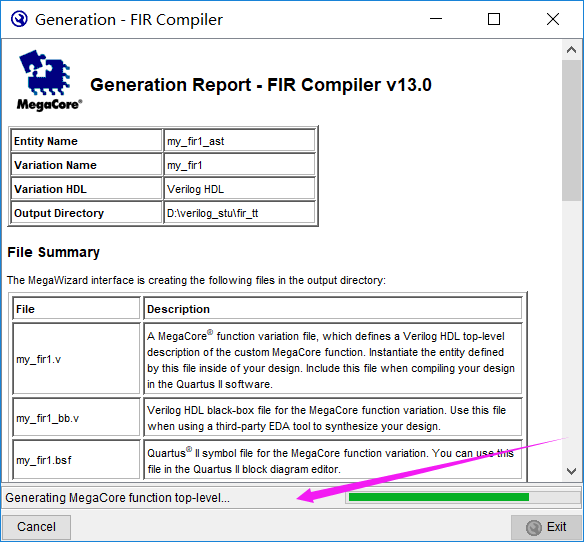

对于第一版的FIT滤波器,在旧的版本中,经常生成不了fir这个滤波器(quartus 的软件问题让人抓狂。。)

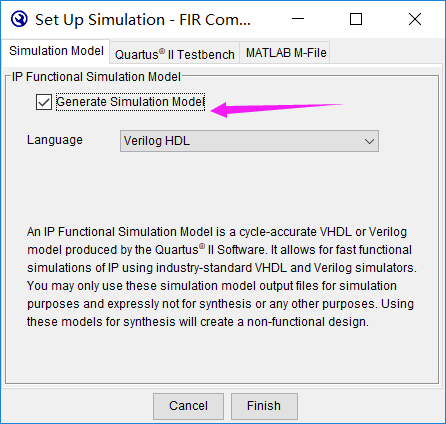

选择生成仿真模型

(卡在这里不动了。。我会告诉你不勾选生成仿真模型就能生成成功了嘛。。呵)

哎。

第二章:

解决方法:

1.我不看仿真了。。(我不)

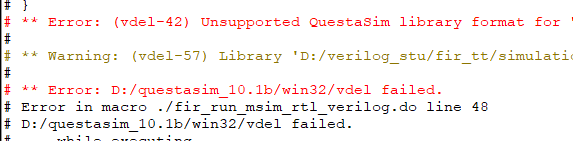

2.于是我按照普通的方法,生成FIR II,然后按照一般的方法联合仿真。然后就会报错。。如下所示:

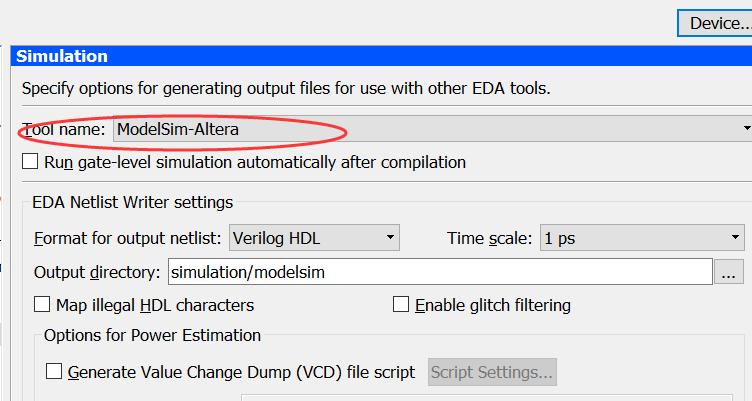

3.正确的方法只要使用quartus自带的modelsim,仿真就可以(其实加入相应的库也可以仿真的。。。不想研究了)。如下所示:

第三章:

仿真matlab中的输入数据:(有兴趣的去研究,有两段话,怎么加入数据,以及怎么输出数据,matlab是不是可以导入txt分析呢?。)

`timescale 1 ps/ 1 ps

module FirIPDa_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg [11:0] Xin;

reg clk;

reg reset_n;

// wires

wire [24:0] Yout;

//wire clk_data;

// assign statements (if any)

FirIPDa i1 (

// port map - connection between master ports and signals/registers

.Xin(Xin),

.Yout(Yout),

.clk(clk),

//.clk_data(clk_data),

.reset_n(reset_n)

);

parameter clk_period=626; //设置时钟信号周期(频率):1.6MHz

//parameter clk_period_data=clk_period*13;

parameter clk_half_period=clk_period/2;

//parameter clk_half_period_data=clk_half_period*13;

parameter data_num=2000; //仿真数据长度

parameter time_sim=data_num*clk_period; //仿真时间

initial

begin

//设置时钟信号初值

clk=1;

//clk_data=1;

//设置复位信号

reset_n=0;

#10000 reset_n=1;

//设置仿真时间

#time_sim $finish;

//设置输入信号初值

Xin=12'd10;

end

//产生时钟信号

always

#clk_half_period clk=~clk;

//always

// #clk_half_period_data clk_data=~clk_data;

//从外部TX文件(SinIn.txt)读入数据作为测试激励

integer Pattern;

reg [11:0] stimulus[1:data_num];

initial

begin

//文件必须放置在"工程目录simulationmodelsim"路径下

//$readmemb("E4_9_Bin_noise.txt",stimulus);

$readmemb("E4_9_Bin_s.txt",stimulus);

Pattern=0;

repeat(data_num)

begin

Pattern=Pattern+1;

Xin=stimulus[Pattern];

//#clk_period_data;//数据周期为时钟周期的8倍

#clk_period;//数据周期为时钟周期的8倍

end

end

//将仿真数据dout写入外部TXT文件中(out.txt)

integer file_out;

initial

begin

//文件放置在"工程目录simulationmodelsim"路径下

//file_out = $fopen("E4_9_Noiseout.txt");

file_out = $fopen("E4_9_Sout.txt");

if(!file_out)

begin

$display("could not open file!");

$finish;

end

end

wire rst_write;

wire signed [24:0] dout_s;

assign dout_s = Yout; //将dout转换成有符号数据

assign rst_write = clk& (reset_n);//产生写入时钟信号,复位状态时不写入数据

always @(posedge rst_write )

$fdisplay(file_out,"%d",dout_s);

endmodule

欢迎大家一起交流,Q群:912014800。