转帖请注明转自http://www.cnblogs.com/connorzx/p/3547673.html

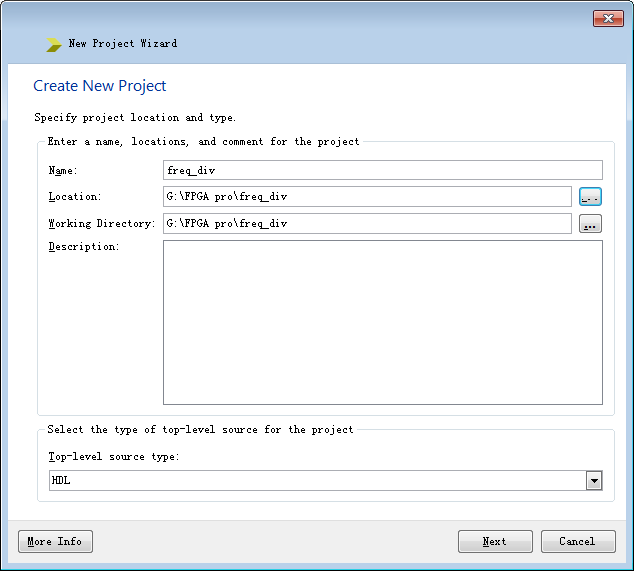

一、新建工程

1.点击File->New Project,

2.点击Next

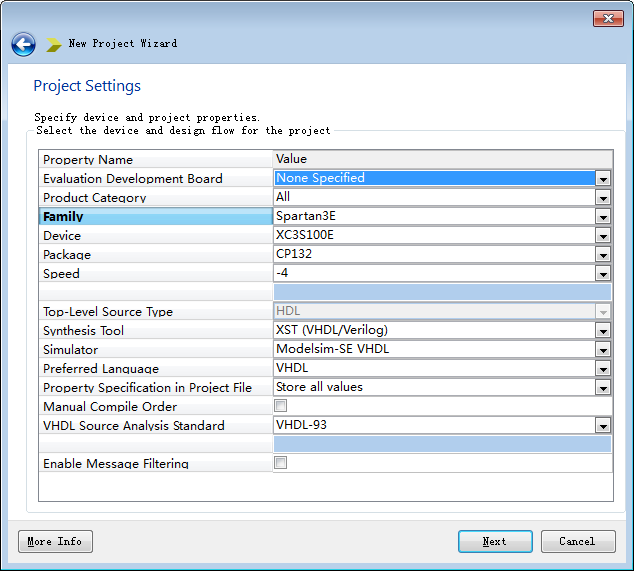

注:此处的simulator已经和modelsim关联,未关联可以先选默认。

3.点击Next,点击Finish。

二、新建源文件

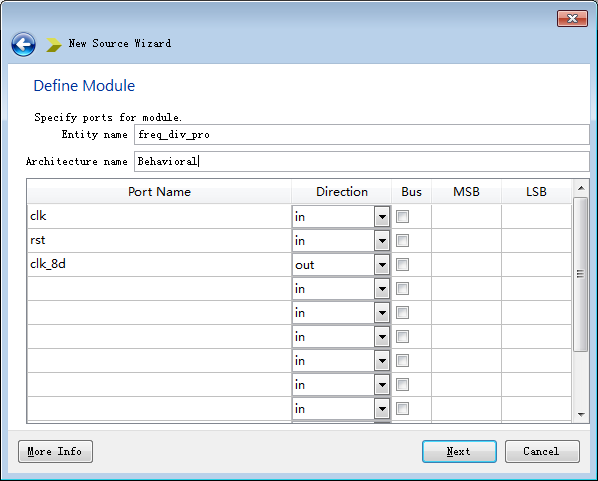

右击程序文件,点击New Source。选择VHDL Module。

输入端口设置,如下图所示

三、编写程序代码

1 library IEEE; --库引用 2 use IEEE.STD_LOGIC_1164.ALL; 3 use IEEE.STD_LOGIC_ARITH.ALL; 4 use IEEE.STD_LOGIC_UNSIGNED.ALL; 5 6 entity freq_div_pro is --实体,端口定义 7 Port ( clk : in STD_LOGIC; 8 rst : in STD_LOGIC; 9 clk_8d : out STD_LOGIC); 10 end freq_div_pro; 11 12 architecture Behavioral of freq_div_pro is --结构体定义 13 signal cnt:STD_LOGIC_VECTOR(1 downto 0); 14 signal tmp:STD_LOGIC; --定义两个信号 15 begin 16 process(rst,clk) --主进程 17 begin 18 if(rst = '1')then --异步清零 19 cnt(1 downto 0) <= "00"; 20 tmp <= '0'; 21 elsif(clk'event and clk ='1')then --上升沿有效 22 cnt(1 downto 0) <= cnt(1 downto 0) + 1; --计数 23 if(cnt(1 downto 0)="11")then 24 tmp <= not tmp; --输出翻转,可以用T'触发器实现 25 cnt(1 downto 0) <= "00"; --计数器复位 26 end if; 27 end if; 28 end process; 29 clk_8d <= tmp; --输出 30 31 end Behavioral;

进行语法检查

然后点击Synthesize –XST 和Implement Design。

四、编写测试基准

选择simulation窗口,新建一个VHDL testbench,

编写代码如下:

1 library IEEE; 2 use IEEE.STD_LOGIC_1164.ALL; 3 use IEEE.STD_LOGIC_ARITH.ALL; 4 use IEEE.STD_LOGIC_UNSIGNED.ALL; 5 6 ENTITY freq_div_test IS 7 END freq_div_test; 8 9 ARCHITECTURE behavior OF freq_div_test IS 10 11 -- Component Declaration for the Unit Under Test (UUT) 12 13 COMPONENT freq_div_pro 14 PORT( 15 clk : IN std_logic; 16 rst : IN std_logic; 17 clk_8d : OUT std_logic 18 ); 19 END COMPONENT; 20 21 22 --Inputs 23 signal clk : std_logic := '1'; 24 signal rst : std_logic := '1'; 25 26 --Outputs 27 signal clk_8d : std_logic; 28 -- Clock period definitions 29 constant clk_period : time := 20 ns; 30 31 BEGIN 32 -- Instantiate the Unit Under Test (UUT) 33 uut: freq_div_pro PORT MAP ( 34 clk => clk, 35 rst => rst, 36 clk_8d => clk_8d 37 ); 38 -- Clock process definitions 39 clk_process :process 40 begin 41 clk <= '0'; 42 wait for clk_period/2; 43 clk <= '1'; 44 wait for clk_period/2; 45 end process; 46 47 -- Stimulus process 48 stim_proc: process 49 begin 50 -- hold reset state for 100 ns. 51 rst<='0' after 100 ns; 52 wait; 53 end process; 54 END;

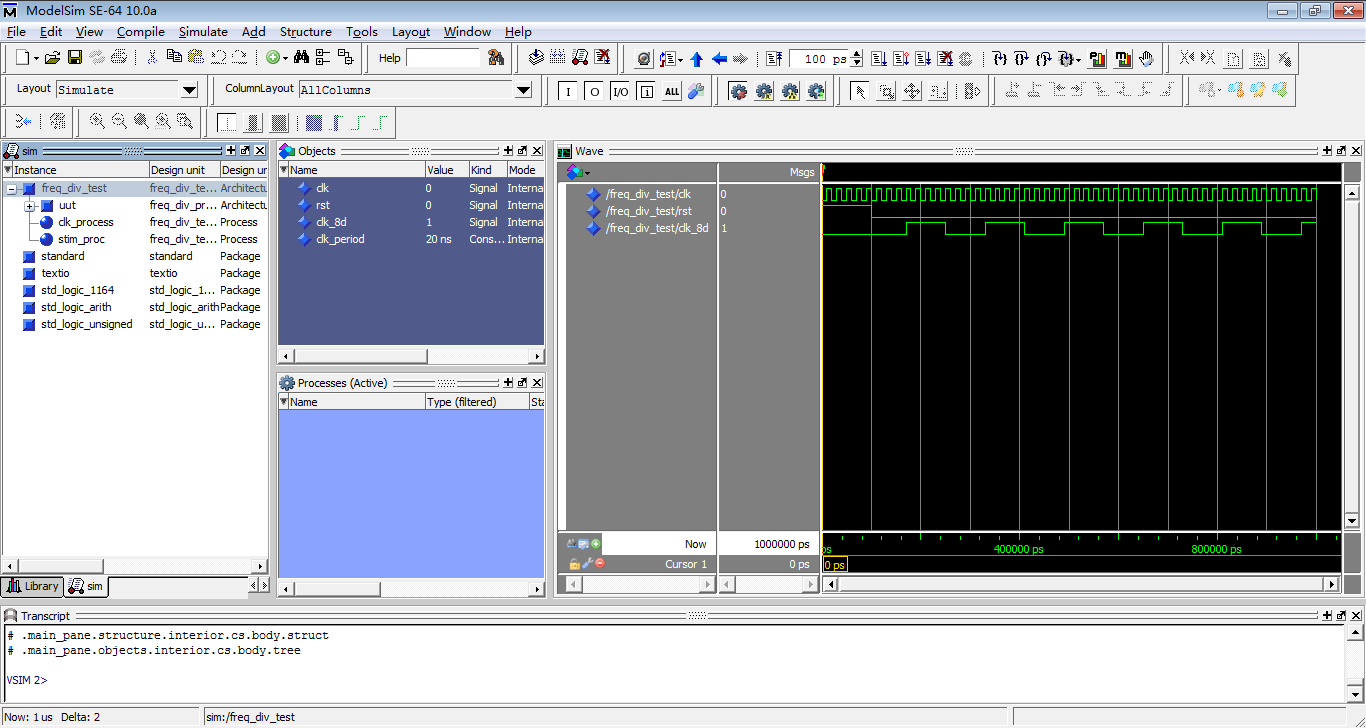

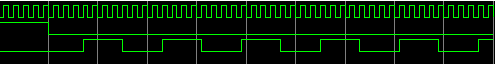

选择仿真程序文件,点击Simulate Behavioral Model,弹出Modelsim程序,可以看到如下结果

波形如下,

注:本实验采用Modelsim进行仿真分析,Modelsim软件以及Xilinx和Modesim关联方法请参照以下链接操作。

链接: http://pan.baidu.com/s/1eQj5rrW 密码: c1ca