1 cpu优化: 缓存

为了提高程序的运行的性能,现代cpu在很多方面对程序进行优化:

例如:cpu的高速缓存,尽可能的避免处理器访问主内存的时间开销,处理器大多会利用缓存来提高性能

cpu缓存分为三级缓存:

L1 一级缓存是cpu第一层高速缓存 分为数据缓存和指令缓存 一般服务器的cpu在32-4.96kb

L2 为了提高cpu的运算速度,在cpu外部放置高速存储器 即二级缓存

L3 现在都是内置的,作用,可以进一步降低内存的延迟,同时提升大数据计算时候处理器的性能,一般死多核公用l3缓存

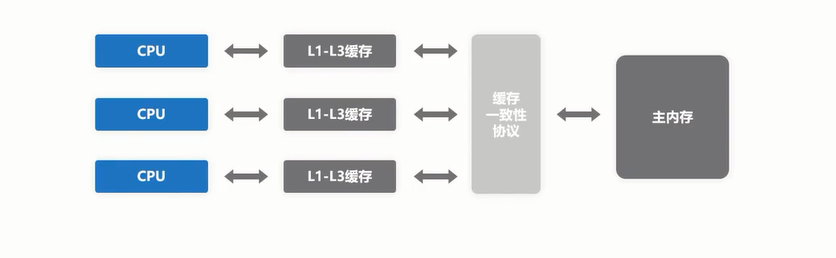

多处理器时候 单个cpu对缓存中的数据进行改动了,需要通知给其他的cpu 也就意味者,cpu的处理器要控制自己的读写操作

还要监听其他cpu的发出的通知,从而保证缓存的一致性

2 cpu优化:指令重排

指令重排的场景:当cpu的写缓存时候发现缓存区域正在被其他cpu占用,为了提高cpu的性能,可能会将后面的都缓存指令优先执行

并非随便重排:需要遵循as-if -serial语义

as-if -serial语义是指: 不管怎么重排序,程序的执行结果不会被改变,编译器和处理器都会遵循这个语义

也就是说,编译器和处理器不会对数据存在对的依赖关系的操作做重排序

存在问题:

1 cpu高速缓存下问题:

缓存中的数据与主内存的数据并不是实时同步的,各个cpu间的缓存数据也不是实时同步,各个cpu所看到的同一内存数据可能不一致

2 指令重排:

虽然遵循的as-if -serial 语义 仅仅在单个cpu自己执行的情况下保证结果正确

多核多线程 中,指令逻辑无法分辨因果关联 可能会出现程序乱执行,导致程序运行结果错误

解决方法: cpu提高内存屏障

1 写内存屏障: 在指令后插入store barrier,能让写入缓存的最新数据更新写入主内存,让其他线程可见

强制写入主内存,这个现实调用,cpu就不会因为性能问题去对指令重排

2 读内存屏障:在指令之前插入load barrier 可以让缓存缓存中的数据实现,强制从新主内存加载数据

强制读取主内存内容,让cpu缓存保持与之内存保持一致,避免了缓存导致的一致性问题