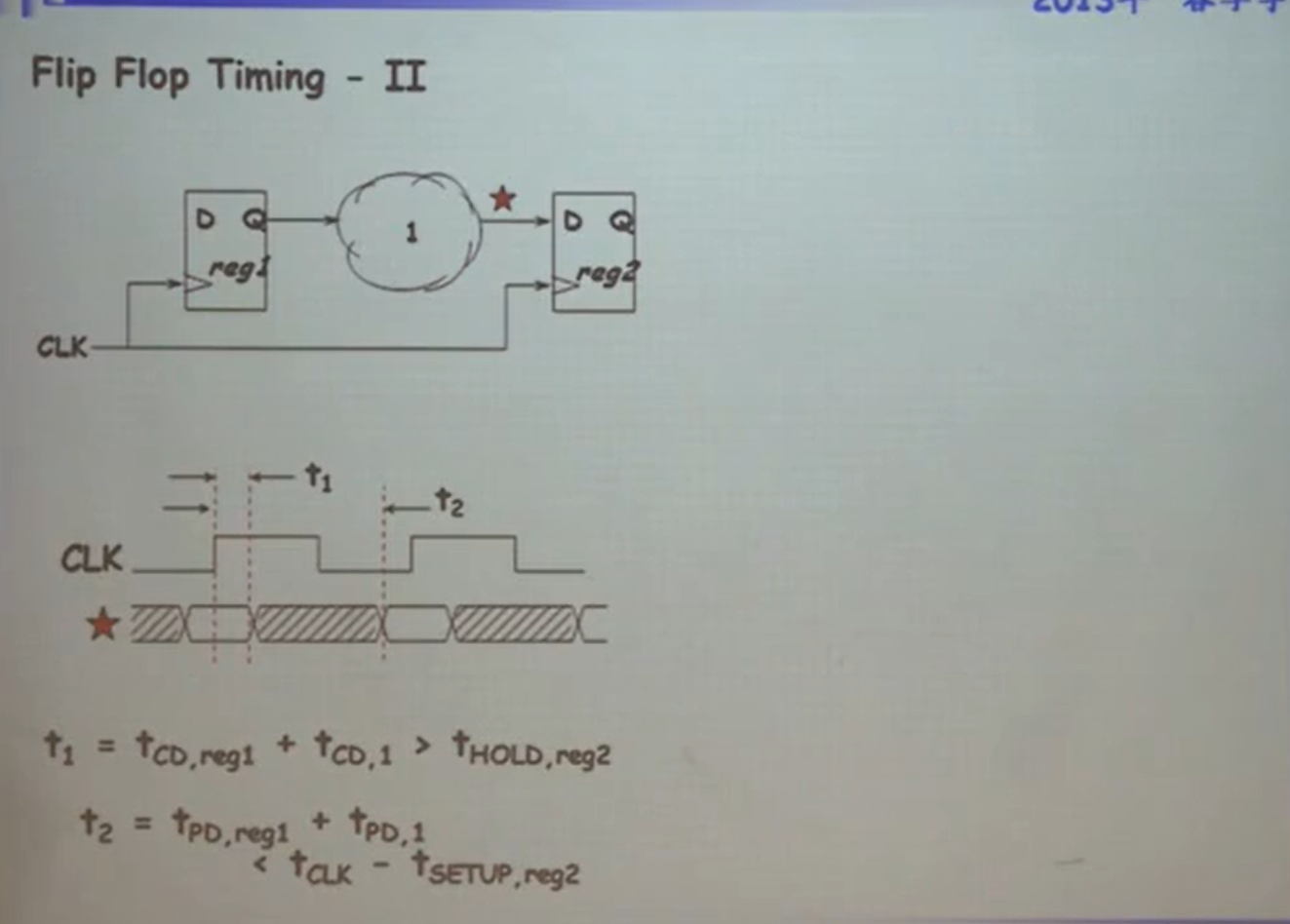

最高频率即触发信号周期取决于两个tpd相加最大的那一级。当为了增加中间组合逻辑级数tcd来满足 > thold时

只要触发信号周期 > 触发器1的tpd + 驱动方程的tpd + 触发器2的tsetup,就能满足触发器2的早来。整个同步时序电路的

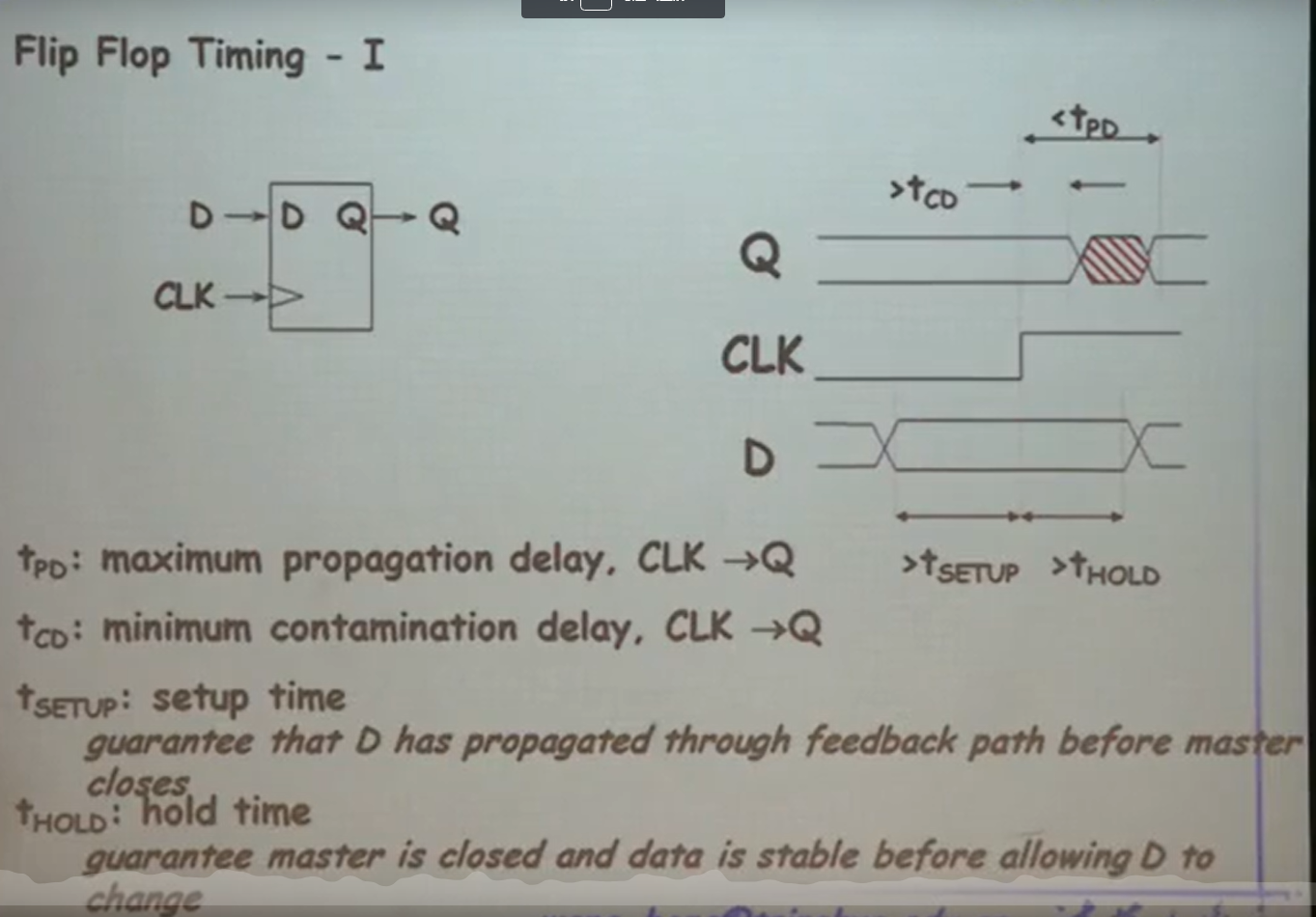

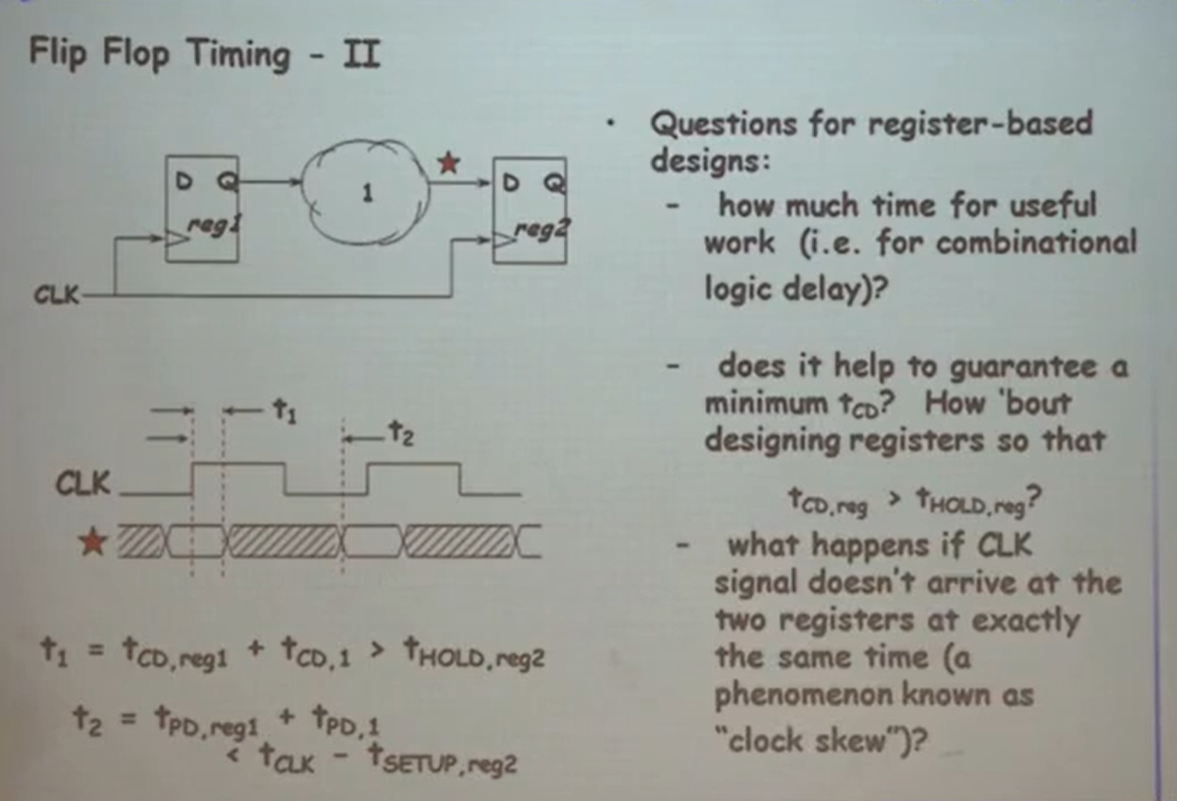

浮云表示驱动方程即触发器之间的组合逻辑电路,这个⭐就是驱动方程的结果,它要早于触发信号来晚于触发信号走:

必然会引起tpd增加进一步导致工作频率降低

只要触发器1的tcd + 驱动方程的tcd > 触发器2的thold,就能满足触发器2的晚走;

只要触发信号周期 > 触发器1tpd + 驱动方程tpd + 触发器2tpd,就能满足触发器2数据信号的早来。所以整个时序电路的最高频率

第三行改为:只要触发信号周期 > 触发器1tpd + 驱动方程tpd + 触发器2tsetup

即触发信号周期受限于两个tpd相加最大的那级。为了满足tcd > thold会增加触发器间逻辑器件,必然导致tpd增加进而导致工作频率降低

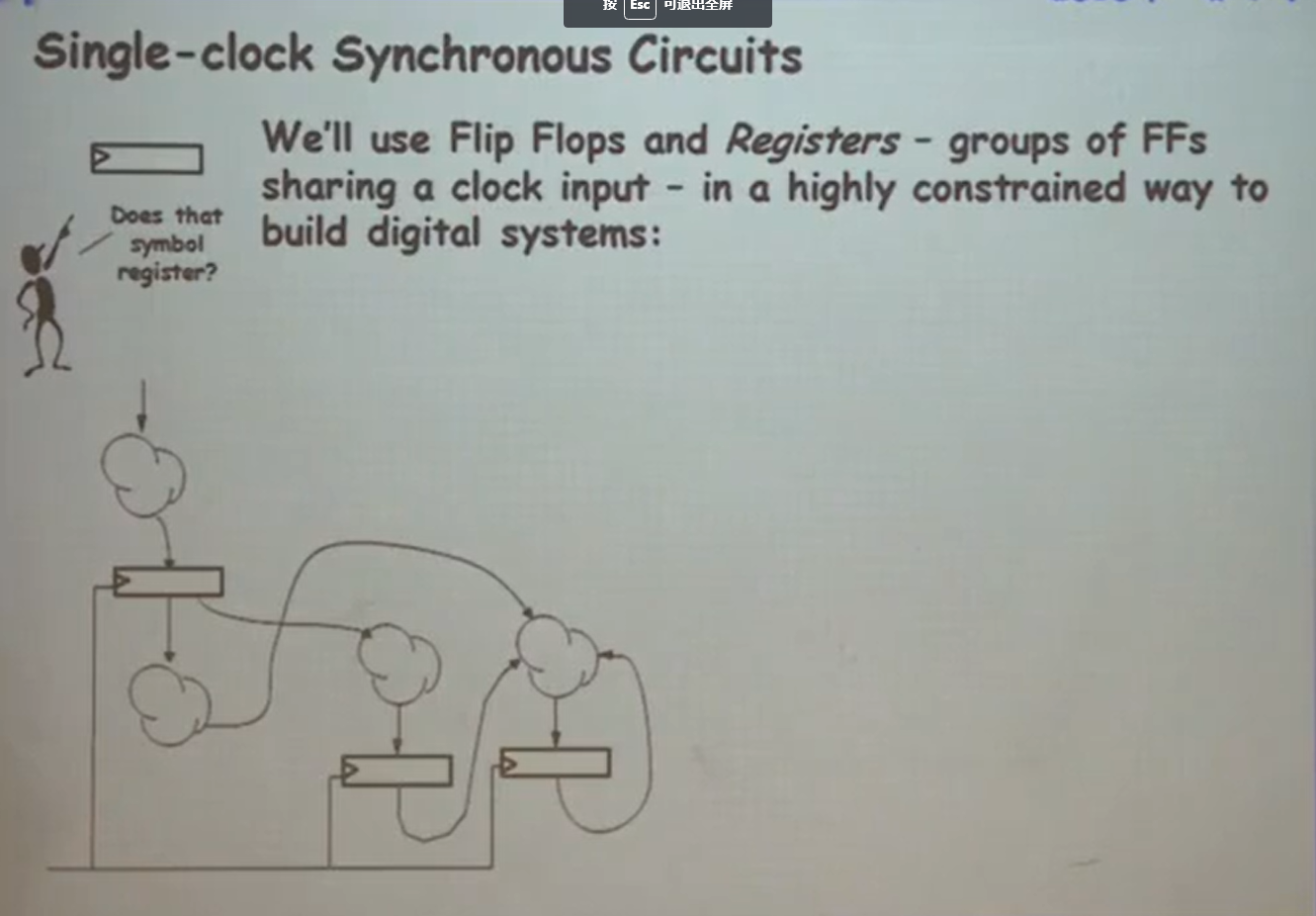

触发器在数字电路中的典型应用:

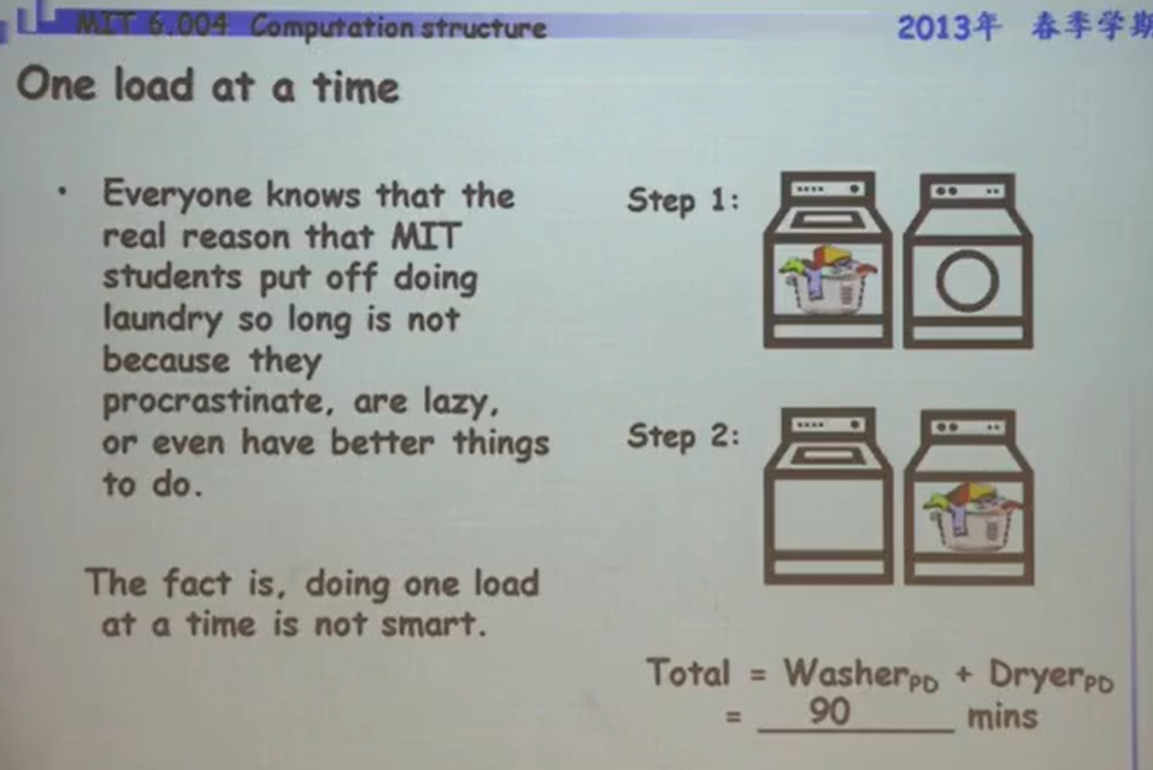

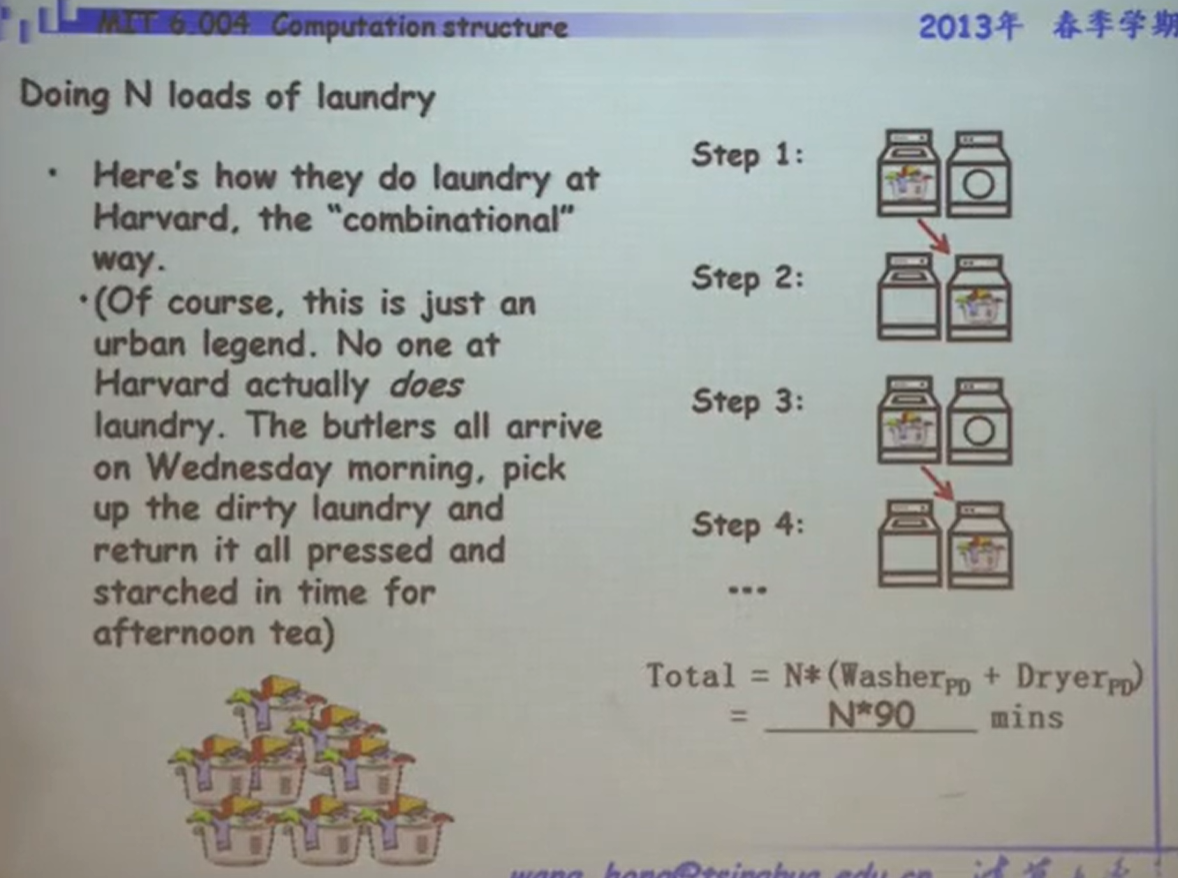

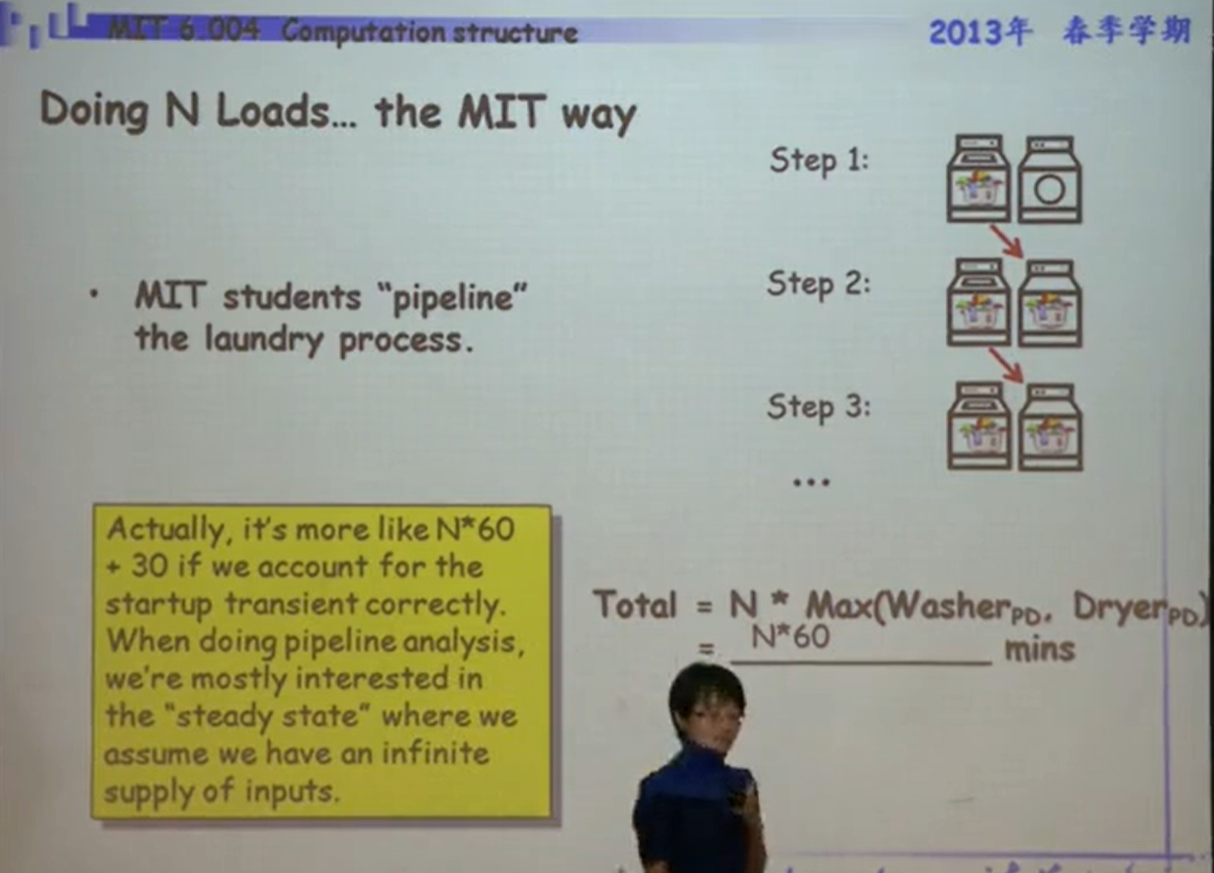

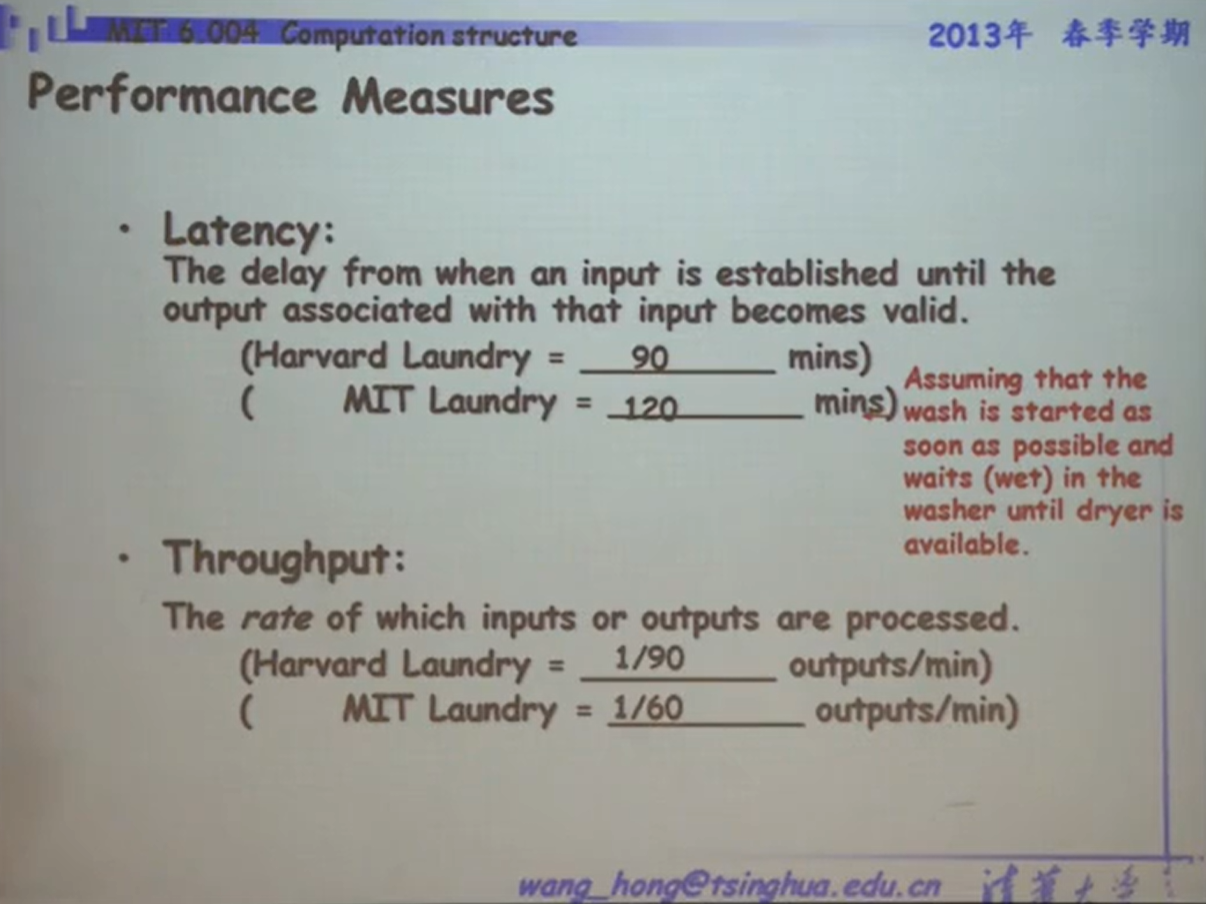

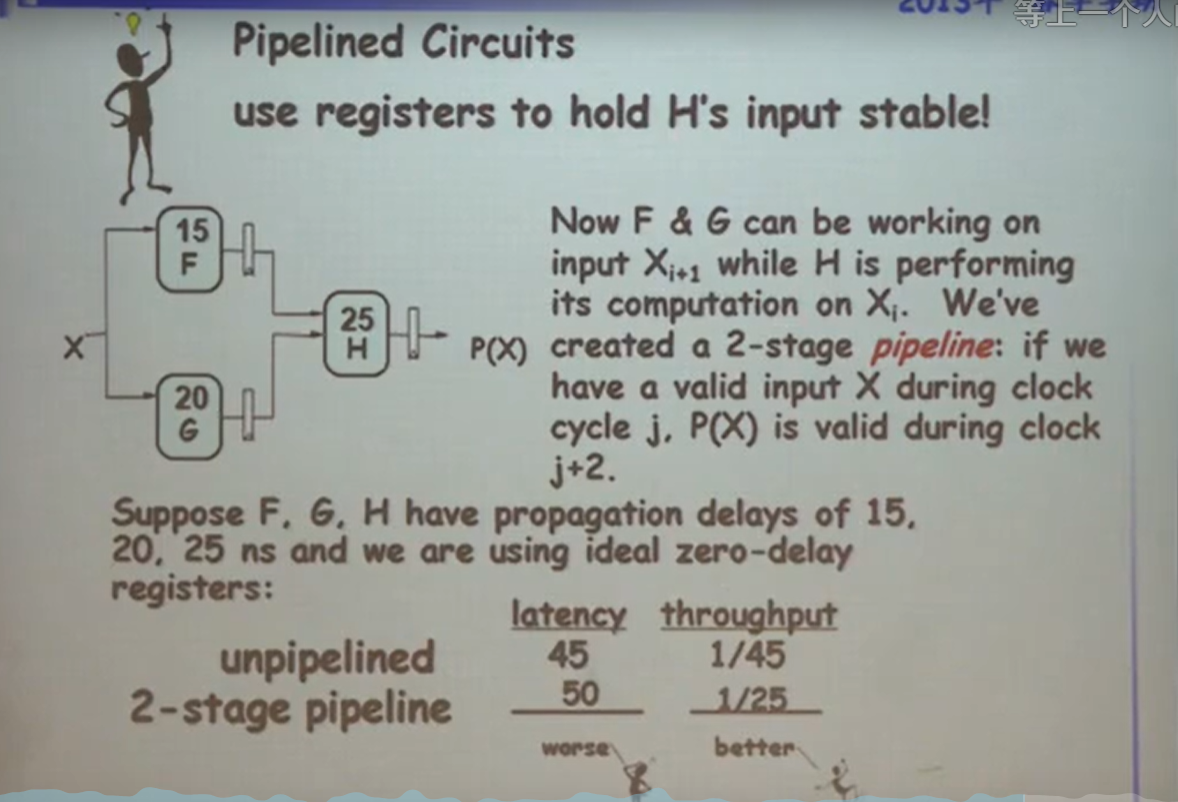

latency:延迟,完全执行一个任务所需的周期 throughput:吞吐率,单位时间内成功地传送数据的数量

20秒(并行算完F和G)+等5秒(等H腾空)+25秒(H开算)=50秒

所有触发器共享时钟长度必须覆盖所有组合路径传播周期+输入触发器的Tpd+输出触发器的Tsetup.

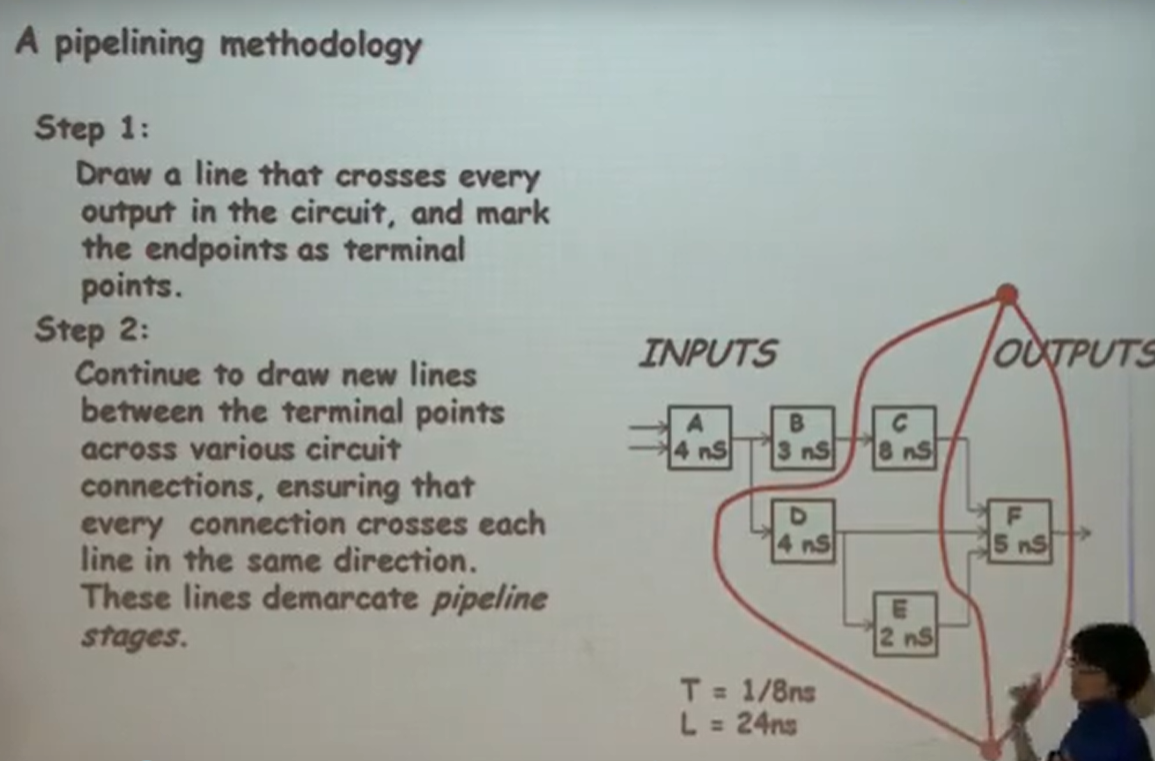

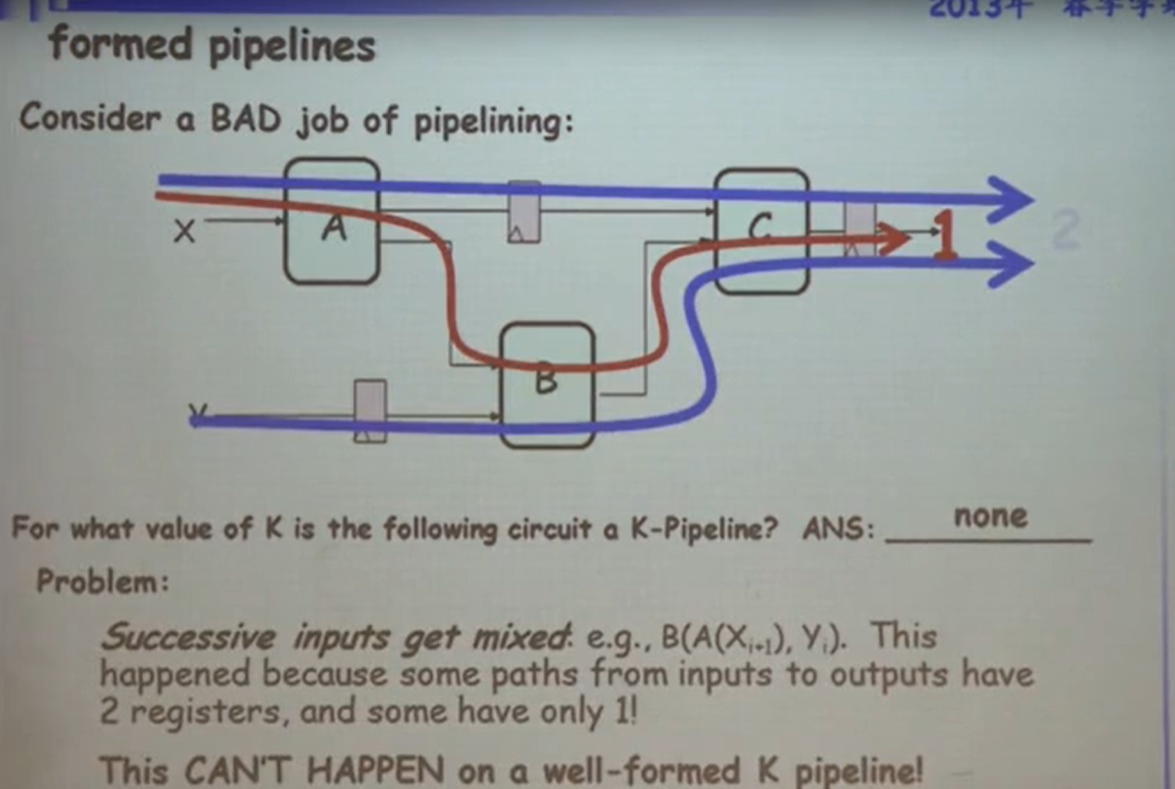

每个K级流水线,其触发器都在输出上(不在其输入上)

无论走哪条线路触发器的数量要一致。

工作频率最高跟最大的组合+触发器的建立时间(就是最大的云朵)要长有关,因为所有的触发器共用一个clk