3. Creating Timing Exceptions

创建好时钟、定义好输入输出延迟后,就可以按照这些约束对设计进行时序分析了。默认的情况下,软件按照1T 原则分析所有需要检查的timing path。在综合、布局布线时,工具也会根据时序约束,尽可能使所有timing path都满足1T的要求。但工具也不是万能的,如果设计要求过高的话,有些timing path可能不能达到设计要求,这样不满足设计要求的timing path就会以timing violation的形式给出。

在很多情况下,设计的结构和功能并不要求所有的timing path都符合1T的要求,甚至有的timing path则根本没有时序要求,比如说异步复位信号。这时候,就可以对这一类的timing path设定相对宽松的时序约束或者不做时序要求,称之为timing exceptions。

常用的设定timing exception的方式有两种:false path和Multicycle path。先来讨论false path。

False path就是不需要关注其时序的timing path。如果将一条timing path设为false path,软件在做时序分析时,会自动忽略掉这条timing path,不做分析。之前讲clock group时曾讲过,如果把两个时钟设定为不同的组,软件就不会分析这两个时钟时间的timing path。软件是如何实现的呢?实际上,当设定两个时钟为不同的组时,软件隐含的动作是把两个时钟之间所有的timing path都设定为false path,从而达到不对其进行分析的目的。

可以使用set_false_path命令将一条timing path设定为false path。下面是set_false_path的语法:

|

Syntax |

set_false_path [-h | -help] [-long_help] [-fall_from <names>] [-fall_to <names>] [-from <names>] [-hold] [-rise_from <names>] [-rise_to <names>] [-setup] [-through <names>] [-to <names>] |

在这个命令中,-from用来定义timing path的起点, -through 用来定义timing path所经过的点, -to用来定义timing path的终点,另外可以用-hold 和 –setup来定义这条命令适用的范围,是setup/hold check时使用,而默认的情况是setup和hold都适用。其他的参数以及更详细的描述可参照QuartusII的帮助系统或者SDC相关的资料。

在DAC7512控制器的设计中,因为工作频率较慢,设计也相对简单,所以在设计中没有出现有timing violation 的情况,不便于在真实的环境中对照set_false_path命令的使用情况。为此,通过提高时钟频率的方式,制造出timing violation。将DAC7512控制器的时钟CLK25M和CLK50M分别调整到75MHz和150MHz,其他相关时钟也随之改变。用TimeQuest报告出更改时钟后DAC7512控制器的时序分析结果。下面是setup check的结果:

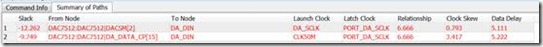

从Summary of Paths的结果可以看系统存在两条timing path存在timing violation。拿timing violation值较大的第一条timing path进行分析,下面是该timing path的详细信息:

该timing path的起点是DAC7512:DAC7512|DACSM[2],终点是DA_DIN,Launch Clock和Latch Clock分别是DA_SCLK和PORT_DA_SCLK(下降沿),Slack值为-12.262。在之前定义时钟的约束时,这两个时钟是被定义为同一组的。另外还有更详细的这条timing path的信息,比如说timing path所经过的每一个点,以及每一个cell或者net之间的延时情况等等,这里不再做详细的介绍。

set_false_path -from [get_pins {DAC7512|DACSM[2]|clk}] -to [get_ports {DA_DIN}]

加上这条约束以后,再看时序分析的结果,setup的情况如下:

现在软件报告只有一条timing path有timing violation了,少了上面被设定为false path的这条timing path。但实际上并不是说上面的这条timing path的时序变得没有问题,原来的问题依然存在,甚至会更糟糕,只是我们把它设定为false path了,软件不会再去分析它而已。这就要求对于set_false_path的使用,一定要慎重。只有肯定不用关注某条timing path的时序时,才能使用这个命令,否则软件不会对它做任何的分析,出问题的概率会比较大。在使用set_false_path的命令时,还要注意一点,timing path的起点实际上是寄存器DACSM[2]的clock端,要用[get_pins {DAC7512|DACSM[2]|clk}]来获取。

再讨论Multicycle path。

一般情况下,信号在timing path的起点(亦即第一个时钟沿)发生变化,Terminate会在timing path的终点(亦即第二个时钟沿)采集该信号。这种情况,做时序检查就需要按1T来做,这也是设计中最常见的一种情况。但如果信号在第一个时钟沿发生变化,terminate端在第三个时钟沿时采集该信号,那么就不需要保证信号在第二个时钟沿传递到终点,也就是说,不需要做1T的检查而是做2T的检查,即保证信号在第三个时钟沿之前到达终点。依次类推,可以对timing path进行nT(n > 1)的检查,这时统称该timing path为multicycle path。

将某一条timing path设定为multicycle path,无论multi实际为多少,实际上都是降低了对该条timing path的时序要求。

可以使用set_multicycle_path命令将一条timing path设为multicycle path。下面是set_multicycle_path命令的语法:

|

Syntax |

set_multicycle_path [-h | -help] [-long_help] [-end] [-fall_from <names>] [-fall_to <names>] [-from <names>] [-hold] [-rise_from <names>] [-rise_to <names>] [-setup] [-start] [-through <names>] [-to <names>] <value> |

和set_false_path一样,在命令中,-from用来定义timing path的起点, -through 用来定义timing path所经过的点, -to用来定义timing path的终点,另外可以用-hold 和 –setup来定义这条命令适用的范围,是setup/hold check时使用,而默认的情况是setup和hold都适用。另外一个重要的参数是value,它直接用来定义multi的值,如果设定value=2,则就是multicycle 2 path,如果value=3,则就是multicycle 3path。其他的参数以及更详细的描述可参照QuartusII的帮助系统或者SDC相关的资料。

假设上面所讲的timing path为multicycle 2 path的话,可以用下面的命令对该timing path进行时序约束:

set_multicycle_path -setup 2 -from [get_pins {DAC7512|DACSM[2]|clk}] -to [get_ports {DA_DIN}]

set_multicycle_path -hold 1 -from [get_pins {DAC7512|DACSM[2]|clk}] -to [get_ports {DA_DIN}]

要注意的是,如果在做setup 检查时,timing path为multicycle 2 path,那么在做hold 检查时,该timing path就为multicycle 1 path,以此类推。

另外非常重要的一点,如果该Resouce有多个Terminate,对该Resource为起点的timing path设multicycle path时,其多个Terminate和起点之间应CDC电路处理,关于这一点的详细信息,可参考CDC的相关资料。

set_false_path和set_multicycle_path这两个命令,有不同的应用场合和背景。但相同的一点是,都从系统实际的结构触发,来降低对整个系统的时序要求。使用这两个命令的时候,一定要确认设计本身是符合要求的,否则很容易出时序方面的问题。

另外还有两个命令分别是set_max_delay和set_min_delay。并不推荐大家使用,所以在这里也不做更多的介绍,有兴趣的朋友可以去查找SDC的相关资料。