2017-2018-1 20155301 《信息安全系统设计基础》第7周学习总结

教材学习内容总结

- 作为我们处理器实现的运行实例,因为受x86-64指令集的启发,它被俗称为“x86”,所以我们称我们的指令集为“Y86-64”,与“x86-64”相比,Y86-64指令集的数据类型、指令和寻址方式都要少一些。它的字节级编码也比较简单,机器代码没有相应的x86-64代码紧凑,不过设计他的CPU译码逻辑也要简单一些。

- 定义Y86指令集体系结构:包括定义各种状态元素、指令集和它们的编码、一组编程规范和异常事件处理。

- Y86-64的状态类似于x86-64。有15个程序寄存器:%rax、%rcx、%rdx、%rbx、%rsp、%rbp、%rsi、%rdi和%r8到%r14。

- 内存从概念上来说就是一个很大的字节数组,保存着程序和数据。

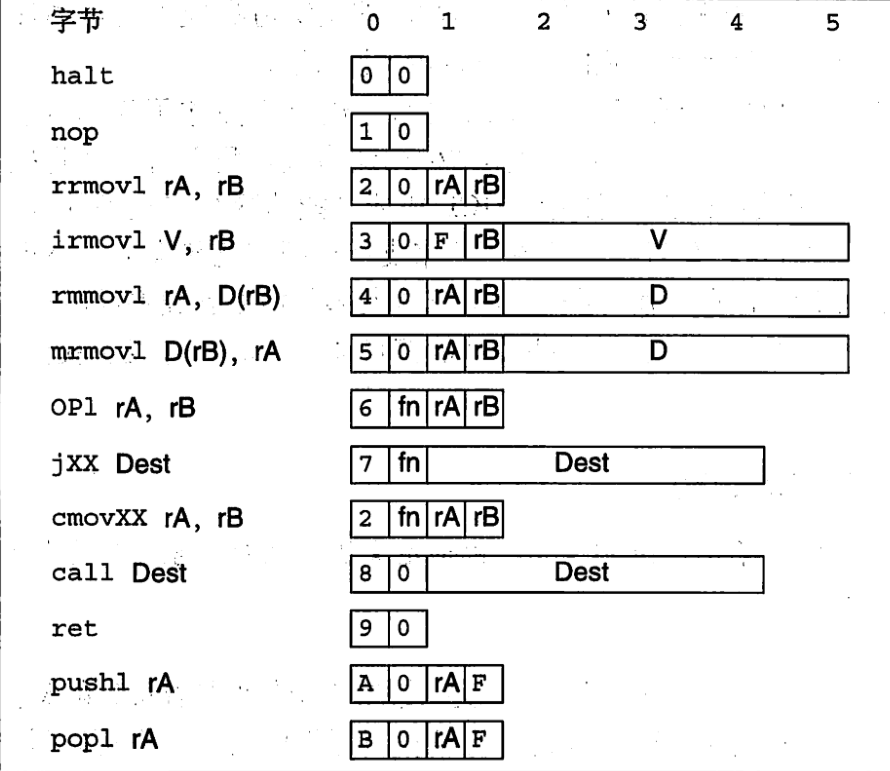

- 下图给出了Y86-64 ISA中各个指令的简单描述。Y86-64指令集基本上是x86-64指令集的一个子集。它只包括8字节整数操作,寻址方式较少,操作也较少。

- x86-64的movq指令分成了4个不同的指令:irmovq、rrmovq、mrmovq、rmmovq分别显示地指明源和目的的格式。源可以是立即数(i)、寄存器(r)或内存(m)。目的可以是寄存器(r)或内存(m)。两个内存传送指令中的内存引用方式是简单的基址和偏移量形式。

- 有4个整数操作指令,如下图中的OPq。它们是addq、subq、andq和xorq。它们只对寄存器数据进行操作,而x86-64还允许对内存数据进行这些操作,这些指令会设置3个条件码ZF、SF和OF。

- 7个跳转指令是jmp、jle、jl、je、jne、jge、jg。

- 有6个条件传送指令:cmovle、cmovl、cmove、cmovne、cmovge、cmovg。这些指令的格式与寄存器-寄存器传送指令rrmovq一样,但是只有当条件码满足所需要的约束时,才会更新目的寄存器的值。

- call指令将返回地址入栈,然后跳到目的地址。ret指令从这样的调用中返回。

- pushq和popq指令实现了入栈和出栈,就像在x86-64中一样。

- halt指令停止指令的执行。x86-64中有一个与之相当的指令hlt。x86-64的应用程序不允许使用这条指令,因为他会导致整个系统暂停运行。

- 每个指令需要1~10个不等的字节。每条指令的第一个字节表明指令的类型。这个字节分为两部分,每部分4位:高4位是代码部分,低4位是功能部分。

- 在指令编码中以及在我们的硬件设计中,当需要指明不应该访问任何寄存器时,就用ID值0xF来表示。

| 数字 | 寄存器名字 | 数字 | 寄存器名字 |

|---|---|---|---|

| 0 | %rax | 8 | %r8 |

| 1 | %rcx | 9 | %r9 |

| 2 | %rdx | A | %r10 |

| 3 | %rbx | B | %r11 |

| 4 | %rsp | C | %r12 |

| 5 | %rbp | D | %r13 |

| 6 | %rsi | E | %r14 |

| 7 | %rdi | F | 无寄存器 |

-Y86-64异常,对于Y86-64来说,程序员可见的状态包括状态码State,它描述程序执行的总体状态。当遇到这些异常的时候,我们就简单地让处理器停止执行指令

| 值 | 名字 | 含义 |

|---|---|---|

| 1 | AOK | 正常操作 |

| 2 | HLT | 遇到器执行halt指令 |

| 3 | ADR | 遇到非法地址 |

| 4 | INS | 遇到非法指令 |

-

逻辑设计和硬件控制语言HCL,在硬件设计中,用电子电路来计算对位进行运算的函数,以及在各种存储器单元中存储位,逻辑1是用1.0伏特左右的高电压表示的,而逻辑0是用0.0伏特左右的低电压表示的。

-

AND用&&表示,OR用||表示,而NOT用!表示,我们用这些符号而不用C语言中的位运算符&、|和~,这是因为逻辑们只对单个位的数进行操作。

-

将很多的逻辑们组合成一个网,就能构建计算块,称为组合电路。如何构建这些网有几个限制:

1.每个逻辑们的输入必须连接到下述选项之一:1)一个系统输入(成为主输入)

2)某个存储单元的输出

3)某个逻辑门的输出。

2.两个或多个逻辑们的输出不能连接在一起。否则它们可能会实现上的信号矛盾,可能会导致一个不合法的电压或电路故障。

3.这个网必须是无环的,也就是在网中不能有路经经过一系列的门而形成一个回路,这样的回路会导致该网络计算的函数有歧义。

-

HCL表达式很清楚地表明了组合逻辑电路和C语言中逻辑表达式的对应之处。它们都是用布尔操作来对输入进行计算的函数,但是有以下区别:

1.因为组合电路是由一系列的逻辑门组成,它的属性输出会持续地响应输入的变化,如果电路的输入变化了,在一定的延迟之后,输出也会相应地变化,而C表达式只会在程序执行过程中被遇到时才进行求值。

2.C的逻辑表达式允许参数是任意整数,0表示FLASE,其他任何值都表示TRUE,而逻辑门只对位值0和1进行操作。

3.C的逻辑表达式有个属性就是它们可能只被部分求值。如果一个AND或OR操作的结果只用对第一个参数求值就能确定,那么就不会对第二个参数求值了。 -

在处理器设计中,很多时候都需要将一个信号与许多可能匹配的信号做比较,以此来检测正在处理的某个指令代码是否属于某一类指令代码。

-

时钟寄存器存储单个位或字。时钟信号控制寄存器加载输入值。

-

随机访问存储器存储多个字,用地址来选择该读或该写哪个字。

-

通常,处理一条指令包括很多操作,将他们组织成某个特殊的阶段序列,即使指令的动作差异很大,但所有的指令都遵循统一的序列。下面是关于各个阶段以及各阶段内执行操作的简略描述:

1.取指:取指阶段从内存读取指令字节,地址为程序计数器(PC)的值。从指令中抽取出指令指示符字节的两个四位部分,称为icode和ifun。它可能去出一个寄存器值指示符字节,指明一个或两个寄存器操作数指示符rA和rB。他还可能取出一个四字节常数字valC。他按顺序方式计算当前指令的下一跳指令的地址valP。

2.译码:译码阶段从寄存器文件读入最多两个操作数,得到值valA和/或valB。通常,他读入指令rA和rB字段指明的寄存器,不过有些指令是读寄存器%rsp的。3.执行:在执行阶段,算术逻辑单元要么执行指令指明的操作,计算内存引用的有效地址,要么增加或减少栈指针。得到的值我们称为value。在此,也可能设置条件码。对一条条件传送指令来说,这个阶段会检验条件码和传送条件,如果条件成立,则更新目标寄存器。

4.访存:访存阶段可以将数据写入内存,或者从内存中读出数据。读出的值为valM。

5.写回:写回阶段最多可以写两个结果到寄存器文件。

6.更新PC:将PC设置成下一条指令的地址。

-

SEQ阶段的实现

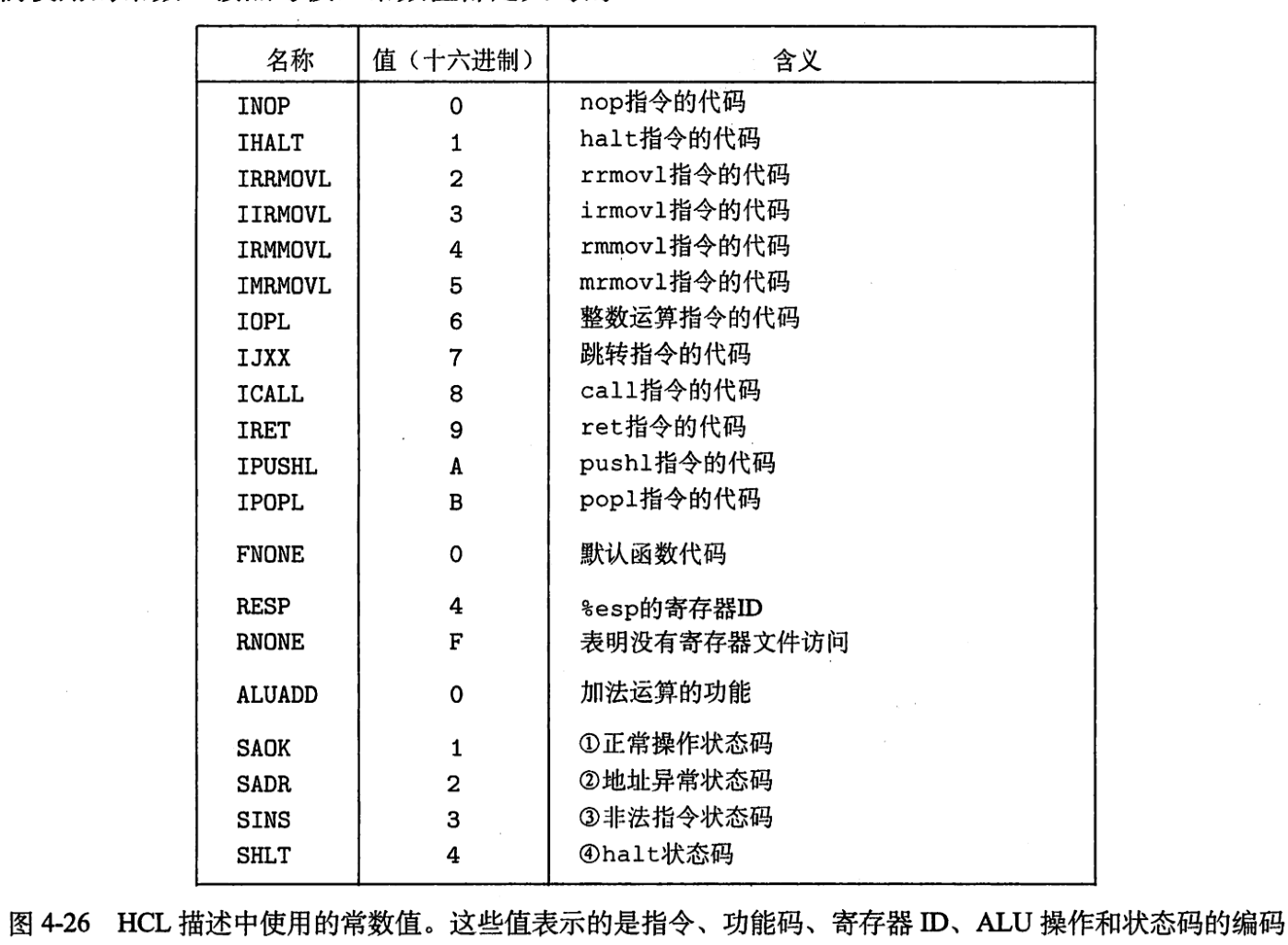

在控制逻辑中必须被显式引用的常数:(常数值都是大写的)

nop指令只是简单的经过各个阶段,除了将PC加1,不进行任何处理。halt指令是处理器状态被设置为HLT,导致处理器停止运行。

实验楼环境

教材学习中的问题和解决过程

代码调试中的问题和解决过程

代码托管

上周考试错题总结

- 错题1及原因,理解情况

- 错题2及原因,理解情况

- ...

结对及互评

点评模板:

- 博客中值得学习的或问题:

- xxx

- xxx

- ...

- 代码中值得学习的或问题:

- xxx

- xxx

- ...

- 其他

本周结对学习情况

[20155317](http://www.cnblogs.com/wxwddp/p/7671075.html)

- 结对学习内容

- XXXX

- XXXX

- ...

其他(感悟、思考等,可选)

xxx

xxx

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 5000行 | 30篇 | 400小时 | |

| 第一周 | 200/200 | 2/2 | 20/20 | |

| 第二周 | 300/500 | 2/4 | 18/38 | |

| 第三周 | 500/1000 | 3/7 | 22/60 | |

| 第四周 | 300/1300 | 2/9 | 30/90 |

尝试一下记录「计划学习时间」和「实际学习时间」,到期末看看能不能改进自己的计划能力。这个工作学习中很重要,也很有用。

耗时估计的公式

:Y=X+X/N ,Y=X-X/N,训练次数多了,X、Y就接近了。

-

计划学习时间:XX小时

-

实际学习时间:XX小时

-

改进情况:

(有空多看看现代软件工程 课件

软件工程师能力自我评价表)