最近在学SDRAM,听说SDRAM涉及到静态时序分析,那还说什么呢学吧。

在看到create_clock与create_generated_clock时我彻底疑惑了, 即然有了create_clock何必还要create_generated_clock呢,google一翻后得到一个结论,create_generated_clock是用于衍生时钟,TimeQuest作STA分析时会自动计算source clock 到generated_clock之间的skew.我又不明白了即然TimeQuest可以计算时钟偏斜,那直接对source clock进行create_clock不就行了,TimeQuest不就会自动对其衍生时钟偏斜进行分析了么。可能这个问题太低级了,大牛觉得太显然对此一略而过,也可能是我理解能力太差,大牛写了我没领会到,不管怎么样我是百思不得其解,早晨醒来就有了一个猜想。TimeQuest号称STA工具,那么他应该不会理解衍生时钟的逻辑功能,只能单纯的根据uTco、clock skew、data path等时间值对setup time、hold time、removal time、recoveral time的余量进行分析。也就是说TimeQuest只会对内部逻辑延时进行计算不进行逻辑分析,实际上TimeQuest并不知道你的衍生时钟与源时钟之间的关系。因此需要create_generated_clock对衍生时钟进行说明,下面用图来说明一下。

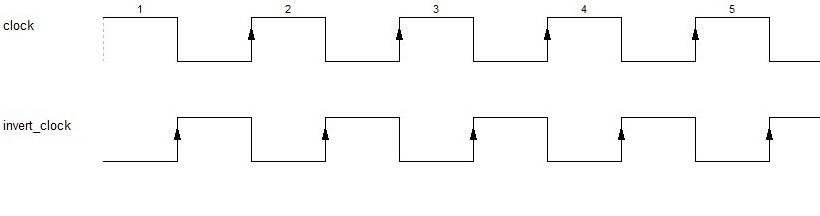

假设使用逻辑衍生出的理想时序如下图:

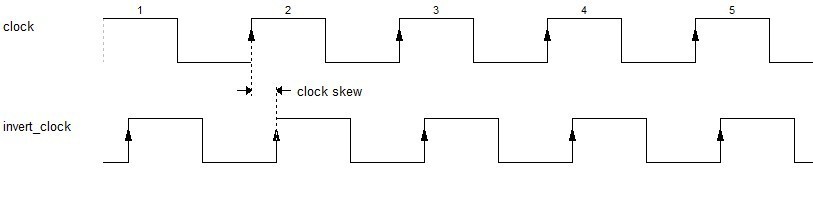

图中clock为源时钟,invert_clock为衍生时钟,与源时钟相移180度,如果仅使用create_clock来对clock时行约束,那么,TimeQuest在进行STA时对invert_clock的时钟所理解的波形应该如下图:

在上图中,clock skew仅仅是由时钟衍生逻辑产生的延时,不包括逻辑产生的相移,也就是说TimeQuest无法理解clock进行一块逻辑后出来的具体时钟与源时钟的真正关系,仅能靠一些路径延迟与DFF或LUT的参数来计算时钟延时。

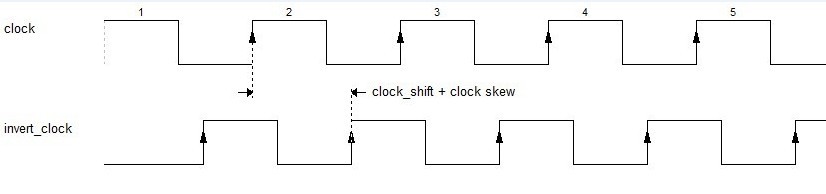

而如果我们使用create_generated_clock对invert_clock进行约束后,TimeQuest在进行STA时对invert_clock的时钟所理解应该如下图:

也就是说只有对衍生时钟进行create_generated_clock约束,TimeQuest才能正确的理解波形,换句话说,一些走线延时、LUT、DFF的参数产生的问题由TimeQuest来自动搞定,如果是由于我们自己用逻辑产生的影响(如上图相位偏移),我们必须报告给TimeQuest,TimeQuest才正在静态时序分析时进行正确的计算。由于上面的TimeQuest所有过程均为我猜测得出,所以有不对的地方,请大家拍砖。