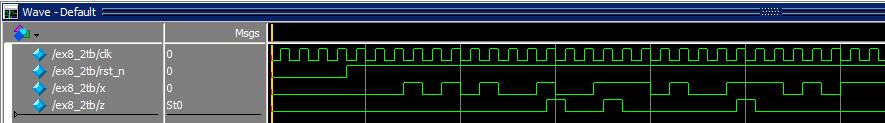

2. 设计一个“1001”串行数据检测器,其输入、输出如下:

输入x:000 101 010 010 011 101 001 110 101

输出z:000 000 000 010 010 000 001 000 000

(1)设计思路:同前,规划状态,无它。

(2)1001序列检测电路源码:

1 //detect 1001 2 //2020-10-13 3 // by YongFengXie 4 module ex8_2(clk,rst_n,x,z); 5 input clk; 6 input rst_n; 7 input x; 8 output reg z; 9 10 reg [4:0] state; 11 12 parameter s0=5'b00001, 13 s1=5'b00010, 14 s2=5'b00100, 15 s3=5'b01000, 16 s4=5'b10000; 17 18 always @(posedge clk or negedge rst_n) 19 begin 20 if(!rst_n) 21 begin 22 state<=s0; 23 z<=1'b0; 24 end 25 else 26 case(state) 27 s0:begin 28 if(x==1'b0) //0 29 begin 30 state<=s0; 31 z<=1'b0; 32 end 33 else //1 34 begin 35 state<=s1; 36 z<=1'b0; 37 end 38 end 39 s1:begin 40 if(x==1'b0) //10 41 begin 42 state<=s2; 43 z<=1'b0; 44 end 45 else //11 46 begin 47 state<=s1; 48 z<=1'b0; 49 end 50 end 51 s2:begin 52 if(x==1'b0) //100 53 begin 54 state<=s3; 55 z<=1'b0; 56 end 57 else //101 58 begin 59 state<=s1; 60 z<=1'b0; 61 end 62 end 63 s3:begin 64 if(x==1'b0) //1000 65 begin 66 state<=s0; 67 z<=1'b0; 68 end 69 else //1001 70 begin 71 state<=s4; 72 z<=1'b1; 73 end 74 end 75 s4:begin 76 if(x==1'b0) //10010 77 begin 78 state<=s2; 79 z<=1'b0; 80 end 81 else //10011 82 begin 83 state<=s1; 84 z<=1'b0; 85 end 86 end 87 default:begin 88 state<=s0; 89 z<=1'b0; 90 end 91 endcase 92 end 93 94 endmodule

(3) 1001序列检测电路测试代码:

1 //ex8_2 testbench 2 //2020-10-13 3 // by YongFengXie 4 `timescale 1ns/1ns 5 module ex8_2tb; 6 reg clk; 7 reg rst_n; 8 reg x; 9 wire z; 10 11 ex8_2 ut(clk,rst_n,x,z); 12 13 initial begin 14 clk=1'b0; 15 rst_n=1'b0; 16 x=1'b0; 17 #40 rst_n=1'b1; 18 #10 x=1'b0; 19 #10 x=1'b0; //000 20 #10 x=1'b1; 21 #10 x=1'b0; 22 #10 x=1'b1; //000 23 #10 x=1'b0; 24 #10 x=1'b1; 25 #10 x=1'b0; //010 26 #10 x=1'b0; 27 #10 x=1'b1; 28 #10 x=1'b0; //010 29 #10 x=1'b0; 30 #10 x=1'b1; 31 #10 x=1'b1; //011 32 #10 x=1'b1; 33 #10 x=1'b0; 34 #10 x=1'b1; //101 35 #10 x=1'b0; 36 #10 x=1'b0; 37 #10 x=1'b1; //001 38 #10 x=1'b1; 39 #10 x=1'b1; 40 #10 x=1'b0; //110 41 #10 x=1'b1; 42 #10 x=1'b0; 43 #10 x=1'b1; //101 44 #300 $stop; 45 end 46 47 always #5 clk=~clk; 48 49 endmodule

(4) 1001序列检测电路的仿真结果如图ex8_2_1所示:

图ex8_2_1 1001序列检测电路仿真结果

(5) 1001序列检测电路的状态转换如图ex8_2_2所示:

图ex8_2_2 1001序列检测电路状态转换图

(6)总结:跟习题8.1相比,无它,唯手熟尔。