Chapter 2. Hierarchical Modeling Concepts

2.8 Exercises

1. An interconnect switch (IS) contains the following components, a shared memory (MEM), a system controller (SC) and a data crossbar (Xbar).

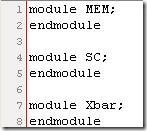

a) Define the modules MEM, SC, and Xbar, using the module/endmodule keywords. You do not need to define the internals. Assume that the modules have no terminal lists.

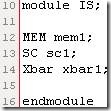

b) Define the module IS, using the module/endmodule keywords. Instantiate the modules MEM, SC, Xbar and call the instance mem1, sc1, and xbar1, respectively. You do not need to define the internals. Assume that the module IS has no terminals.

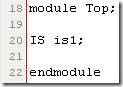

c) Define a stimulus block (Top), using the module/endmodule keywords. Instantiate the design block IS and call the instance is1. This is the final step in building the simulation environment.

my answer:

a)

b)

c)

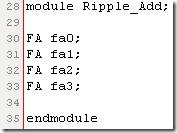

2. A 4-bit ripple carry adder (Ripple_Add) contains four 1-bit full adders (FA).

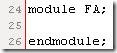

a) Define the module FA. Do not define the internals or the terminal list.

b) Define the module Ripple_Add. Do not define the internals or the terminal list. Instantiate four full adders of the type FA in the module Ripple_Add and call them fa0, fa1, fa2, fa3.

my answer:

a)

b)

Reference

Smair Palnitkar, <Verilog HDL: A Guide to Digital Design and Synthesis (2nd) >