1、 FP2网络处理器的背景知识

在http://www.newelectronics.co.uk/article/22079/Pushing-packet-performance.aspx

公布了下述关系P2的技术细节:

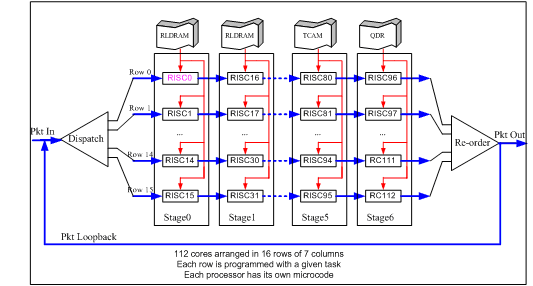

The p-chip’s role is to inspect packets and perform the look ups that determine where the packets should be forwarded. This network processor comprises 112 cores arranged in 16 rows of 7 columns – with the cores clocked at 840MHz. This contrasts to the 0.15µm process first generation 10Gbit/s FP1, whose 30 cores are clocked at 190MHz.

Each processor is programmable and has its own microcode. Each row is programmed with a given task before being fed data packets, while packets from the same flow are sent in order. Thus, one row could be implementing multiprotocol label switching (MPLS) protocol tasks used to direct tagged packets between nodes, while another row could be performing IP routing.

On the ingress path, two p-chips are used in series, along with the q-chip traffic manager. Though a single p-chip can process 100Gbit/s line rates, a second p-chip is included to provide additional processing for the broad range of current and future edge router processing tasks.

上文大意是:

1)FP2的NP有112个cores, 排布成16行7列。

2)每一行完成一种业务转发。如第一行做MPLS转发,第二行做IP转发。

而每一行又有7个Core,这说明它是典型的Pipeline架构,由7个Core接力完成一种转发业务(如MPLS转发);

3)共有16个rows,说明有16条独立的流水线。每条流水线都可处理任何业务,具体是根据输入的包来决定。Each row is programmed with a given task before being fed data packets;

4)每一行的包能保证输入输出保序,说明它是严格的流水线,一个包只会沿着一条流水线走,中间不会切换到其它行;

5)再考虑到整个芯片要在16行之间保证顺序(例子,处理single flow IP转发),故需要一个输入分发模块和输出排序模块;

6)每个Core可以有自己的微码空间;

7)在Ingress方向,为了增强处理能力,将两个P串起来用。为什么要串起来?主要是增加查表次数;

根据对NP背景知识,上述信息已经很清楚描述了FP2网络处理器的架构:Pipeline stage,16条流水线,每条流水线上7个core。

2、 Xelerated网络处理器的背景知识

Xelerated的X11是最典型的Pipeline stage的NP,它的设计思路与转发ASIC最接近:一条流水线,划分成若干个Stages,各Stages接力完成转发工作 。

如小强同学所述,Xelerated的X11和HT320是很不错的网络处理器,转发性能有保障。下述链接算是基础知识,有需要的DX请先看看。

下面链接介绍,HX320有512个RISC core,是业界最多的芯片,无与伦比。第二多的是思科的SPP,有188个RISC Core。

http://www.slideshare.net/EJarstrand/service-density-by-xelerated-at-linley-seminar

下面链接是“A 40Gb/s Network Processor with PISC™”,介绍了X11的基本设计思想。

http://portal.acm.org/citation.cfm?id=1032450

http://spg.ict.ac.cn/paper/cassetDownload.action?cassetId=81043

3、 NP的两种类型:RTC和Pipeline

如果你想开汽车制造厂,有两种方式:手工作坊式和流水线式。

手工作坊式:招一个“四项全能”的工人,给他几张铁皮和全套工具,包括锤子、焊枪和几把刷子。然后由该工人完成汽车的所有工序。

只有一个工人,生产速率太慢,如何改进?答案是招几百个工人,每人分别发一套工具。生产速率也就提高了几百倍。

流水线式:伟大的福特发明了流水线造汽车。一条汽车生产线上有几百名工人,每人只发一件工具(不是一套),每个工人只做其中一件事,如张三上左轮胎,李四上右车门;所有人接力配合,也就造成出一辆完整的汽车。

流水线的发明,使平均每人的生产效率大大提高,也使工具的消耗量大大减小。既然流水线生产效率要高,为什么手工作坊造汽车还有存在的价值?因为这种汽车叫纯手工打造,全定制,每一辆汽车都是不同的精品,可作为经典收藏品。

了解上述造汽车的原理,再来理解NP的两种架构就很容了。一个标准L2/L3转发,可以分成下述动作:包头分析,IPv4查表、IPv6查表、MPLS查表、ACL查表、QoS分类、TTL减一、Checksum重计算、L2包头生成、流量统计等动作。

用许多RSIC Core来做包转发时,可以让一个Core完成上述所有功能,也可以让一个Core只完成上述一种功能甚至一种功能的小部分。根据Core的分工和组织方式,NP形成了两种典型的架构:RTC模型和Pipeline stage模型。

1)RTC(Run to Complement)

类似手工作坊式汽车生产厂。一个Core相当于一个工人,完成所有转发功能。所有Core并行工作,性能得以倍增。一个Packet只交给一个Core处理,不会转交给其它Core。一个Core有全套微码,但Core之间不需要交互。

该架构一句话评价:将方便留给软件人员,将困难留给了芯片设计人员。

优点:其编程模型对软件人员是最好的。因为是一个Core完成所有转发工作,故不用考虑多Core/多Thread之间的交付,微码编程与单Core无本质区别。微码可以任意跳转,甚至可以做复杂的函数调用(需要Stack支持)。

缺点:对芯片设计人员,不是好消息。 首先,每个Core需要放转置所有的微码(类似每个工人都要放全套工具),故需要的片内RAM较大,或者需要采用复杂的L1/L2 Icache;其次,每个Core都要去访问全部的外设(Co-processor),这样Core与外设之间需要一个巨大的Crossbar,该Crossbar在Top level布线很困难,长连线在整个芯片顶层乱跑。该Crossbar会成为架构扩展的瓶颈,甚至引起架构重写。

历史上采用该架构的NP举例如下:

Internet Machine(year 2003, closed): 64个Cores(ARC),单线程per core;

Silicon Access(year 2003, closed): 32个RISC Cores,8线程per Core;

Cisco SPP: 188个RISC Cores, 单线程 per Core;

Cisco QFP: 40个Cores,4线程per Core

2)Pipeline stage

类似流水线汽车生产厂。将许多Core分成N组,组之间以流水线方式相连。流水线上每个Core只完成一小部分工作,多个core接力配合,完成所有功能。例如第一个Core作包头分析,第二Core作MPLS查表,第三个Core作ACL查表。这样,每个core只做一小件事,只需要一小段微码。所有Core的微码串起来,就是一全套微码。

该架构一句话评价:将方面留给了芯片人员,将困难留给了软件编程人员。

优点:首先,每个Core只有一小段微码(类似每个工人只发一个工具,而不是全套工具),故微码占用的片内RAM很小;其次,每个Pipeline stage只查一种表,故Core与外设之间不需要复杂的Crossbar;再其次,架构可扩展性比较好,只需要增加流水线级数,以及每级流水线中的Core数目,处理性能就可以倍增;最后,正如流水线汽车生产厂可以大大提高单位生产率一样,相同面积的硅片上可以放下更多的Core,从而提供更高的处理性能。

缺点:软件编程复杂。首先,编程人员要将微码拆分成一小段一小段,每段正好放在一个Stage;Stage之间,需要传送参数;需要保证每个Stage的负荷相当,否则就会造成流水线上有人忙死有人闲死。但IP转发业务千变万化,需要做到合理拆分其实不容易,特别是4层以上的业务如网络安全。所以,Pipeline的Core处理能力使用效率是要打折扣的。其次,一个Stage只能做一次查一次外部表,错过了本Stage,就只能等到下一个Stage查表了,而IP转发业务查表次数特别多(例如VPLS终结进入L3 VPN),所以常见解决办法是将多个NP串接起来用。有人提到将3个NP3串接在一起完成转发功能。总之,此类NP适合四层以下的高性能转发。

历史的Pipeline stage网络处理器如下:

X11: 160个PISC Cores,分成5个stages,每个Stage有32个Cores;

Ezchip NP3/NP4: 分成4个Pipeline Stages, 每个Stage有N个Cores;

HX320: 512个PISC Cores,分成32个stages,每个Stage有16个Cores

需要指出,NP3/NP4虽然也是Pipeline stage,但其发性能并不高,这是因为其放的Core数目不够多。HT320有512个Core,而NP4有多少个Core?二者的运行频率相当。以前发表过的对NP4的评价,不妨再引用一下:

评价一个GPU的性能,主要看两个参数:内核和显存。同理,评价一个100G NP的性能,也是看类似的参数:Core, 以及Lookup Memory Bandwidth。根据这两点,不要指望NP4的性能。NP4集成了一个50G的TM, 用去了大量的Memory interface和Die size,留给NPU用的资源和DRAM就大大减小了。而Trio/FP2/SPP等高端芯片都是将TM和NP分离成2个芯片,可以充分保证NPU有足够的Die面放下众多高性能Core,以及众多Memory interface,从而保证处理性能。从过去业界对NP2/NP3的应用历史也可以看出:MX960用NP3给I-chip当配角用;C7600用NP3C给ES40单板的转发ASIC当配角用。

4、Table Lookup的延时如何处理

每个NP都配置了众多的外设,如做IP lookup的DDR2/RLDRAM,做CAR和统计的QDR SRAM。当一个Core开始访问外设到外设将结果返回到Core,可能需要50个Core时钟周期。在这50个时钟周期中,Core的ALU无事可做,Core处理能力白白浪费掉了,非常可惜。

解决上述问题,根据NP架构不同,有两个方法:

1) RTC模型:使用Multi threads

这里的Thread是指Hardware thread,不是指OS的Thread。一个Thread发出查表请求时,进入“go to sleep”,而当查表结果返回时,该Thread自动进入“awakened”。当一个Core有多个Threads时,当正在运行的Thread进入Sleep时,Core可以另外挑一个Thread来运行。

一个Core的thread多少合适?这取决了外设查表时间,以及外设查表频度和延时,以及Core的主频。一般而言,Core的主频越高,需要的Thread就越多;外设查表频度越高及时延越大,则需要的Thread数目越多。

采用Multi thread的NP:

Silicon Access iPP (year 2003, closed): 8 threads per core, 32 cores

Cisco QFP: 4 threads per core, 40 cores

RMI XLR732: 4 threads per core, 8 cores

Juniper Trio: 20 thread per core, 16 cores

2) Pipeline stage模型

做过转发ASIC的DX知道,在Stage之间的常做法是加FIFO,用吸收流水线之间速率差。Pipeline stage的NP,基本思想上就是从转发ASIC发展而来,只是将其中的Stage换成可编程的RISC。当然,也有人将其中的Stage变成可编程ASIC,如Juniper的Internet processor,这是题外话。所以,Pipeline stage的NP处理Lookup外设时延时,简单处理办法就是:在一条流水线上的两个Core之间增加一个FIFO SRAM,当上一个core发出查找外设请求时,同时将packet送入到FIFO SRAM中,自己就释放出来处理后续包;当外设查表结果返回后,packet从FIFO SRAM中输出,连同查表结果一起送给下一个Core。这种做法,与Multi thread有异曲同工之妙。位于Core中的包永远是“awakened”,让core的ALU充分转起来,除非微码编程人员的程序分段不均匀让某些Core太闲(这不是芯片人员的错,呵呵);处于Sleep态的Packet包永远位于FIFO RAM中,不占用Core的任何资源。显然,这种做法的代价要比Multi thread小。这又是为什么Pipeline stage的Core数目可以做得比RTC模型要多的原因之一。

在一条流水线上,一个Pipeline stage通常只设置一个FIFO SRAM, 一个Stage就只能查一次外设。X11 NP共有5个Stage,共可查5次外设。一个复杂的IP转发业务要查10至20次外部表项,远远超过5次,点解? 答案:内部流量绕一圈,5次变10次;将两个X11串接起来用,10次变成20次。实际上,Alcatel FP2也是同样做法。

5、 FP2网络处理器架构猜测

根据Pushing-packet-performance提到的信息,猜想结构如下:

一个P2共有7个Stage,每个Stage有16个Core。每个Stage外接一片RLDRAM或QDR供16个Core共享。

包转发流程:

1) Dispatch将输入packet分发到某条流水线上(即16个Row选一);

2) Row中的7个RISC接力处理一种业务(如MPLS转发,如IP转发),每个Core只需要放一小段微码,而不是全部;

3) 每个Stage可支持一次外部查表;外部查表时,包离开上一级Core,进入下一次Core前面的FIFO;

4) 最后一个Stage处理完后,因为同一个Row的包是保证顺序的,但Row之间不保序。故需要一个Reorder模块来重排序;

5) 重排序的包有两种情形:如果处理完成,就输出;否则,就loopback到输入端等待再次处理;

,根据http://www.valleytalk.org/wp-content/uploads/2010/02/alu7750.pdf上的100GE单板图,Ingress放了2个P2串接,Egress放了1个P2,共有3个P2芯片。

每个P2有7个Stage,每个Stage支持查一次外部表,总共可以查7次外部表。参照X11的设计思想,P2应该是支持转圈,这样多转一圈就可以查14次。单板Ingress方向再放2个P2串接,就可以查28次外部表。28次查表与Xelerated的HX320之32次相当,一般情况下够用了。要是28次查表也不够用怎么办?答案:继续转圈,性能下降。

同时,FP1的30个Core,可以猜想组织为30 cores arranged in 6 rows of 5 columns。内部支持多转一圈,即有10次查表,上行方向再用2-3个P串接,则有20-30次查表。

可以,这种Pipeline架构的最大应用限制倒不是RISC core处理能力,而是查表次数。为了获得合适的查表次数,单板上需要串接P芯片。

申明:本文信息是基于公开材料Pushing-packet-performance的文字描述来推测,只能算个大概,不能当真。如果公开材料描述不准确(marketing语言),则推测也就不准确。

PS:

下面是Xelerated的NP架构示图。每16个Core组成一个stage;在两两Stage之间有一个EAP,EAP中有块FIFO RAM存放查找外部Table的Packet;当Packet的查表请求返回后,该Packet送到下一级Stage继续处理。

引自http://www.xelerated.com/en/dataflow-architecture/

The dataflow architecture includes the following components:

- Packet Instruction Set Computer (PISC) is a processor core specifically designed for packet processing. A pipeline can include several hundreds (400+) of PISCs.

- Engine Access Point (EAP) is a specialized I/O unit for classification tasks. EAPs unify access to tables stored in embedded or external memory (TCAM, SRAM, DRAM) and include resource engines for metering, counting, hashing, formatting, traffic management and table search.

- Execution context is packet specific data available to the programmer. The execution context includes the first 256 bytes of the packet, general purpose registers, device registers and condition flags. An execution context is uniquely associated with every packet and follows the packet through the pipeline.