① secureip库:硬核(HARD IP)仿真(功能仿真和时序仿真)模型(hard IP simulation model),比如PowerPC、PCIE、SRIO、DDR等。Simulation models for the Hard-IP such as the PowerPC processor, MGT, and PCIe leverage this technology

②unisim(unisim_ver)库:xilinx 原语的功能仿真模型

③unimacro(unimacro_ver)库:xilinx宏命令功能仿真模型

④xilinxcorelib(xilinxcorelib_ver)库:xilinx cores 功能仿真模型

⑤simprims(simprims_ver)库:xilinx原语的时序仿真模型

⑥unifast库:vivado加速仿真的库(The UNIFAST library is an optional library that can be used during RTL behavioral simulation to speed up simulation runtime.

Xilinx recommends using the UNIFAST library for initial verification of the design and when running a complete verification use the UNISIM library.)

- UNISIM library for functional simulation of Xilinx primitives

- UniMacro library for functional simulation of Xilinx macros

- XilinxCoreLib library for functional simulation of Xilinx cores

- Xilinx EDK library for behavioral simulation of Xilinx Embedded Development Kit (EDK) IP components

- SIMPRIM library for timing simulation of Xilinx primitives

- SmartModel/SecureIP simulation library for both functional and timing simulation of Xilinx Hard-IP, such as PPC, PCIe®, GT, and TEMAC IP.

http://www.xilinx.com/support/documentation/sw_manuals/xilinx11/ise_c_simulation_libraries.htm

How do I speed up simulation?

Description

Solution

The UNIFAST library is an optional library that can be used during RTL behavioral simulation to speed up simulation runtime.

Xilinx recommends using the UNIFAST library for initial verification of the design and when running a complete verification use the UNISIM library.

The simulation runtime speed-up is achieved by supporting a subset of the primitive features in the simulation mode.

The libraries listed below have an equivalent UNIFAST model:

- MMCME2

- RAMB18E1/RAMB36E1

- FIFO18E1/FIFO36E1

- DSP48E1

- GTHE2_CHANNEL/GTHE2_COMMON

- GTXE2_CHANNEL/GTXE2_COMMON

The UNIFAST model is provided in both VHDL & Verilog versions and is located in the following directories:

Verilog: <Vivado_Install_Dir>/data/verilog/src/unifast

VHDL: <Vivado_Install_Dir>/data/vhdl/src/unifast

Recommended method for simulation with all UNIFAST models:

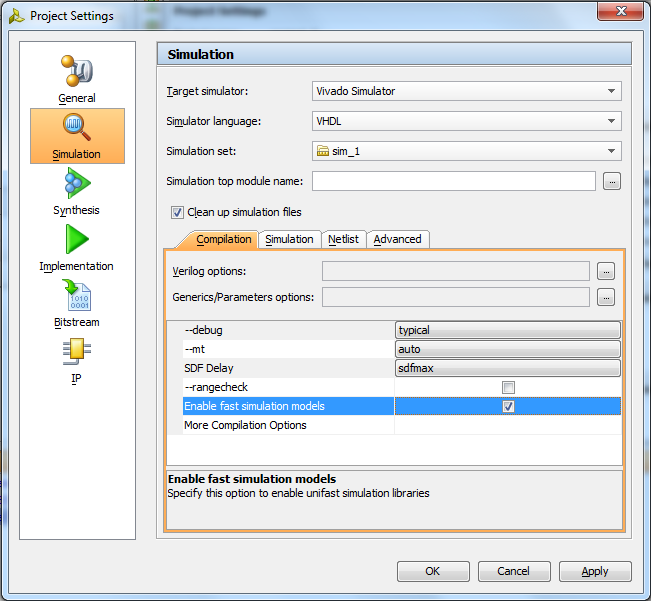

To enable UNIFAST support in a Vivado project environment for the Vivado simulator or ModelSim, check the Enable fast simulation models box, as shown below:

unifast.PNG

For IES and VCS simulators, point to the UNIFAST library using:

-y ../verilog/src/unifast

IMPORTANT NOTE:

- This model cannot be used for timing-driven simulations.

- UNIFAST libraries cannot be used for sign-off simulations because the library components do not have all of the checks/features that are available in a full model.