在一个项目完成设计、仿真后,我们就需要在FPGA平台上进行原型验证。但是原型验证往往不是一帆风顺的,总会遇到一些issue。

Xilinx的FPGA editor工具给我们调试、分析、解决这些issue提供了很好的 帮助。

今天就总结一下关于利用FPGA editor工具增加内部线延迟的方法。

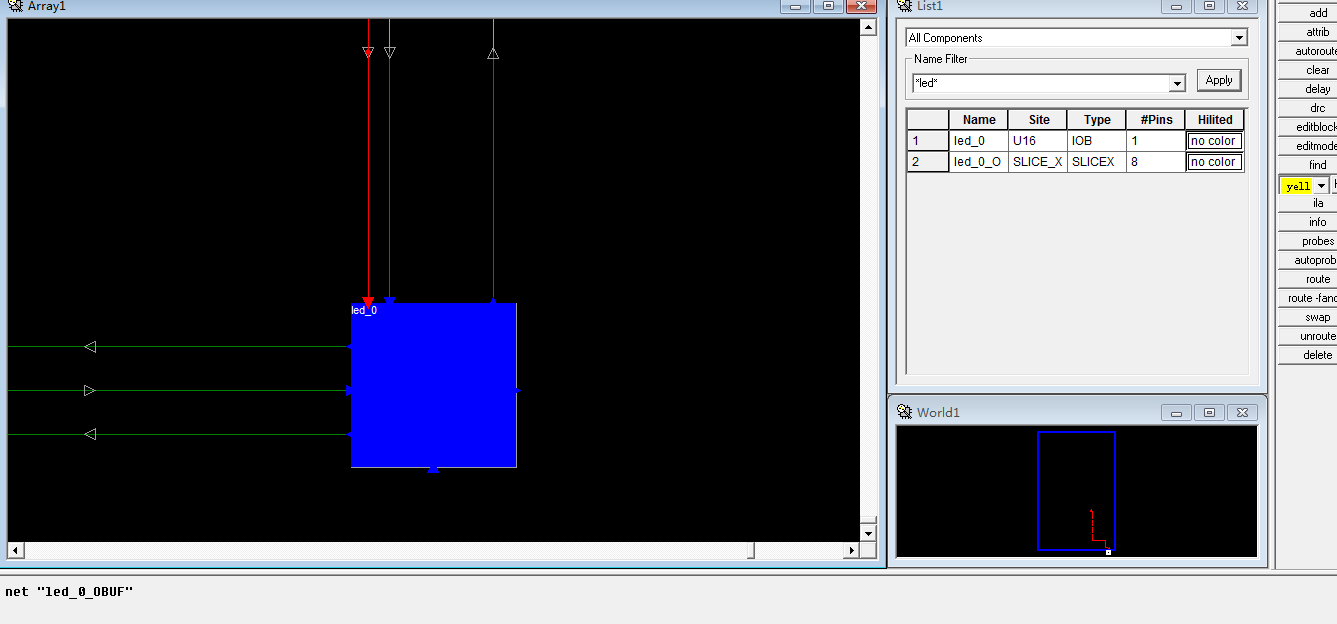

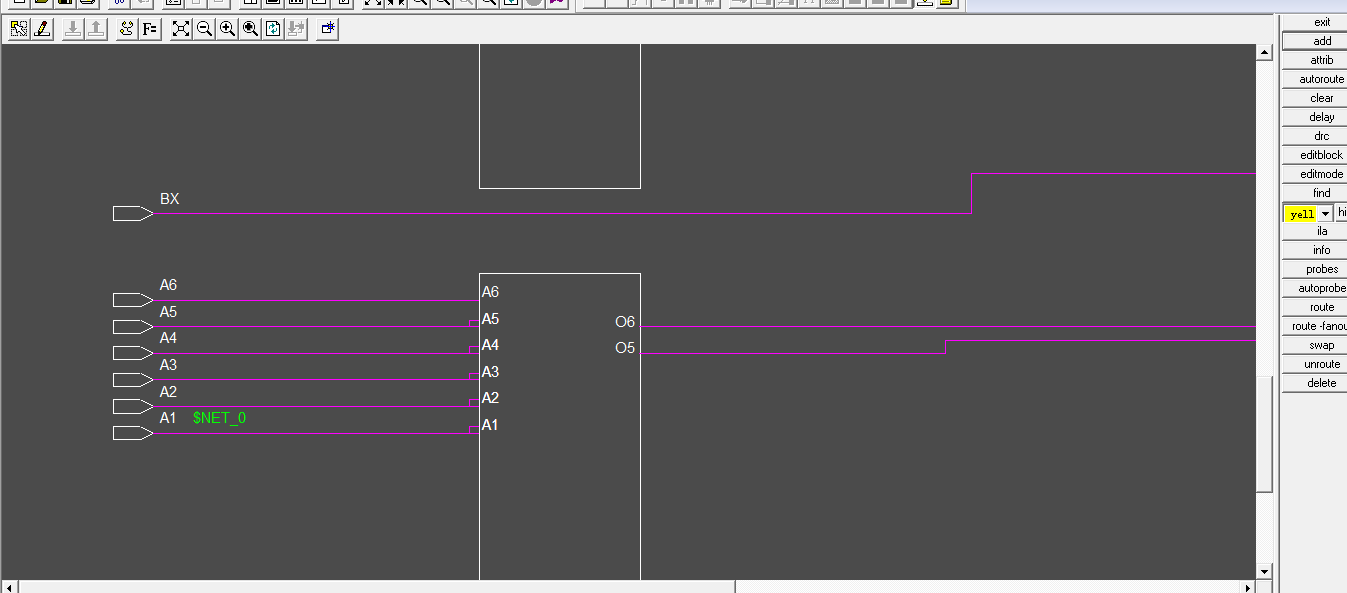

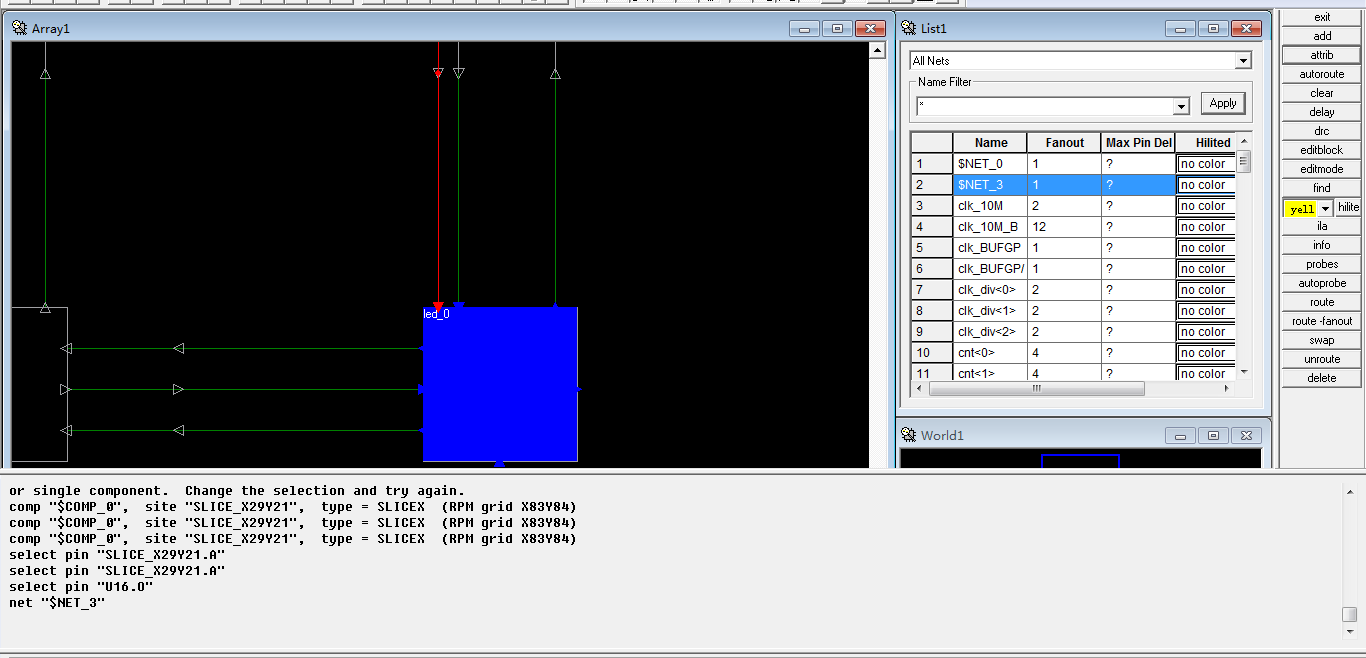

例如想把 送到 PAD上的 一个信号 “led_0” ,延迟几个ns 后 再 送到 PAD上。先在 lis里 找到这个 PAD,定位到 array 里面,单击 “led_0” 这条线,会以红色 标亮。

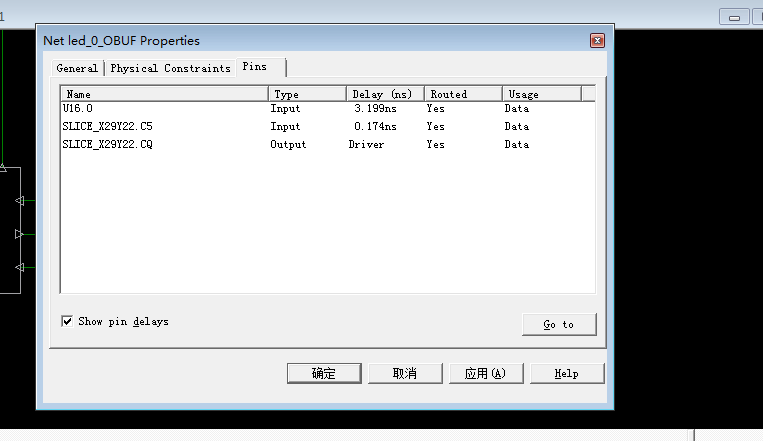

点击最右侧的 attrib ,选择 pins 选项,这里列出了 这个net的 source 和 destination 端 ,以及延迟信息。选择output(source 端),单击goto,就会找到 这个 net的

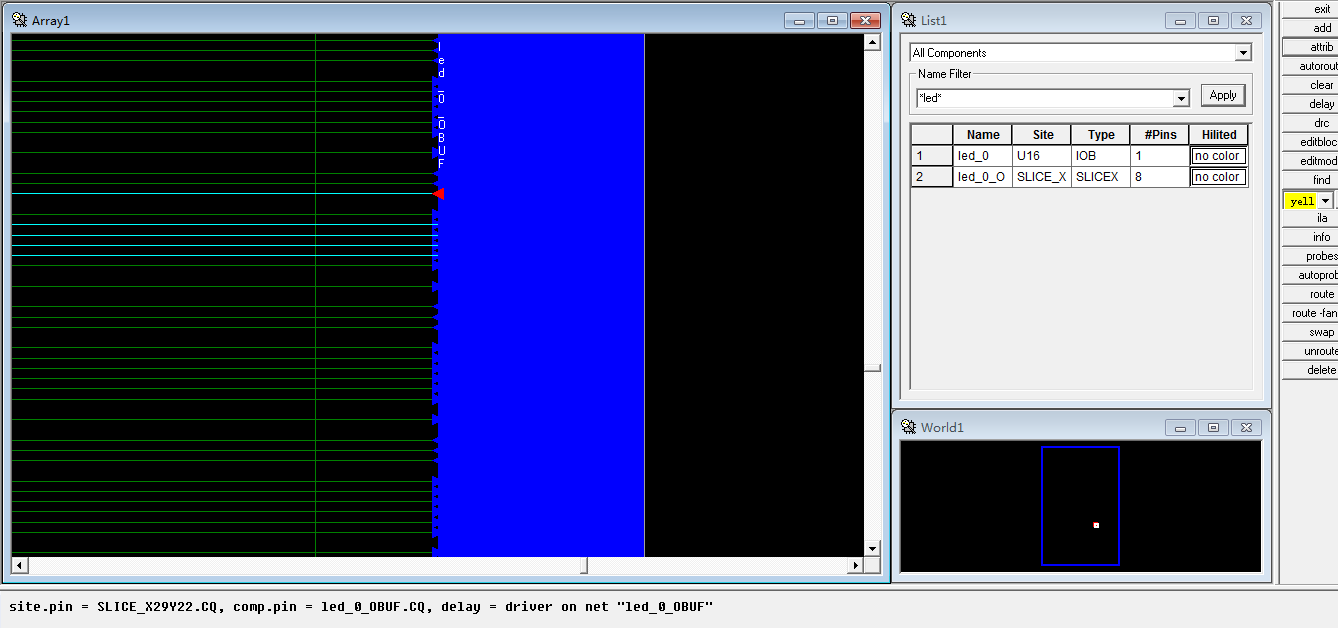

source (driver)端,如下图所示:

可以看到 这个 net 是由 SLICE_X29Y22 的 CQ Pin 驱动的。要增加延迟,可以 在 SLICE_X29Y22 的 CQ Pin 与 PAD(PAD U16的O Pin) 之间 加一个 buffer。

这里可以 增加一个 LUT 来 增加延时。

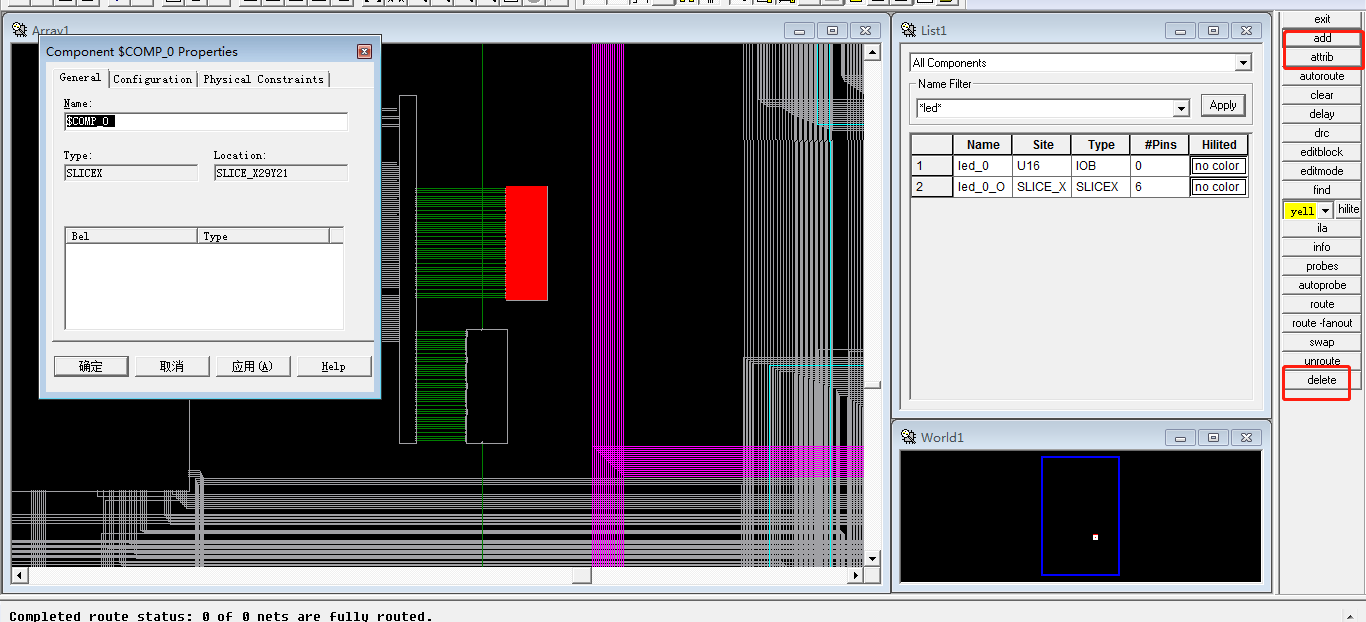

首先 单击选中这个net,在最右侧 点击delete,删除这个net。在array 里面 选取 一个 空闲的 SLICE,单击最右侧add 增加一个component。

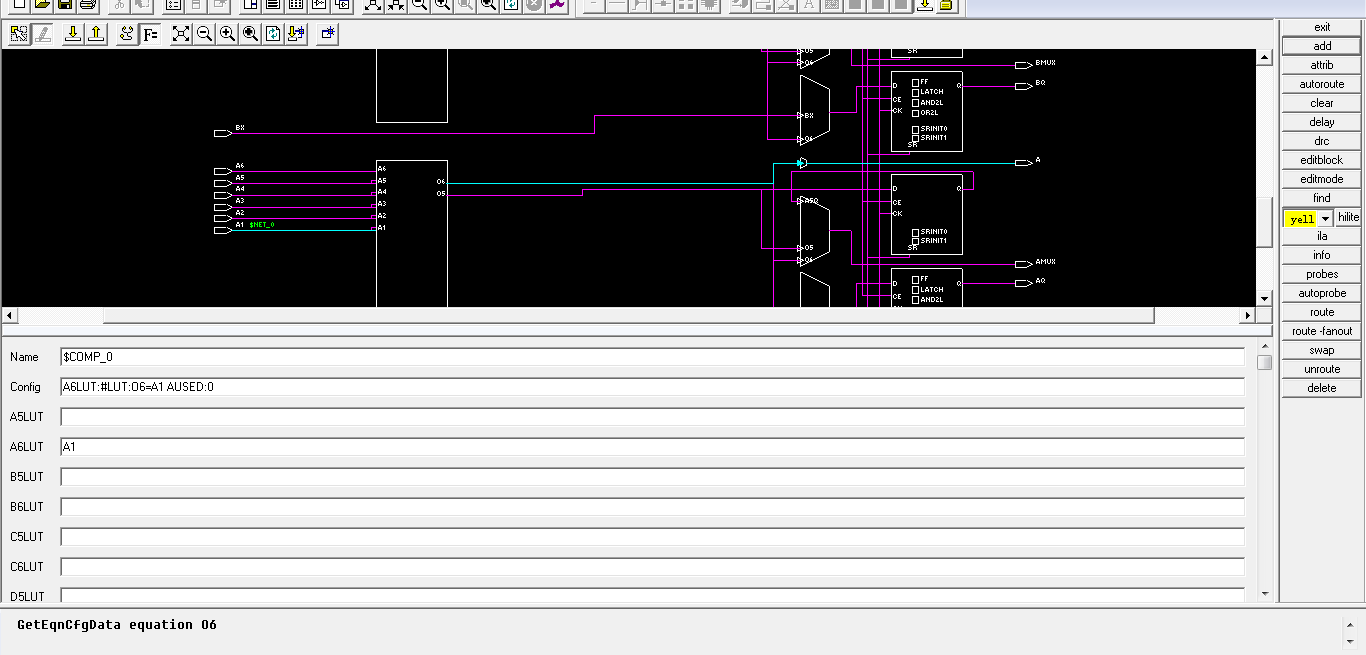

单击确定,就增加了一个 component ,名称 为 $COMP_0。双击 这个 component,可以看到 这个 slice 里有 四个 LUT 可以使用。

在这里 我选择 使用 A1~A6 对应的 LUT,在 命令行 窗口 输入 如下 命令行:

select pin "SLICE_X29Y22.CQ"

select pin "SLICE_X29Y21.A1" (在输入这条命令时,按住Ctrl 键)

点击 最右侧的 add。

然后 双击 这个新增的 component $COMP_0后 可以看到 一个 $NET_0 信号 连到了 A1上。

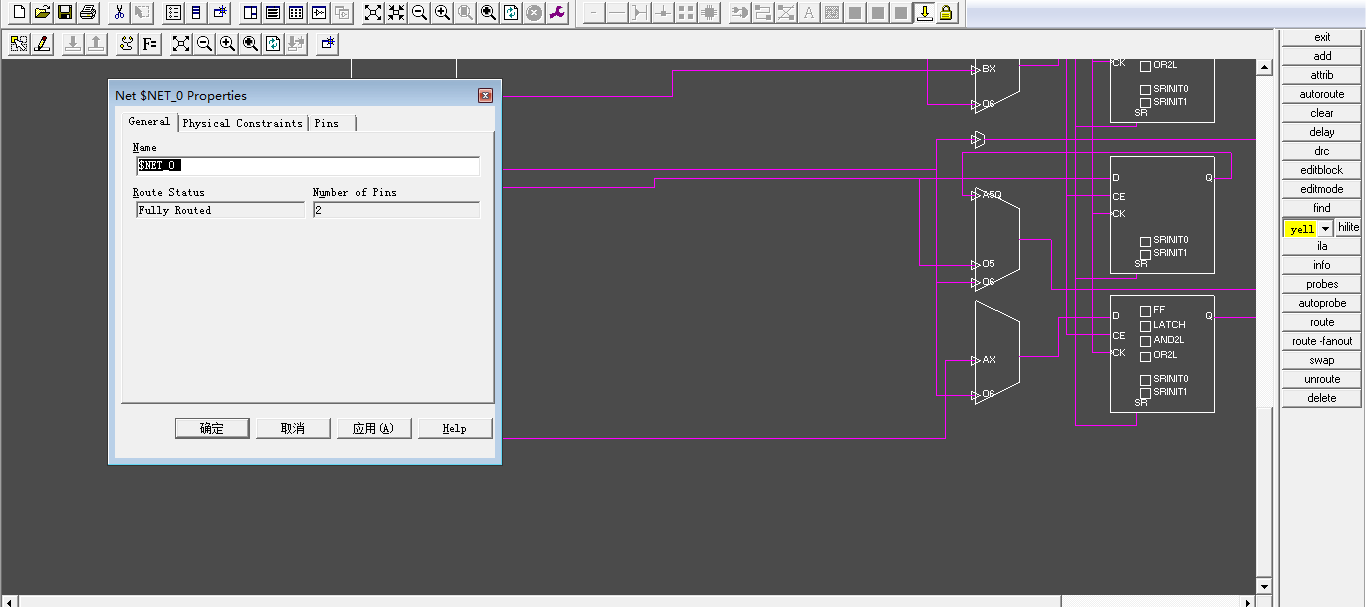

将 打开的 窗口 改成 可修改模式,单击F= ,修改 这个slice的 内部电路。先在 A6LUT上 填入 A1(因为 新增加 的 net 连到了 A1 上,在A6LUT中输入是因为 要从 O6 输出),,然后 点击 apply ,使得前面的修改变成 电路。如下图所示:

然后 可以看到 这个 $NET_0 连到了 输出 端 A上。

最后 再将 component $COMP_0 的 A Pin,连到 之前的 PAD U16的 O 端。使用 同样的 方法。

select pin "SLICE_X29Y21.A"

select pin "U16.O" (在输入这条命令时,按住Ctrl 键)

点击 最右侧的 add。

这里 新增加了一个 $NET_3 的 net,连到了 PAD U16上。

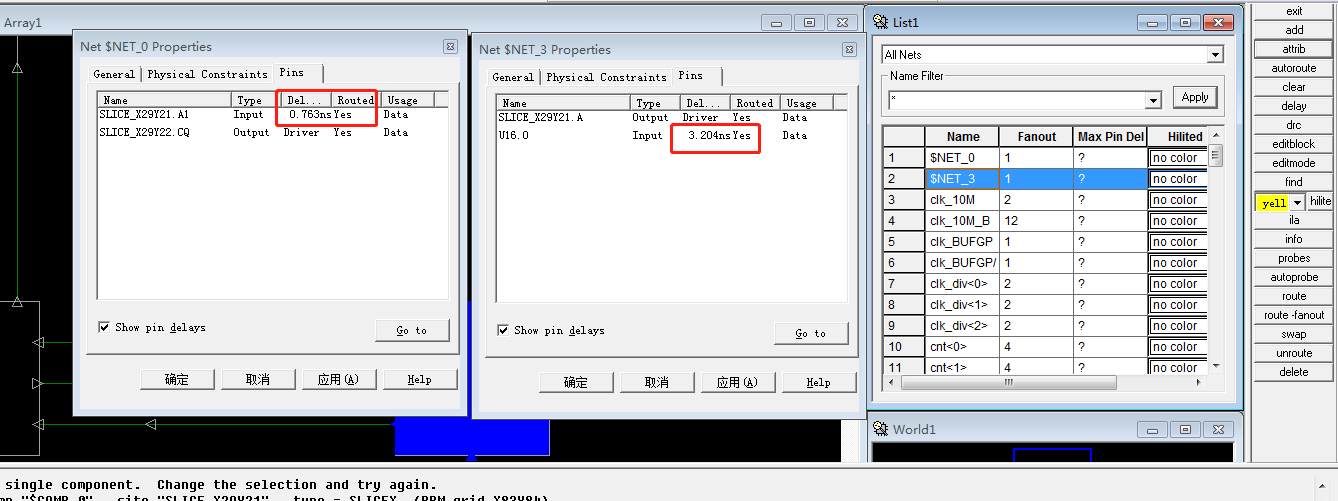

通过 查看 $NET_0 和 $NET_3 的 attrib, 可以看到 这两段的 时间分别是 0.763ns 和 3.204ns。

而在 修改之前 从 SLICE_X29Y22 的 CQ Pin 到 PAD U16的 O端的 延时 为 0.174 ns + 3.199ns ,所以 修改后 延时 增加了 0.594ns。这只是演示,想要 延迟 跟多的 时间,可以 选择 更远的 空闲slice。

当上述完成,并得到理想的 延时后,就可以 生成 .bit file,用于FPGA平台验证。

点击Tools,选择Run Bitgen,选择生成的 .bit file 放置位置,点击 OK ,即可生成 .bit file。