本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

4.3 提取所得寄生参数的表示方法

从布局(layout)中提取的寄生参数可以用三种格式描述:

- 详尽的寄生参数格式 :Detailed Standard Parasitic Format(DSPF)

- 精简的寄生参数格式 :Reduced Standard Parasitic Format(RSPF)

- 标准的寄生参数格式 :Standard Parasitic Extraction Format(SPEF)

一些工具还提供了专用的寄生参数二进制表示格式,例如SBPF;这有助于减小文件存储空间,并加快了工具读取寄生参数的速度。下面分别对以上三种格式进行简要说明。

4.3.1 详尽的寄生参数格式

使用DSPF格式时,详尽的寄生参数以SPICE格式表示。SPICE中的Comment语句用于表明单元类型、单元引脚及其电容。电阻和电容值采用标准SPICE语法,并且单元实例也包含在此表示格式中。这种格式的优势在于,DSPF文件可以用作SPICE仿真器本身的输入。但是,缺点是DSPF语法过于详细和冗长,导致模块的总文件大小非常大。因此,这种格式在实际中仅用于相对较小的一组网络。

以下是DSPF文件的示例,描述了从主输入IN到缓冲器BUF的输入引脚A以及从BUF的输出引脚OUT到主输出引脚OUT的一个网络互连。

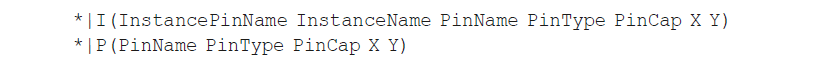

DSPF中的非标准SPICE语句是以 * |开头,并具有以下格式:

4.3.2 精简的寄生参数格式

使用RSPF格式时,寄生参数以精简的形式表示。精简格式包括电压源和受控电流源。RSPF格式也是SPICE文件,也可以将其读取到类似SPICE的仿真器中。RSPF格式要求简化详细的寄生参数并将其映射为精简格式,因此这是RSPF格式的一个缺点,因为寄生提取过程的重点通常是提取的精度,而不是压缩成RSPF之类的精简格式。RSPF格式的另一个限制是不能以这种格式表示双向信号流。

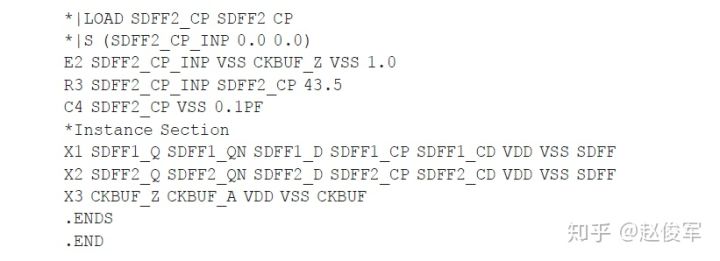

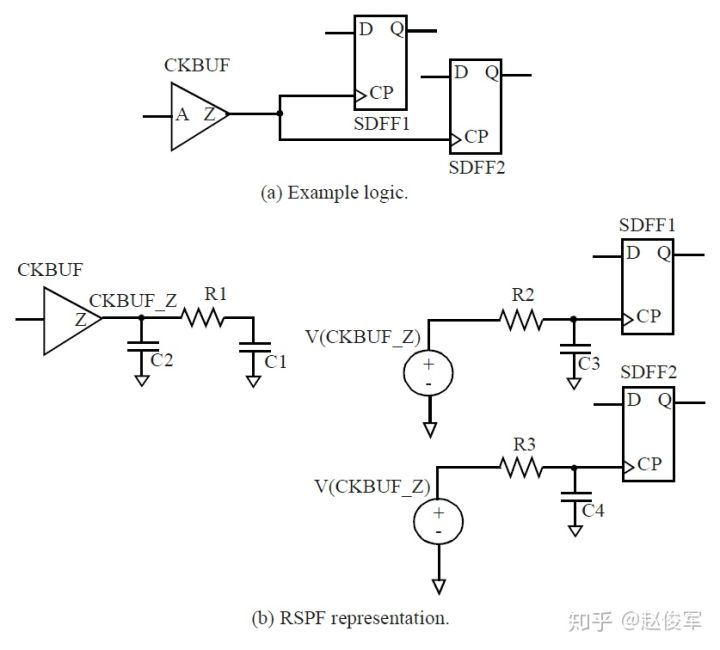

以下是RSPF文件的示例,原始设计和等效表示如图4-13所示。

这个文件具有以下特点:

- 在每个扇出单元的输入引脚上都使用0.1pF的电容(C3和C4)和电阻(R2和R3)对引脚到引脚(pin-to-pin)的互连延迟进行建模,电阻值的选取原则是使RC延迟对应于引脚到引脚的互连延迟。驱动单元输出引脚上的π型负载模拟了通过该单元的延迟。

- 输入端的RC元件由理想电压源(E1和E2)驱动,该电压源等于驱动单元输出端的电压。

4.3.3 标准的寄生参数格式

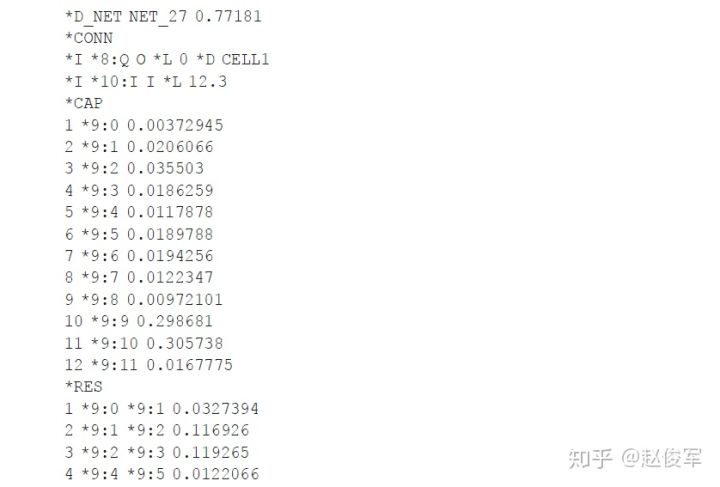

SPEF是一种紧凑格式,可以表示详细的寄生参数。下面是一个具有两个扇出的网络的示例:

寄生电阻和电容的单位在SPEF文件的开头中指定,附录C中提供了SPEF文件的更详细说明。由于SPEF的紧凑性和表示的完整性,它是设计中寄生参数表示方法的首选格式。

4.4 耦合电容的表示方法

上一节说明了将一个网络的电容表示为接地(grounded)电容的情况。由于纳米技术中的大多数电容是侧壁(sidewall)电容,因此这些电容的恰当表示形式应该是信号到信号(signal-to-signal)的耦合电容(Coupling Capacitance)。

DSPF中耦合电容的表示是对原始DSPF标准的附加(add-on),因此不是唯一的。耦合电容会在两组耦合网络之间被复制,这意味着由于两组网络中有重复的耦合电容,因此DSPF无法直接被读入SPICE。一些输出DSPF的工具通过在两个耦合网络中各包含一半的耦合电容解决了这一问题。

RSPF是精简的格式,因此不适合表示耦合电容。

SPEF标准以统一和明确的方式处理耦合电容,因此是考虑串扰(crosstalk)时序时优先选择的提取格式。此外,就文件大小而言,SPEF是紧凑的表示格式,适合用于表示带耦合或不带耦合的寄生参数。

如附录C中所描述,管理文件大小的机制之一是在文件的开头列出名称目录(name directory)。现在,许多提取工具在SPEF文件的开头指定了网络名目录(将网络名表示为索引),从而避免了重复网络名的冗长性,这样可以大大减小文件大小。附录C中列举了一个SPEF的名称目录示例。

4.5 分层方法

大型复杂的设计通常在物理设计过程中需要使用分层方法(hierarchical methodology)来进行寄生参数提取和时序验证。在这种情况下,模块的寄生参数会在模块级别提取,然后可以在更高的层次上使用。

可以将从一个模块的布局中提取得到的寄生参数用于尚未完成布局的另一个模块的时序验证。在这种情况下,通常将已布局完的模块的寄生参数与预布局模块的基于线负载模型的估计寄生参数结合使用。

在使用分层方法的流程中,顶层(top)模块的布局最先完成,但其中的模块仍为黑匣子(预布局),基于线负载模型估计所得的寄生参数可以结合从布局完成的顶层中提取得到的寄生参数用于较低层次的模块。 一旦各模块的布局也完成了,就可以将从顶部和模块的布局中提取得到的寄生参数结合在一起。

布局中的重复模块

如果将一个设计模块在布局中复制多次,则可以将从一个实例(instantiation)中提取的寄生参数用于所有实例,这就要求该模块的布局在各方面对于每个实例都是相同的。例如,从布局内的布线网络看,布局环境(environment)应该没有差异,这意味着模块内网络不与模块外部的任何网络电容耦合。可以做到这一点的一种方法是:确保没有在模块内布线任何顶层的网络,并且对在块的边界附近布线的网络有足够的保护或间距。

4.6 减少关键网络的寄生参数

本节简要概述了管理寄生参数对关键(critical)网络影响的常用技术。

降低互连电阻

对于关键网络,重要的是要保持较低的压摆率(slew)或快速的过渡时间(transition),这意味着应降低互连电阻。通常,有两种方法可以实现较低的电阻:

- 宽走线(Wide trace):具有比最小宽度更加宽的走线可以降低互连电阻,而且不会引起寄生电容的显著增加。因此,可以减少总的RC互连延迟和过渡时间。

- 在较高(较厚)金属中布线:较高的金属层通常具有低电阻率,可用于给关键信号布线。较低的互连电阻可减少互连延迟以及目标引脚(destination pin)上的过渡时间。

增加走线间距

增加走线之间的间距可以减少网络的耦合电容和总电容。大的耦合电容会增加串扰,避免串扰是在长距离相邻走线中布线的网络的重要考虑因素。

相关网络的寄生参数

在许多情况下,一组网络必须在时序上匹配。比如高速DDR接口的一个字节通道内的数据信号,因为需要保证一个字节通道内的所有信号都具有相同的寄生参数,所以这些信号都应在同一金属层中布线。例如,虽然金属层M2和M3具有相同的平均值和相同的统计变化,但是这些变化是独立的,从而这两个金属层中的寄生参数变化是无关的。因此,如果对于关键信号的时序匹配很重要,则在每个金属层中的布线必须相同。