视频版:

https://www.bilibili.com/video/av839767912

课程前准备

建议准备仿真软件,熟悉VCS的同学可以直接使用VCS,不熟悉的同学建议直接再win平台的Questa就行了。

使用Questa前期不用打开GUI,不需要看波形,questa的图形界面还是有点卡的。

首先来看第一节课的代码

module lab1 ();

import uvm_pkg::*;

`include "uvm_macros.svh"

initial begin

`uvm_info("lab1.1","hello uvm!",UVM_NONE)

end

endmodule

从头开始看,只要使用了UVM,就必须写开头的两行。import语句导入UVM的包,而include语句则包含了一系列宏定义。由于SV的局限性,不得不借用宏的形式实现一些功能。总之,就像JAVA八股文一样,UVM的基本书写也是一样的八股,但是这只是指代码基本框架的八股,验证背后的内容依然要与业务紧密结合。

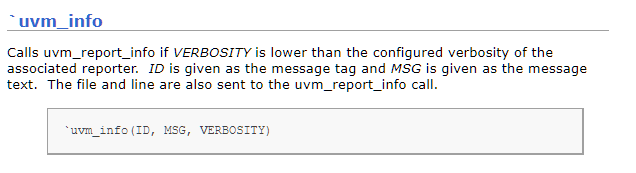

我们遇到的第一个宏就是uvm_info,用于打印信息

uvm_info使用时需要传递三个参数,分别是ID, MSG, VERBOSITY。ID表示是谁发出的信息,MSG就是发出的内容,而最后的VERBOSITY则是冗余度,当冗余度小于阈值时,消息才会被打印出来。

我们可以到UVM学院的一个网站中去查找相关内容:https://verificationacademy.com/verification-methodology-reference/uvm/docs_1.2/html/

有兴趣的同学可以去自己查阅源码,看看uvm_info宏背后都做了哪些工作。

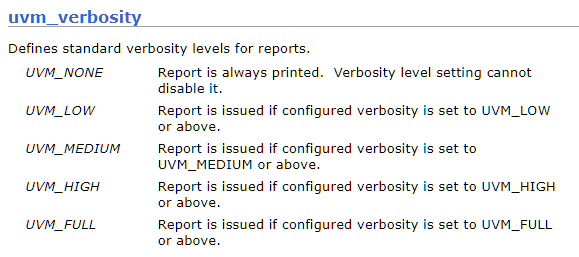

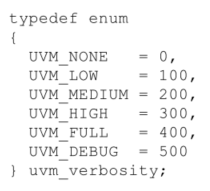

冗余度是一个枚举型变量,默认的等级包括

也可以直接使用具体数值。

接下来是makefile

TESTNAME ?= lab2

all: work tb sim

work:

vlib work

tb:

vlog -f filelist.f

sim:

vsim lab1 -do "run -all;exit" -c -l $(TESTNAME).log -voptargs=+acc

clean:

rm -r work

rm *.log transcript vsim.* *.ucdb

vlib建立工作库

vlog进行文件编译

vsim进行仿真,-do 选项执行后面双引号内部的命令,也可以将命令写入一个do文件中,do文件使用tcl语言编写,有兴趣的同学可以去了解。run -all仿真时直接一直仿真,exit代表仿真结束后退出仿真器,不加exit会停在仿真命令行。-c选项让仿真器不要打开GUI界面,-l选项让仿真信息全部输入到指定文件中,而最后的-voptargs=+acc是仿真器的优化选项。VCS等其他仿真器也会有类似的选项,可以自行了解。

直接make all即可执行,下面是编译

QuestaSim-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

Start time: 22:06:57 on Apr 27,2021

vlog -f filelist.f -l comp.log

-- Compiling module lab1

-- Importing package mtiUvm.uvm_pkg (uvm-1.1d Built-in)

** Note: (vlog-2286) ./lab1.sv(3): Using implicit +incdir+E:/questasim64_10.6c/uvm-1.1d/../verilog_src/uvm-1.1d/src from import uvm_pkg

Top level modules:

lab1

End time: 22:06:58 on Apr 27,2021, Elapsed time: 0:00:01

Errors: 0, Warnings: 0

接下来是执行仿真

# vsim lab1 -do "run -all;exit" -c -l lab2.log -voptargs="+acc"

# Start time: 22:06:59 on Apr 27,2021

# ** Note: (vsim-3812) Design is being optimized...

# // Questa Sim-64

# // Version 10.6c win64 Jul 26 2017

# //

# // Copyright 1991-2017 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading mtiUvm.uvm_pkg

# Loading work.lab1(fast)

# Loading mtiUvm.questa_uvm_pkg(fast)

# Loading E:/questasim64_10.6c/uvm-1.1dwin64uvm_dpi.dll

# run -all

# ----------------------------------------------------------------

# UVM-1.1d

# (C) 2007-2013 Mentor Graphics Corporation

# (C) 2007-2013 Cadence Design Systems, Inc.

# (C) 2006-2013 Synopsys, Inc.

# (C) 2011-2013 Cypress Semiconductor Corp.

# ----------------------------------------------------------------

#

# *********** IMPORTANT RELEASE NOTES ************

#

# You are using a version of the UVM library that has been compiled

# with `UVM_NO_DEPRECATED undefined.

# See http://www.eda.org/svdb/view.php?id=3313 for more details.

#

# You are using a version of the UVM library that has been compiled

# with `UVM_OBJECT_MUST_HAVE_CONSTRUCTOR undefined.

# See http://www.eda.org/svdb/view.php?id=3770 for more details.

#

# (Specify +UVM_NO_RELNOTES to turn off this notice)

#

# UVM_INFO verilog_src/questa_uvm_pkg-1.2/src/questa_uvm_pkg.sv(215) @ 0: reporter [Questa UVM] QUESTA_UVM-1.2.3

# UVM_INFO verilog_src/questa_uvm_pkg-1.2/src/questa_uvm_pkg.sv(217) @ 0: reporter [Questa UVM] questa_uvm::init(+struct)

# UVM_INFO ./lab1.sv(6) @ 0: reporter [lab1.1] hello uvm!

# exit

# End time: 22:07:02 on Apr 27,2021, Elapsed time: 0:00:03

# Errors: 0, Warnings: 0

可以看到打印了信息# UVM_INFO ./lab1.sv(6) @ 0: reporter [lab1.1] hello uvm!

软件:Questasim、gitbash

推荐使用gitbash,使用makefile之前要安装makefile,教程在这里->https://www.eemaker.com/git-bash-make.html

本节代码下载链接:

链接:https://pan.baidu.com/s/1GBhvpGaoG_BNvRZqh-4kPA

提取码:4rcr